Master's Thesis

Benjamin Spragg Sørensen PED4-1045, 06-2025

Copyright © Aalborg University 2025 Software programs utilized in the report.

1. LTSpice

- 2. Altium

- 3. Xilinx Vivado

#### **Department of Energy Technology**

Aalborg University http://www.aau.dk

#### **AALBORG UNIVERSITY**

STUDENT REPORT

Title:

Experimental Test of 3.6 kW Totem-Pole Converter Using State of the Art SiC MOS-FETs

Theme:

Master's Thesis

**Project Period:**

10th Semester 2025

**Project Group:**

PED4-1045

Participant(s):

Benjamin Spragg Sørensen

**Supervisor(s):**

Stig Munk-Nielsen

**Copies:** Unlimited

Page Numbers: 78

**Date of Completion:**

June 20, 2025

#### **Synopsis:**

Dette projekt undersøger effektivitetsforbedringen for en eksisterende konverter fra en svejsemaskine udviklet af Migatronic. Effektiviteten forbedres ved at bygge en totempæl-konfiguration kombineret med SiC MOSFET'er. Konverteren er blevet designet, simuleret og eksperimentelt valideret for at vurdere dens ydeevne og effektivitet. For at opfylde Migatronics designkrav er der udført en analyse af komponenttab, konverterkonfiguration og transistorvalg.

#### **Abstract**

This project explores the efficiency improvement for an existing converter from a wielding machine developed by Migatronic. The efficiency is improved by building a Totem-pole configuration combined with SiC MOSFETs.

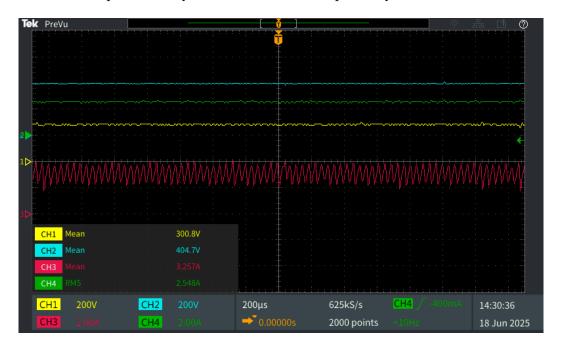

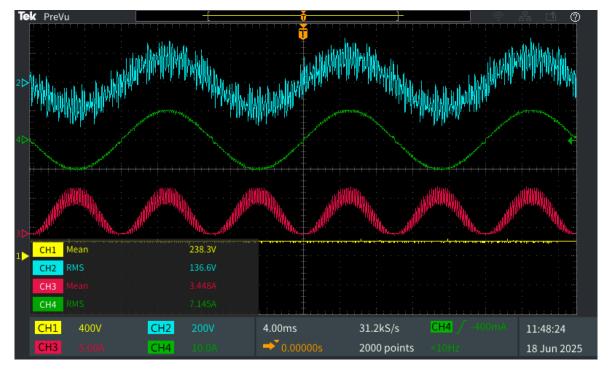

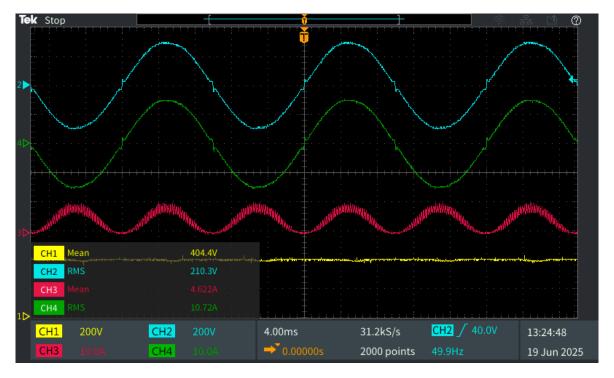

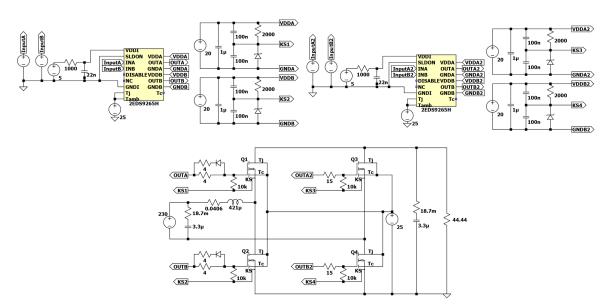

The converter has been designed, simulated, and experimentally validated to assess its performance and efficiency. In order to meet Migatronic's design requirements, an analysis of component losses, converter configuration, and transistor selection has been conducted. Two control systems have been developed on an FPGA development board. The first control system controls the converter in a DC-DC configuration which operates at 100 kHz with a dead-time implemented. Another control system controls the converter in an inverter configuration with the goal of generating a 50 Hz fundamental sine-wave duty cycle with a 100 kHz switching frequency and dead-time implemented. Both controllers are tested in a laboratory setting and have proven performance. In the project, SiC MOS-FET C3M0045065K is chosen for the HF leg and C3M0025065K is chosen for the LF leg. A simulation model has been made that estimates the converter's performance. A series of simulations are then conducted. When testing the converter in a DC-DC configuration, the converter is able to boost the voltage to 397 V. The output voltage ripple is measured as  $\pm$  5.85 V and the inductor current ripple is measured to 2.34 A. When testing the converter in inverter configuration, the output voltage and current are a sinusoidal waveform operating at 228.9 V rms and 15.48 A rms with a fundamental frequency of 50 Hz. The simulated efficiency reaches 98.9 %.

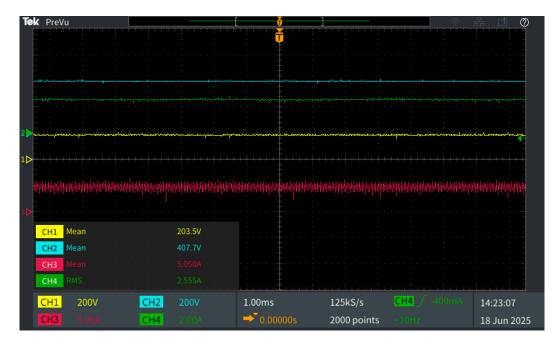

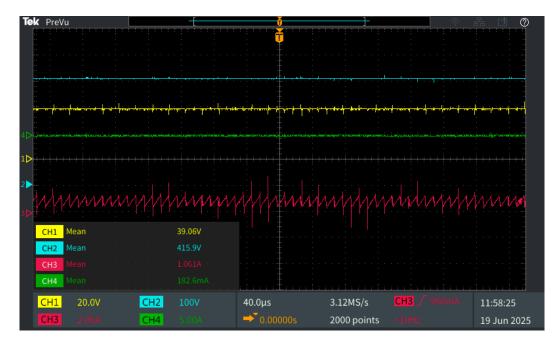

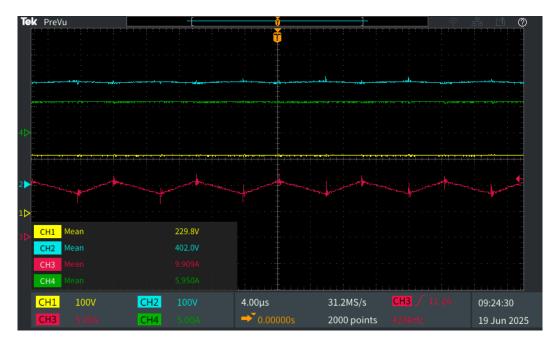

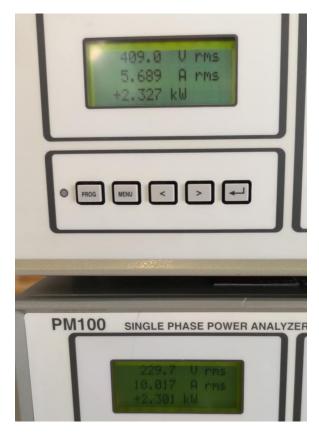

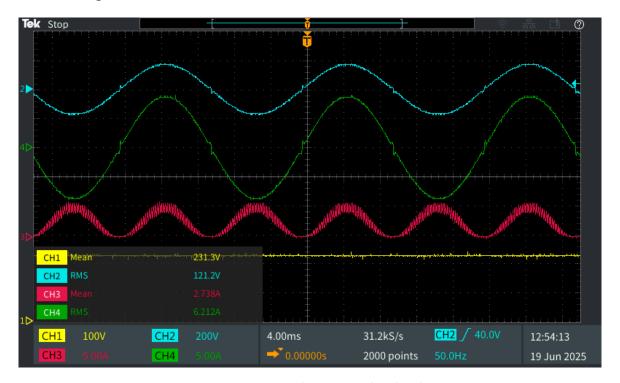

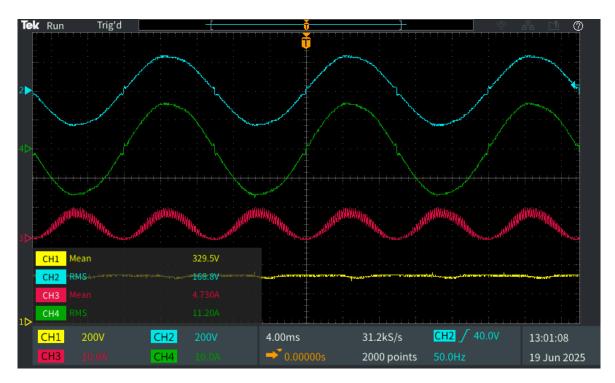

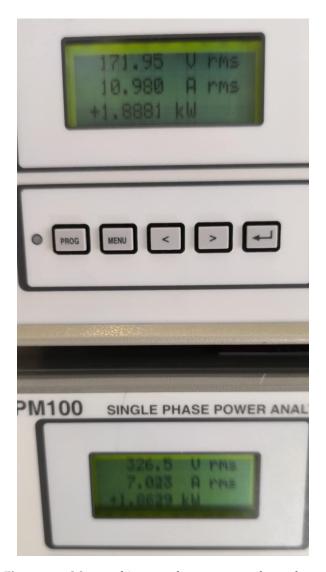

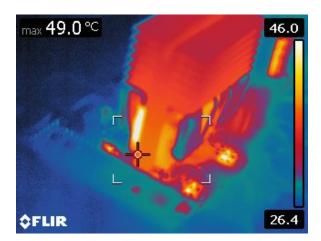

The converter has been experimentally validated with a 2-layer PCB. The converter has been tested in a DC-DC configuration. with a switching frequency of 100 kHz. The voltage boosting capability has been tested with various duty cycles. It is shown that the converter is capable of converting different voltage ranges from 39 V up to 415 V. The efficiency is estimated to be 99.1 % at 2.3 kW and estimated efficiency is 99.3% at 3.6 kW. The converter is then tested with an inverter configuration. A 3.3  $\mu$ F capacitor is added to remove the voltage ripple. The inverter worked correctly and is capable of turning a 329 V DC signal into a 168 V rms sine wave. The estimated efficiency is 98.9 % at 1860 W.

Table 1: Nomenclature of symbols throughout the report.

| Nomenclature          |                                             |  |  |

|-----------------------|---------------------------------------------|--|--|

| Symbol                | Symbol Description                          |  |  |

| $f_s$                 | Switching Frequency                         |  |  |

| $f_c$                 | Clock Frequency                             |  |  |

| C                     | Capacitance                                 |  |  |

| $C_{par}$             | Parasitic Capacitance                       |  |  |

| Ĺ                     | Inductance                                  |  |  |

| $L_{par}$             | Parasitic Inductance                        |  |  |

| η                     | Efficiency                                  |  |  |

| $t_r$                 | Rise Time                                   |  |  |

| $t_f$                 | Fall Time                                   |  |  |

| $R_{on}$              | On Resistance                               |  |  |

| $R_L$                 | Load Resistor                               |  |  |

| $I_{ac}$              | AC Current                                  |  |  |

| $I_{dc}$              | DC Current                                  |  |  |

| $I_L$                 | Inductor Current                            |  |  |

| $V_{ac}$              | AC Voltage                                  |  |  |

| $V_{dc}$              | DC Voltage                                  |  |  |

| $V_s$                 | Input Voltage                               |  |  |

| $V_f$                 | Forward Voltage                             |  |  |

| $V_{peak}$            | Peak Voltage                                |  |  |

| $V_o$                 | Output Voltage                              |  |  |

| $V_g$                 | Gate Voltage                                |  |  |

| $V_C$                 | Capacitor Ripple Voltage                    |  |  |

| $V_{rms}$             | Root-Mean-Square Voltage                    |  |  |

| $P_o$                 | Output Power                                |  |  |

| $P_{Diode}$           | Diode Power Loss                            |  |  |

| $P_L$                 | Inductor Power Loss                         |  |  |

| $P_{con}$             | Conduction Loss                             |  |  |

| $P_{sw}$              | Switching Loss                              |  |  |

| $P_{Cap}$             | Capacitor Power Loss                        |  |  |

| $D_Q$                 | Duty Cycle                                  |  |  |

| T                     | Period/Temperature                          |  |  |

| $k_d$                 | Dead Time Ratio                             |  |  |

| $Q_{rr}$              | · · · · · ·                                 |  |  |

| $C_S$                 | Ratio between clock and switching frequency |  |  |

| N                     |                                             |  |  |

| $\zeta$ Damping ratio |                                             |  |  |

**Table 2:** Nomenclature of abbreviations throughout the report.

| Nomenclature                                                      |                                                   |  |  |

|-------------------------------------------------------------------|---------------------------------------------------|--|--|

| Abbreviation Description                                          |                                                   |  |  |

| MIG                                                               | Metal Inert Gas                                   |  |  |

| TIG Titanium Inert Gas                                            |                                                   |  |  |

| MOSFET                                                            | Metal-Oxide-Semiconductor Field-Effect Transistor |  |  |

| Si                                                                | Silicon                                           |  |  |

| SiC                                                               | Silicon Carbide                                   |  |  |

| GaN                                                               | Gallium Nitride                                   |  |  |

| GaNFET                                                            | Gallium Nitride Field-Effect Transistors          |  |  |

| PFC                                                               | Power Factor Correction                           |  |  |

| LF                                                                | Low Frequency                                     |  |  |

| HF                                                                | High Frequency                                    |  |  |

| CrCM                                                              | Critical Conduction Mode                          |  |  |

| EMI Electromagnetic Interference                                  |                                                   |  |  |

| PCB Printed Circuit Board                                         |                                                   |  |  |

| FPGA Field-Programmable Gate Array                                |                                                   |  |  |

| VHDL Very High Speed Integrated Circuit Hardware Description Lang |                                                   |  |  |

| DCR DC Resistance                                                 |                                                   |  |  |

| ESR Equivalent Series Resistance                                  |                                                   |  |  |

| Q <sub>rr</sub> Reverse Recovery Charge                           |                                                   |  |  |

| CrCM Critical Conduction Mode                                     |                                                   |  |  |

| CCM Continuous Conduction Mode                                    |                                                   |  |  |

| PWM Pulse Width Modulation                                        |                                                   |  |  |

| LF Low Frequency                                                  |                                                   |  |  |

| HF                                                                | High Frequency                                    |  |  |

| LUT                                                               | Lookup Table                                      |  |  |

| LFM                                                               | Linear Feet per Minute                            |  |  |

## **Preface**

Aalborg University, June 20, 2025

This master thesis is written by Benjamin Spragg Sørensen studying at Aalborg University. Simulations on circuit design are done in LTSpice and for the results analysis MATLAB has been used. The illustrations are made in Lucidchart and Microsoft PowerPoint.

The prerequisites for reading the report are a certain knowledge of mathematics, physics, circuit analysis theory, power electronics, semiconductor technologies.

The author would like to thank the supervisor Stig Munk-Nielsen and Tamás Kerekes for instructive guidance as well as constructive criticism. Thanks to Walter Neumayr for helping with the laboratory experiments. Thanks to my parents and girlfriend for their support throughout the project period.

Benjamin Sørensen

Benjamin Spragg Sørensen bss18@student.aau.dk

# Contents

| 1 | Intr | Introduction                                                  |          |  |

|---|------|---------------------------------------------------------------|----------|--|

|   | 1.1  | Converter-based Welding Machine                               | 4        |  |

|   |      | 1.1.1 PFC rectifier                                           | 4        |  |

|   |      | 1.1.2 Frequency inverter                                      | 6        |  |

|   |      | 1.1.3 High frequency transformer                              | 8        |  |

|   |      | 1.1.4 Improving efficiency in modern welding equipment        | ç        |  |

|   |      |                                                               |          |  |

| 2 | Eva  | luation of Migatronic's Converter and Proposed Improvements   | 10       |  |

|   |      | 2.0.1 Migatronic Design Requirements                          | 10       |  |

|   | 2.1  | Estimation of Converter Component Loss                        | 11       |  |

|   | 2.2  | Converter Configuration & Transistor choice                   | 13       |  |

|   | 2.3  | Project Scope                                                 | 16       |  |

|   | 2.4  | Problem Statement                                             | 16       |  |

|   |      |                                                               |          |  |

| 3 |      | trol Strategy of Converter                                    | 17       |  |

|   | 3.1  | Selection of Hardware Implementation Platform                 | 17       |  |

|   | 3.2  | Rationale for testing in DC-DC and Inverter Configuration     | 17       |  |

|   | 3.3  | DC-DC Control Operating Principle                             | 17       |  |

|   |      | 3.3.1 Duty cycle derivation of DC control structure           | 18       |  |

|   |      | 3.3.2 Implementation of DC control system                     | 19       |  |

|   | 3.4  | Inverter Control Operating Principle                          | 22       |  |

|   |      |                                                               | 23       |  |

|   |      | 3.4.2 Implementation of inverter control system               | 23       |  |

| 4 | Ром  | ver Stage, Gate Driver Design and Passive Component Selection | 31       |  |

| • | 4.1  | Selection of SiC MOSFETs                                      | 31       |  |

| 4 | 4.2  | Gate Driver Choice and Driver Circuit                         |          |  |

|   | 4.3  | Passive Component Dimensioning                                |          |  |

|   | 4.5  | 4.3.1 Selection of Capacitor and Inductor                     |          |  |

|   |      | 4.5.1 Selection of Capacitor and inductor                     | رن       |  |

| 5 | Sim  | ulation-Based Verification of Converter and Thermal Design    | 41       |  |

|   | 5.1  | Simulation of Converter in DC-DC Configuration                | 41       |  |

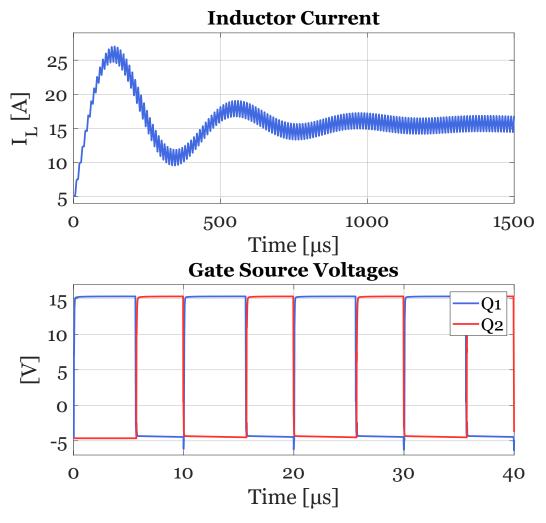

|   | 5.2  | Simulation of Converter in Inverter Configuration             | 44       |  |

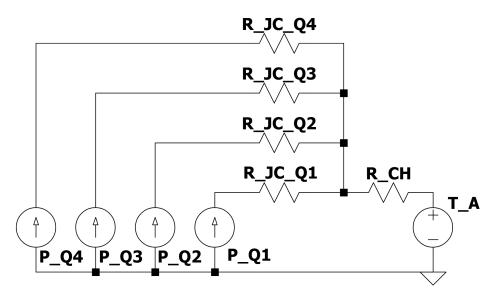

|   | 5.3  | Thermal Design                                                | 46       |  |

| 6 | PCF  | B Design and Experimental Results                             | 49       |  |

| U | 6.1  | PCB Layout                                                    | 49       |  |

|   | 6.2  | Test of Converter in DC-DC Configuration                      | 50       |  |

|   | 0.2  |                                                               | 50       |  |

|   |      | 6.2.1 DC-DC gate driver signals                               |          |  |

|   |      | 0 -                                                           | 52<br>52 |  |

|   |      | 6.2.3 Voltage boosting capability                             | 56       |  |

|   |      | 6.2.4 Power analysis and efficiency at 230 V input            | 58       |  |

|   |      | 6.2.5 Power Analysis and Efficiency at 360 V input            | 62       |  |

|   | 6.3  | Inverter Configuration                                        | 64       |  |

|   |      | 6.3.1 Inverter gate driver signals                            | 64       |  |

Contents 1

|    | 6.3.2       | Initial test of converter operating in inverter configuration | 66 |

|----|-------------|---------------------------------------------------------------|----|

|    | 6.3.3       | Power analysis Analysis and Efficiency at 330 V input         | 67 |

|    | 6.3.4       | 400 V input voltage test                                      | 71 |

| 7  | Discussion  |                                                               | 72 |

| 8  | Conclusion  | ı                                                             | 73 |

| 9  | Further Inv | restigation                                                   | 76 |

| Bi | bliography  |                                                               | 77 |

| A  | Appendix 1  | I                                                             | 78 |

## Introduction

Welding is the process of joining materials together; this usually consists of metals that are fused together using a combination of heat, pressure and a filler material. Up until the end of the 19th century, the only welding method was forge welding, which was predominantly carried out by blacksmiths[1]. This method fused two metals together by heating them up and then hammering the metals together. At the end of the century new methods were developed, such as gas welding, resistance welding and arc welding. These methods quickly became the standard during the 20th century as the demand for faster, cheaper and more reliable ways of joining metals increased.

Gas welding relies on the use of a gas flame as the heat source to melt and join metals. A filler material is typically used to facilitate the fusion process. This method is highly versatile, as it can be applied to a wide range of metal types[1]. However, gas welding will not be discussed further.

Resistance welding and arc welding utilize electrical energy to heat metals. In resistance welding, two metal pieces are clamped together under pressure and exposed to electrical current. The heat generated by the current flowing through the resistive metals causes them to melt at the junction. As the metals cool, they fuse to form a weld. This method is primarily used for joining thin metal plates and does not require any filler material[1].

Arc welding creates an electrical arc between an electrode and the metal surface. The arc generates intense heat that melts the metals, allowing them to fuse. Unlike resistance welding, arc welding uses a filler material that serves as a medium to aid in the fusion process. There are several arc welding techniques, such as stick welding, metal inert gas (MIG), and titanium inert gas (TIG) techniques. Each method offers different advantages depending on the application[1].

An important factor in both resistance and arc welding is the ability to generate high currents, as this is essential to generate sufficient heat for the metals to melt. These currents can typically vary between 50-500 amperes. To generate such currents, it is necessary to reduce the high voltage of the mains supply[1].

Throughout most of the 20th century, welding machines relied on large transformers connected directly to the mains power supply. These high-power transformers operated at the standard 50 Hz frequency and as such required a large core to prevent magnetic saturation. As a result, welding machines were bulky, often weighing several hundred kilograms. They also had poor efficiency and were expensive to buy and operate[5]. By the late 20th century a new generation of welding machine based on converter technology emerged. This new approach replaced the large transformer with converters, consisting of a front end rectifier coupled together with an inverter. The rectifier converted the mains AC signal to DC, which the inverter then converted to a high frequency AC voltage signal in the kilohertz range. The high frequency AC signal allowed for the use of a much smaller transformer as the required core size decreases with increasing frequency[5].

The shift to converter-based technology brought many significant improvements to welding machines. A depiction of two Migatronic welding machines is presented. This consists of an older MTE model from the 1990s and a modern CenTIG model. Both models are TIG type welding machines. Figure 1.1 shows the illustrations of both machines.

(a) Transformer Based MTE Model[15]

(b) Inverter Based CenTig Model [14]

Figure 1.1: Welding machine technology types

Figure 1.1 (a) shows the older MTE welding machine, which operates on a transformer-based design. This machine has a limited duty cycle, which means it can only operate for a portion of a 10-minute period before requiring a cooldown. It is characterized by its large size, heavy weight, and relatively low efficiency[15]. In contrast, Figure 1.1 (b) shows the modern CenTig welding machine. This model utilizes converter technology, which allows it to operate continuously without cooldown periods. It is significantly smaller, lighter, and more efficient compared to the older transformer-based design[14]. A comparison of the models is shown in Table 1.1.

| Feature         | Older MTE Model                   | Modern CenTig Model         |

|-----------------|-----------------------------------|-----------------------------|

| Welding Current | 220 A                             | 200 A                       |

| Duty Cycle      | 30% (3 minutes on, 7 minutes off) | 100% (continuous operation) |

| Weight          | 135 kg                            | 13.6 kg                     |

| Volume          | $0.225 \text{ m}^3$               | $0.0463 \text{ m}^3$        |

| Efficiency      | 60%                               | 86%                         |

| Technology      | Transformer-based                 | Converter-based             |

Table 1.1: Comparison of older MTE model and modern converter-based welding machine [14][15]

Today, all new welding machines are converter-based, a shift driven not only by technological advancements but also by regulatory requirements. To better understand modern welding machines, it is important to examine the three main circuits that form the core functionality.

## 1.1 Converter-based Welding Machine

Modern welding machines rely on three key circuits to convert mains power into a controlled output suitable for welding: the PFC rectifier, the high-frequency inverter, and the high-frequency transformer. These circuits work together to meet regulatory requirements, improve efficiency, and enable compact and lightweight designs.[5].

#### 1.1.1 PFC rectifier

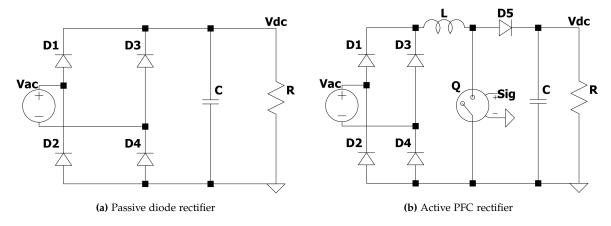

The first circuit is the PFC rectifier, whose primary function is to convert the main AC signal to DC, which can then be used by the inverter. The PFC rectifier has other important functions and is required by law. To understand why this is the case, it is helpful to compare its operation with that of a passive diode bridge rectifier. An illustration of each converter configuration is shown in Figure 1.2.

**Figure 1.2:** Schematic comparison of a passive rectifier with an active PFC rectifier, where R represents the load

In the passive configuration shown in Figure 1.2a, the mains AC supply is connected to a diode full bridge, which converts the AC signal into a DC waveform. A capacitor is connected on the DC side to smooth out the voltage ripple, ensuring stable DC output. The capacitor charges to the maximum voltage of the AC input  $V_{DC} \approx V_{peak} = \sqrt{2} \cdot V_{rms}$  and maintains a DC voltage higher than the AC input voltage for most of the cycle. As a result, current can only flow from the mains during the brief intervals when the AC voltage exceeds the DC voltage. This leads to short, high-amplitude current pulses drawn from the grid as shown in Figure 1.3.

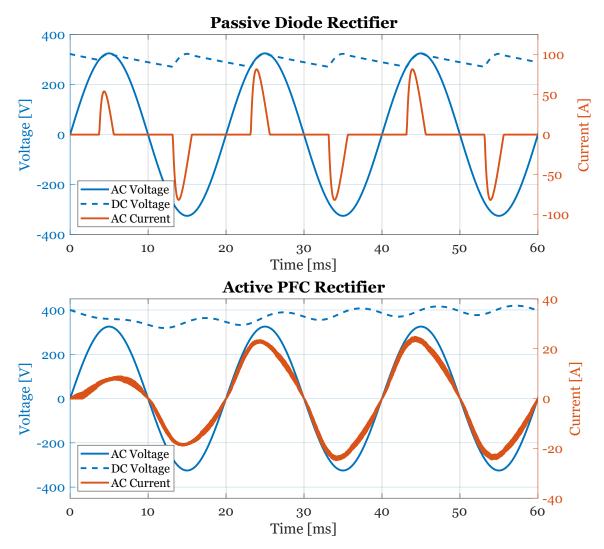

**Figure 1.3:** Comparison of current waveform of a passive diode rectifier against a PFC rectifier, Initial condition of 325 V DC is included to remove inrush current

Since current can only be drawn during short intervals, the current amplitude reaches nearly 80 A to fully charge the capacitor. However, the current that can be drawn from the grid is much lower than that. This limits the DC output power to a fraction of the 3.68 kW that could theoretically be achieved with a sinusoidal current draw.

The PFC configuration shown in Figure 1.2b adds a DC boost stage between the diode bridge and the smoothing capacitor. This allows the current to be controlled by either charging or discharging the inductor depending on the state of the switch. If controlled correctly, the current can be shaped to follow a sinusoidal curve in phase with the AC voltage as shown in Figure 1.3. This means that power is transferred during the whole AC cycle and the capacitor is continuously charged, because of this the peak current is significantly reduced. This in turn allows more power to be supplied. Additionally, the boost stage also allows the DC voltage magnitude to be higher than the peak voltage of the AC voltage. This is also shown in Figure 1.3, where the average DC voltage is 400 V. Furthermore, because the PFC rectifier shapes the current to follow the voltage, it significantly reduces the introduction of higher-order harmonics. This is shown in Figure 1.4 where the AC frequency spectrum of both rectifiers is compared.

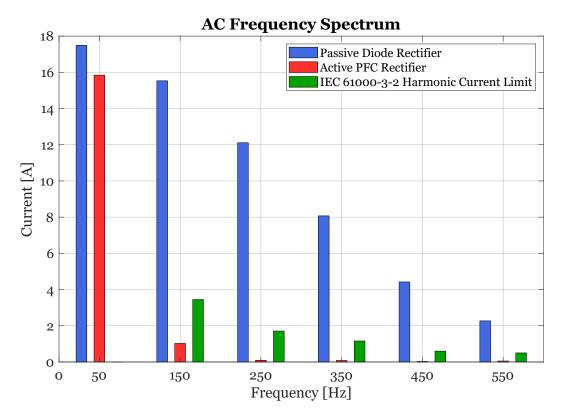

**Figure 1.4:** Comparison of AC frequency spectrum, showing the fundamental and first five harmonics. The diode Rectifier is above the IEC limit whereas the PFC rectifier is below [2].

As shown in Figure 1.4, the AC current from the passive diode rectifier contains significant harmonic content, with multiple high-order frequency components contributing to the total current. Here, the third harmonic alone is nearly equal to that of the fundamental. This distortion is undesirable, as it degrades power quality and negatively affects the power grid. To prevent this, the IEC 61000-3-2 standard sets regulatory requirements for the amplitude of harmonics in welding equipment. As seen, the AC current exceeds the limits for all harmonics shown in Figure 1.4 and it would not be possible to implement this configuration in commercial welding equipment [2]. In contrast, the PFC rectifier generates substantially lower harmonic content, with higher-order harmonics diminishing rapidly beyond the third, becoming nearly negligible. The amplitude of each harmonic is also lower than the IEC 61000-3-2 limit, and it would therefore meet the requirements of the standard[2].

#### 1.1.2 Frequency inverter

The high-frequency inverter is connected to the output of the PFC rectifier. It converts the DC voltage into a high-frequency AC wave, typically in the range of 30 to 50 kHz[5]. Together, the PFC rectifier and inverter effectively function as a frequency drive by increasing the fundamental frequency from the standard 50 Hz to a much higher value. This increase in frequency allows for a significant reduction in transformer size. This is because the reactance of the transformer is given by  $X = 2 \cdot \pi \cdot f \cdot L$ , where f is the frequency and L is the inductance. At higher frequencies, the reactance is dominated by the term f, reducing the influence of the inductance L, which is related to the number of windings and the physical size of the transformer core. As a result, a smaller and lighter transformer can be used without compromising performance. A schematic of the inverter is shown in Figure 1.5.

Figure 1.5: A frequency inverter, converting the DC input to a high frequency AC signal

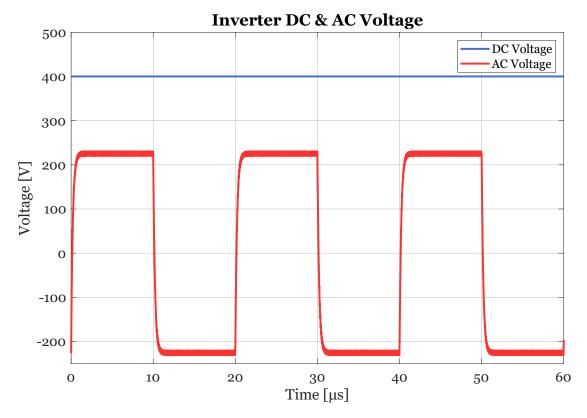

Using the four switches, the inverter can change the DC input into the desired AC waveform, typically this would be a sine or square wave. In addition, the amplitude of the output voltage can be controlled according to the value of the duty cycle. This allows the inverter to control the voltage seen on the transformers output terminals depending on the load conditions and the operator power target. An inverter operating example is shown in Figure 1.6.

Figure 1.6: Inverter operation, converting a DC signal into a 50 kHz AC square wave.

As shown, a 400 V DC signal is converted into a 50 kHz 230 V AC square wave. This signal is applied across the transformer represented by the inductor L and resistor R in Figure 1.7.

#### 1.1.3 High frequency transformer

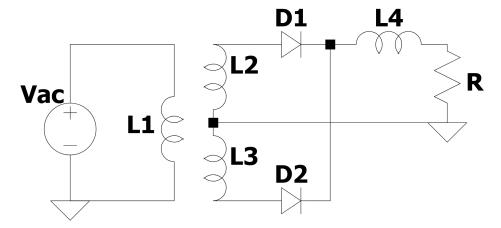

At the back end of the system is a high frequency step-down transformer connected to the output of the inverter. This transformer serves several functions. Primarily, it reduces voltage while increasing current, which is necessary to generate the high heat required to effectively join materials during welding[1]. In addition, the transformer improves the stability of the welding arc by compensating for power fluctuations from the supply, ensuring that voltage spikes at the input are not transmitted to the welding arc. This contributes to a more consistent and controlled welding process. The transformer also provides galvanic isolation between the high voltage inverter stage and the low voltage welding terminals, which are exposed and can be touched by the user. This isolation significantly reduces the risk of electric shock and increases operational safety. A schematic of the transformer circuit is shown in Figure 1.7.

Figure 1.7: A step down center-tapped transformer with secondary side diode rectifier

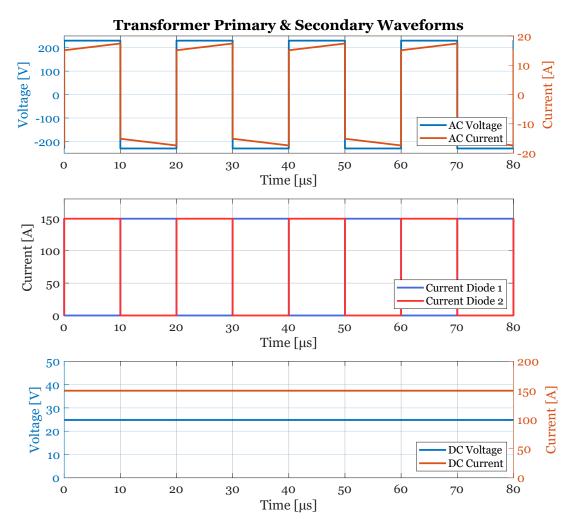

The secondary side of the transformer is center tapped so that the neutral wire is connected at the midpoint of the secondary winding. Each live wire is then connected to the load through diodes. This rectifies the current such that a DC output is provided between the terminals and the welding materials, represented in the circuit by *R*. An operational example of an almost ideal transformer is shown in Figure 1.8 where a 230 V 50 kHz square wave is applied to the transformer with a step-down ratio of 9.2.

Figure 1.8: Transformer voltage and current signals.

As shown in Figure 1.8 the AC voltage is lowered from 235 V to 25 V. The secondary side voltage is then rectified through the diodes, resulting in a DC signal at the output terminal of low voltage and high current. At this point, the output can now be used for welding.

#### 1.1.4 Improving efficiency in modern welding equipment

One of the goals in the welding industry today is to further improve the performance of each of the three circuits described above. Here, efficiency has been a key driver, as any reduction in power loss and thereby heat generation can improve many aspects of welding equipment, such as production cost, operating costs, equipment size, and system weight. One such company, Migatronic, is looking to improve the design of their existing welding equipment, focusing on their PFC rectifier. Currently, they are looking for new configurations that can improve efficiency over their current design.

To this end, the focus of this project will be examining Migatronic's current PFC rectifier design to identify potential improvements related to efficiency. As a result, the scope of this work will be limited to the PFC rectifier circuit. Although the high-frequency inverter and step-down transformer stages are important to the overall system, they will not be investigated further in this project. In addition, different types of welding methods, such as TIG or MIG, are outside the scope of this project and therefore will not be considered.

# Evaluation of Migatronic's Converter and Proposed Improvements

This chapter presents the converter operating requirements set out by Migatronic. A brief presentation of Migatronic's existing converter is also shown. Here, a calculation of the existing converters losses is made in order to identify the main loss generating components. From this a new converter configuration is proposed with the intent to maximize efficiency. Then a comparison of different types of transistor is made with the intention of picking one. From this a problem formulation is then created that outlines the overall goals of the project.

#### 2.0.1 Migatronic Design Requirements

The converter requirements are based on the criteria set out by Migatronic. According to Migatronic the converter should be capable of drawing full power from a single phase, which is equated to 3.6 kW. The output voltage should be 400 V DC with a maximum ripple of  $\pm$  20 V. The maximum current ripple should be between 10-20 %. Finally, the total efficiency of the converter should exceed 97 % at full power.

Assuming that the converter is ideal, the input power is equal to the output power, as such the expected input current can be calculated from the given design parameters as:

$$I_{ac} = \frac{P_o}{V_{ac}} \tag{2.1}$$

This results in an estimated input current of 15.6 A rms. This estimate serves as a reference to determine the rating requirements of the components to be selected. All parameters are listed in Table 2.1.

$$egin{array}{c|c} V_{ac} & 230 \ V \\ I_{ac} & 15.6 \ A \pm 1.56 - 3.12 \ A \\ V_{dc} & 400 \ V \pm 20 \ V \\ P_o & 3.6 \ kW \\ \eta & >97 \ \% \\ \end{array}$$

Table 2.1: Migatronic PFC converter requirements.

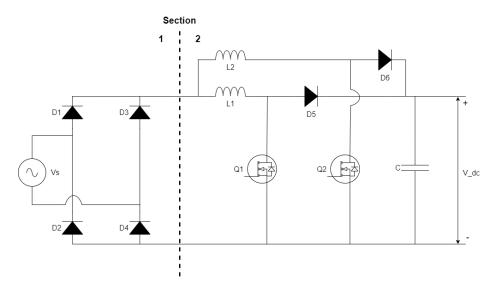

Migatronic currently uses an interleaved bridge PFC rectifier for their single-phase welding machines. This converter consists of two sections, which serve to rectify the current, increase the power factor (PF), and boost the output voltage. A schematic of the PFC rectifier is shown in Figure 2.1.

Figure 2.1: Interleaved bridge rectifier

The first section is a diode bridge that rectifies the input current. This is transferred to the second section, which improves the PF and increases the output to 400 V DC. The converter also implements an interleaved design, meaning that two boost converters are connected in parallel. This helps to improve efficiency and reduce component stress by splitting the input current and therefore reducing conduction losses. The two boost sections operation are also phase shifted 180 degrees from each other. As a result, the two currents are also phase shifted 180 degrees, this in turn reduces the ripple current at the output stage.

## 2.1 Estimation of Converter Component Loss

To estimate the performance of the converter, a loss calculation is performed. The loss calculation is based on data provided by Migatronic where available. For components without supplied data, real components were selected based on datasheet specifications that meet Migatronic converter design requirements. Table 2.2 lists all the components used. Following the schematic of Figure 2.1 from left to right, the component losses are calculated.

| Component       | Model             | Parameter         | Value | Unit      |

|-----------------|-------------------|-------------------|-------|-----------|

| SI MOSFET       | FCP170N60         | $R_{on}$          | 175   | mΩ        |

|                 |                   | $t_r$ (Rise time) | 12    | ns        |

|                 |                   | $t_f$ (Fall time) | 3.8   | ns        |

| Rectifier Diode | GBPC3512W         | $V_f$             | 1.1   | V         |

| Schottky Diode  | IDV20E65D1        | $V_f$             | 1.3   | V         |

| Inductor        | PHBC24N-2R0A0219V | DCR               | 19.5  | $m\Omega$ |

| Capacitor       | ALC70(1)821EN600  | ESR               | 163   | mΩ        |

**Table 2.2:** Overview of chosen components and loss-relevant parameters based on 100 °C operating temperature [4] [18] [7] [13] [11]

The first major losses are seen in the diode bridge, which comes from the forward voltage drop during conduction. Here D1 and D4 conduct for the positive half-cycle, and D2 and

D3 conduct during the negative half-cycle. The total loss seen in the diode bridge can be calculated using Equation 2.2.

$$P_{Diode.slow} = 2 \cdot V_f \cdot I_{ac,rms} \tag{2.2}$$

Next are the inductor losses, where only the resistive losses will be considered. Given that the average inductor currents are equal to each other,  $I_L$  is given as  $I_L = I_{L1} = I_{L2}$ . The inductor losses are then calculated using Equation 2.3.

$$P_L = 2 \cdot I_L^2 \cdot R_L \tag{2.3}$$

Two fast diodes are present, with one in each switching leg where most of the losses consist of the conduction losses from the forward voltage drop. The total losses of the fast diodes are calculated using Equation 2.4.

$$P_{Diode,fast} = 2 \cdot V_f \cdot I_L \cdot (1 - D) \tag{2.4}$$

Here, *D* is the duty cycle, where the average duty cycle is 0.5. The MOSFET losses are made up of the conduction and switching losses. Here, the conduction losses are calculated using Equation 2.5

$$P_{con} = 2 \cdot I_L^2 \cdot R_{on} \cdot D \tag{2.5}$$

Likewise, the switching losses can be found using Equation 2.6.

$$P_{sw} = V_o \cdot I_L \cdot (t_r + t_f) \cdot f_{sw} \tag{2.6}$$

Lastly, capacitor losses can be found using Equation 2.7

$$P_{cap} = I_o^2 \cdot R_{esr} \tag{2.7}$$

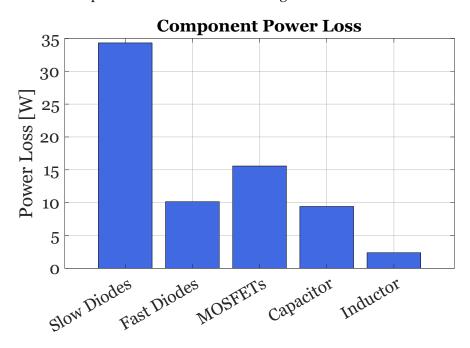

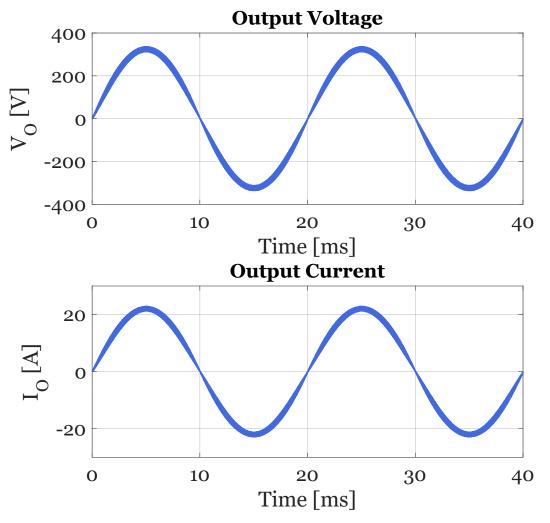

All the calculated component losses are shown in figure 2.2.

Figure 2.2: Estimation of component losses in Migatronic's existing converter based on datasheet parameters

From Figure 2.2 the total component losses are 71.8 Watt, which gives a converter efficiency of 98 % this is 1 % higher than the stated 97 % which Migatronics estimates their converter efficiency to be. However, some difference is expected since estimations of components had to be made as not all data was available from Migatronic. Additionally, the equations used to calculate the losses are only estimates and do not consider things such as the reverse recovery of the diodes or the impact of gate driver design on MOSFET losses. Regardless of the difference, Figure 2.2 reveals that the majority of component losses occur in the diodes and MOSFETs where the combined losses constitute 60 W of the total losses. While the capacitor and inductor losses are also significant, these are harder to reduce as the loss parameters are directly related to the design requirements of the converter, such as breakdown voltage, inductance, capacitance and rated current. In contrast, many of the MOSFET and diode losses can be reduced or completely eliminated by using a different converter configuration. With this in mind, a new converter configuration is investigated with the goal of improving efficiency.

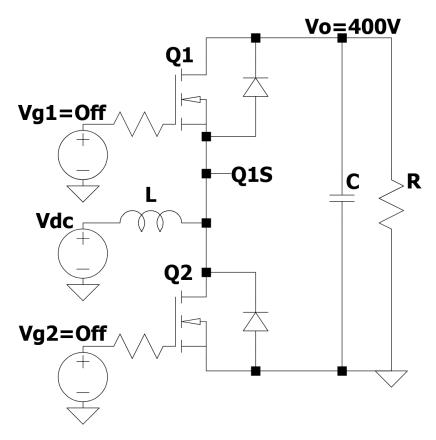

## 2.2 Converter Configuration & Transistor choice

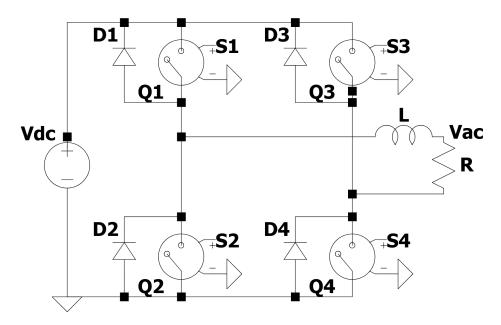

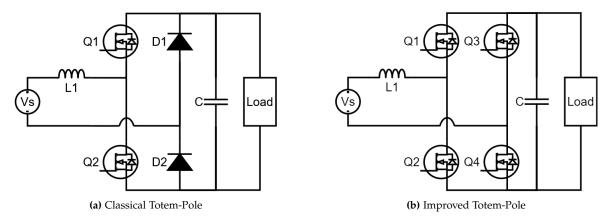

In order to reduce the number of components and reduce the complexity of the control, interleaved configurations will not be investigated. Additionally, only full bridge configurations will be considered to reduce the size of the DC link capacitor. There exist several configurations that use a bridgeless design. However, as the main objective is to increase efficiency, the totem pole configuration is selected for further analysis. This configuration is chosen because it incorporates only two or no diodes, as such it holds the potential to achieve a high efficiency. The totem pole configuration consists of two variants. The following diagrams presented in Figure 2.3 show the two totem pole configurations that will be described.

The classic Totem Pole, shown in (a), uses two switches in the High-Frequency (HF) leg and two diodes in the Low-Frequency (LF) leg. This configuration simplifies the control, since the diodes passively determine the current direction depending on the input voltage polarity. The downside is the losses caused by the diode forward voltage [9, 17]. In order to improve efficiency, the diodes can be replaced with switches that turn on and off according to the input voltage polarity. This allows the switches to mimic the behavior of the diodes, while reducing losses. This configuration requires a more complicated control scheme since the LF leg requires active control to turn on and off the switches. As the stated goal of this project is to maximize efficiency, the second configuration is chosen. [9, 17]

Figure 2.3: Totem-Pole configurations

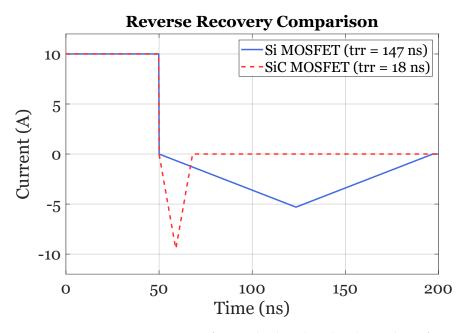

The Totem pole configuration offers high efficiency potential but has historically faced challenges in high-power applications. Because Q1 and Q2 are stacked on top of each other, it is required to have dead-time between each switching cycle. During the dead-time period, the body diode of Q1 conducts until Q2 turns on. As a result of this, the body diode goes through a reverse recovery period  $t_{rr}$ . In Si MOSFEts the reverse recovery charge  $Q_{rr}$  is very high compared to the newer SiC MOSFET as shown in Figure 2.4

**Figure 2.4:** Reverse recovery comparison of SiC and Si based on datasheet values of MOSFETs "IPBE65R099CFD7A" and "C3M0045065K" [21] [8]

Since the reverse recovery period is much larger in the Si MOSFET the switching frequency is limited to avoid high switching losses. Consequently, this requires large inductors to meet the ripple current requirements. However, large inductors are typically not viable due to cost and size restrictions. Alternatively, running the converter in critical conduction mode (CrCM) could eliminate ripple requirements, but CrCM poses other problems in the form of high peak currents, increasing the rating of components and a varying switching frequency, which complicates filter design for EMI compliance. Therefore, Si MOSFETs are not considered for the converter.

As such, the two semiconductor technologies considered are SiC and GaN. Compared to traditional Si devices, both offer significantly improved performance characteristics, including lower conduction and switching losses. In addition, SiC has a much lower reverse recovery charge ( $Q_{rr}$ ) and GaNFETs do not have reverse recovery at all because they do not have a body diode. Therefore, both are viable choices for a totem pole configuration. However, there are some significant differences between them that are worth discussing. SiC is similar to Si as both are MOSFETs with the same structural build-up. as such, the difference is in the material composition. SiC offers several advantages over Si, including a higher dielectric breakdown voltage and great thermal conductivity. This results in a lower On resistance due to a reduced material path length.[10]

GaN transistors have historically been used for low-power high-switching-frequency applications. This has been primarily due to the low capacitance of the gate drain resulting in high switching speeds and due to the lack of a body diode resulting in no reverse recovery  $Q_{rr}$ . More recently GaN transistors have started to see increased use in power applications

where voltages of 600-800 V are used. They are generally a good choice for maximizing efficiency, as they have very low switching losses.[10]

The following is a table of the main advantages and limitations of SiC and GaN transistors.

#### SiC MOSFETs

#### • Advantages:

- Good power scalability, with options above 3 kV breakdown voltage.

- Low conduction losses due to low ON resistance.

- Low switching losses, due to low  $Q_{rr}$  and fast switching speeds.

- Higher thermal conductivity, resulting in simpler and smaller cooling solutions

- High temperature stability, Performance characteristics like on resistance only increase slightly % from 25 °C to 125 °C.

#### • Limitations:

- High body diode forward voltage of 3-5 V, leading to high losses during dead time operation.

- Negative bias turn-off voltage, resulting in a more complex gate drive design.

- Prone to gate driver ringing due to fast switching speeds.

#### **GaN Transistors**

#### Advantages:

- High efficiency potential

- Low conduction losses due to low ON resistance.

- The absence of a body diode means that there are no reverse recovery losses.

- Low switching losses, due zero  $Q_{rr}$  and fast switching speeds.

- Reduced losses in dead time operation range compared to SiC, due to reverse conduction voltage drop of 2-3 V.

#### • Limitations:

- Low thermal conductivity, meaning more complex cooling solutions.

- Low temperature stability, performance characteristics are sensitive to changes in temperature, resistance can double from 25 °C to 125 °C.

- Negative bias turn-off voltage, resulting in more complex gate drive design.

- Prone to gate driver ringing due to fast switching speeds.

In summary, while both SiC and GaN transistors present significant advancements over Si MOSFETs and are suitable for high-efficiency totem pole configurations, they have distinct characteristics and trade-offs. SiC MOSFETs are advantageous for high-power applications because of their robust thermal performance and higher breakdown voltage capabilities. GaN transistors excel in high-frequency applications due to their superior switching performance but can face challenges in power scalability and thermal management.

Although GaN transistors show great promise, this project chose to go with SiC MOSFETs. This choice was made for several reasons. Firstly, SiC MOSFETs were already available for use at the start of the project, which speeds up the design process. Additionally, the thermal advantages of SiC is a significant benefit, as they simplify the cooling solution required.

## 2.3 Project Scope

In order to achieve a higher converter efficiency, a more efficient topology has to be applied. One of the topologies that has the highest potential to increase efficiency is the Totem pole configuration. Compared to traditional topologies that use diodes in their design, the Totem pole configuration reduces losses by removing the need for diodes. When combined with improved conduction and switching characteristics of SiC MOSFETs relative to conventional silicon, the opportunity for enhancing overall converter efficiency is considerable.

Therefore, this project will investigate a 3.6 kW Totem-Pole converter using SiC MOSFETs, as this provides great potential for improvements in efficiency compared to Migatronic's existing converter.

Given the limited time available and the project being undertaken by one individual, several simplifications are made.

The converter will be tested in a DC-DC and inverter configuration. This allows the converter to be tested using an open-loop control structure, which in turn removes the need for measuring circuits.

A common mode filter will not be implemented to simplify the design process.

An external power supply will be used to power the gate driver circuits.

A 2-layer PCB will be used to increase the speed at which the converter can be constructed. In-house components will be used when possible to speed up the design process.

#### 2.4 Problem Statement

From the contents discussed, a problem statement is constructed. The problem statement aims to describe the primary problem that will be addressed in this project. Several objectives will be presented that aim to outline the necessary steps that are required to answer the problem statement. The following problem statement is constructed.

How can a single phase 3.6 kW totem-pole converter be constructed and operated using state-of-the-art SiC MOSFETs, which achieve a higher efficiency than Migatronic's current design?

- Develop a control system to operate the converter

- Identify components which fulfill Migatronic's requirements.

- Create a simulation model to verify converter operation

- Design a PCB circuit for the converter

- Build and test the prototype, in order to identify key problems that need to be solved

- Verify correct converter operation and estimate the efficiency

# **Control Strategy of Converter**

This chapter addresses the design process of the converter control system. This includes the motivation to test the converter in a DC-DC and inverter configuration. The implementation of the control schemes will be presented, and an explanation of the code structure and verification of the control signals will be shown.

## 3.1 Selection of Hardware Implementation Platform

In order to control the converter, an FPGA-based solution is selected. Unlike microcontrollers, which rely on software execution, an FPGA is a hardware-based platform that allows digital logic to be directly implemented. Furthermore, because FPGAs are hardware-based, their performance is significantly better for high-speed operations. They are able to generate PWM with very little latency and precise timing, which is important for things such as accurate dead-time implementation[19]. The control structure is implemented using a Cmod S7 programmable development board, which is built around a Xilinx Spartan 7 FPGA. This board includes 32 digital I/O pins, two analog input signals, and a 5V rail. The board also includes a 12 MHz oscillator and a USB circuit for power and programming[3]. VHDL is used to program the FPGA using the Xilinx Vivado software.

## 3.2 Rationale for testing in DC-DC and Inverter Configuration

The evaluation of the converter will be carried out in a DC-DC and inverter configuration. This allows the converter to be operated in an open loop, removing the need for a feedback loop. There is also no need to measure the input voltage and current since they are constant. As such, the control system can be operated independently from the rest of the converter, while the output voltage is adjusted based on the governing equations and known variables. This simplifies the control system design and enhances its robustness, since any noise or transients originating from the converter will not adversely impact the controller. Furthermore, the converter can still be operated in a way that gives a good estimation of the converter's efficiency, since the current and voltages will be similar to the converter operating in PFC mode.

## 3.3 DC-DC Control Operating Principle

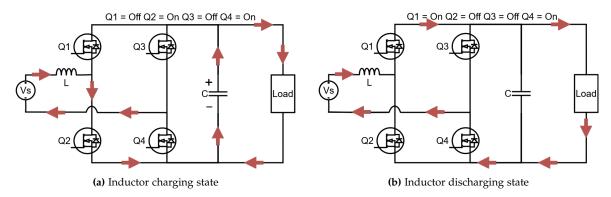

In this setup, the first leg consisting of Q1 and Q2 is treated as one pair when Q1 is in the "ON" state, Q2 is in the "OFF" state, and vice versa. In the second leg, Q3 is always turned "OFF" and Q4 is always turned "ON". When Q1 is "OFF" and Q2 is "ON", the current of the inductor will flow through Q2 and Q4 back to the source, causing the inductor to charge and the capacitor to discharge, as illustrated in Figure 3.1 (a). When Q1 is "ON" and Q2 is "OFF", the inductor current will flow through the capacitor and the load, causing the inductor to discharge and the capacitor to charge, as illustrated in Figure 3.1 (b).

Figure 3.1: Converter switching states in DC-DC configuration

As such, the relationship between the charge state of the inductor and capacitor depends only on switches Q1 and Q2. This, in turn, simplifies the control since only the first leg has to be controlled.

#### 3.3.1 Duty cycle derivation of DC control structure

It is important to understand the relationship between the output voltage and the duty cycle of switches Q1 and Q2. This can be derived from the inductor current equations. In the charging state, the voltage across the inductor is the same as the input voltage  $V_S$  as given in Equation 3.1. During discharge, the inductor voltage is given by the output voltage  $V_O$  minus the input voltage  $V_S$  as seen in equation 3.2. Included in the equations are  $D_{Q2}$  for the duty cycle of Q2 and T for the period. These variables represent the amount of charge/discharge time with respect to a period.

$$\Delta I_L = \frac{V_s}{L} \cdot D_{Q2} \cdot T \qquad (3.1) \qquad \Delta I_L = \frac{\langle V_o \rangle - V_s}{L} \cdot (1 - D_{Q2}) \cdot T \qquad (3.2)$$

According to the steady-state condition, the average inductor current  $\Delta I_L$  over a period must be constant, and as such the positive and negative change in current must be equal, so that  $\Delta I_L - \Delta I_L = 0$ . Therefore, equations 3.1 and 3.2 can be set equal and variables L and T will cancel out. This is given in Equation 3.3.

$$V_s \cdot D_{O2} = (\langle V_o \rangle - V_s) \cdot (1 - D_{O2}) \tag{3.3}$$

Writing out the terms gives Equation 3.4.

$$V_s \cdot D_{O2} = \langle V_o \rangle - V_s - \langle V_o \rangle \cdot D_{O2} + V_s \cdot D_{O2}$$

(3.4)

From this, the term  $V_s \cdot D_Q$  cancels out, giving Equation 3.5

$$V_s = < V_o > - < V_o > \cdot D_{O2} \tag{3.5}$$

Factoring the output voltage  $\langle V_o \rangle$  gives Equation 3.6.

$$V_s = (1 - D_{O2}) \cdot \langle V_o \rangle \tag{3.6}$$

The equation can then be rearranged with respect to  $D_{O2}$  as seen in Equation 3.7

$$D_{Q2} = 1 - \frac{V_s}{V_o} \tag{3.7}$$

Since the duty cycle *D* ranges from 0-1, it can be concluded that the converter operates in boost mode.

Before implementation, it is necessary to incorporate dead time. Dead time is a short time interval between each switching cycle in which both switches are off. This measure aims to prevent a shoot-through scenario in which the switches, Q1 and Q2, are turned on simultaneously. Avoiding this is crucial to avoid a situation where the DC capacitor is effectively short-circuited, resulting in the generation of high currents that would damage the converter. An implementation method is to reduce the ON time of both switches equally so that the duty ratio does not change. However, in this case, this would affect the output voltage since during the dead time the converter is still conducting because of the body diodes present in the switches. As a result of the orientation of the body diode, the current flows through Q1 and Q4, which is the same conduction state as shown in Figure 3.1 (b). To account for this effect, the inductor current equations can be rewritten as Equation 3.8.

$$\Delta I_L = \frac{V_s}{L} \cdot D_{Q2} \cdot T - \frac{\langle V_o \rangle - V_s}{L} \cdot k_d \cdot T \tag{3.8}$$

And Equation 3.9

$$\Delta I_L = \frac{\langle V_o \rangle - V_s}{I_s} \cdot D_{Q1} \cdot T + \frac{\langle V_o \rangle - V_s}{I_s} \cdot k_d \cdot T \tag{3.9}$$

Where,  $k_d$  represents the fraction of time spent in dead time with respect to the period T. From equations 3.8 and 3.9 it is shown that the inductor discharges at an additional rate equal to twice the dead time. This also means that the dead time affects only the inductor discharge rate. Therefore, only the duty cycle of Q1 needs to be adjusted to account for the dead time. As such, the relationship between  $D_{Q1}$   $k_d$  can be derived. Equations 3.8 and 3.9 are set equal and the variables L and T cancel out, giving Equation 3.10.

$$V_s \cdot D_{O2} = (V_o - V_s) \cdot D_{O1} + 2 \cdot k_d \cdot (V_o - V_s)$$

(3.10)

Isolating for  $D_{Q1}$  gives Equation 3.11.

$$D_{Q1} = \frac{V_s \cdot D_{Q2}}{V_o - V_s} - 2 \cdot k_d \tag{3.11}$$

Substituting  $D_{O2}$  with Equation 3.7, then gives the final Equation 3.12.

$$D_{Q1} = \frac{V_s}{V_o} - 2 \cdot k_d \tag{3.12}$$

From this, the duty cycle can be set on the basis of a given input voltage, a desired output voltage, and a dead time.

#### 3.3.2 Implementation of DC control system

Since the oscillator acts as a clock reference for the FPGA, it will be used to define the switching frequency in terms of clock cycles. By tracking each rising edge of the clock, the elapsed time can be recorded; at 12 MHz this equals 83.33 ns for a period. As such, the number of clock cycles to a given switching frequency can be calculated as the ratio of the clock frequency and the switching frequency given as  $c_s = f_c/f_s$ . The duty cycle can then

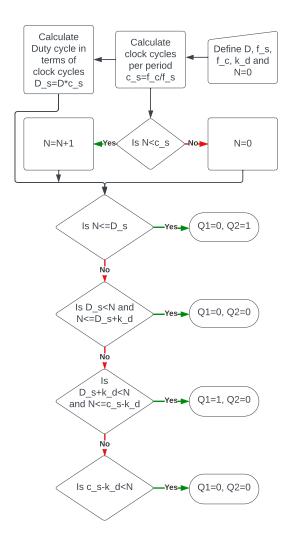

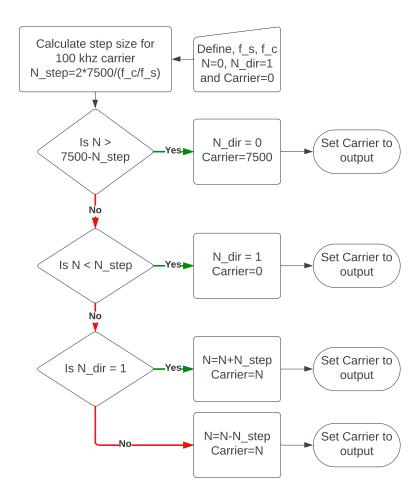

also be defined in terms of clock cycles by multiplying the duty cycle by  $c_s$  as  $D_s = D \cdot c_s$ . Lastly, the dead time  $k_d$  can also be defined in terms of clock cycles. Then a series of *if* statements can be constructed that check whether the time counter is below or above the thresholds set by  $D_s$ ,  $k_d$ , and  $c_s$ . An illustration of the control process using a flow chart is shown in Figure 3.2.

Figure 3.2: Flowchart diagram of the control process for FPGA signal generation

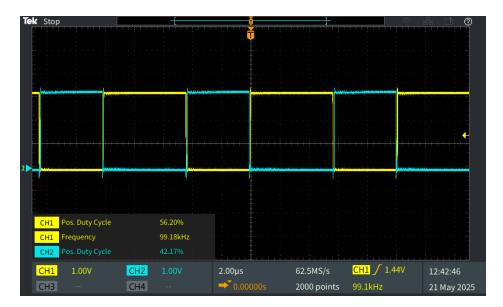

Because time is tracked through a clock in finite increments, timing errors can occur. If the chosen duty cycle is not an integer multiplicative of the clock period, the output signal will deviate from the intended one. In the worst case, this can be up to half the clock period. Furthermore, the relative error increases at lower duty cycles, since the absolute timing error is constant relative to the on-time. To reduce the relative error, a higher frequency oscillator is needed, or the switching frequency has to be reduced. To test the program, the code is executed with a duty cycle of  $D_{Q1}=0.56$ , a dead time of 1 clock cycle, and a switching frequency of 100 kHz. The FPGA output signals are shown in Figures 3.3 and 3.4.

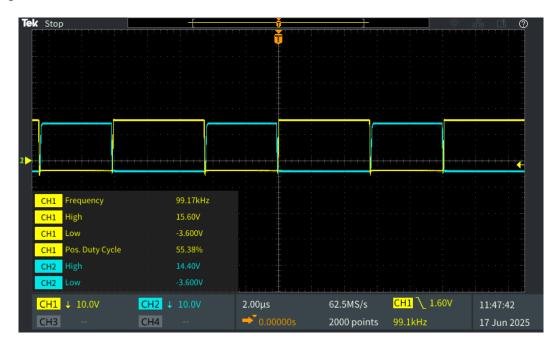

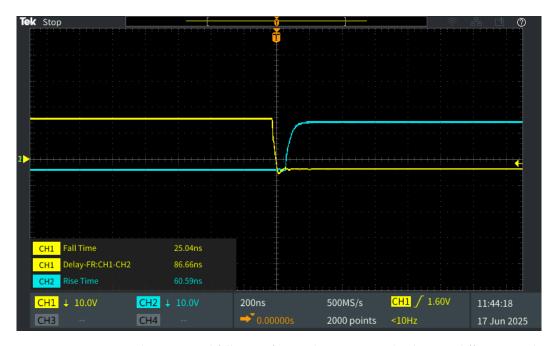

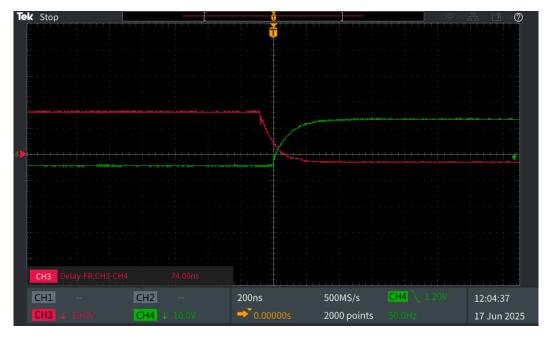

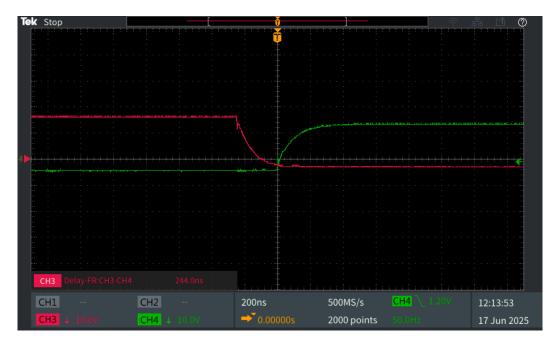

Figure 3.3: FPGA gate control signals, showing duty cycle and frequency

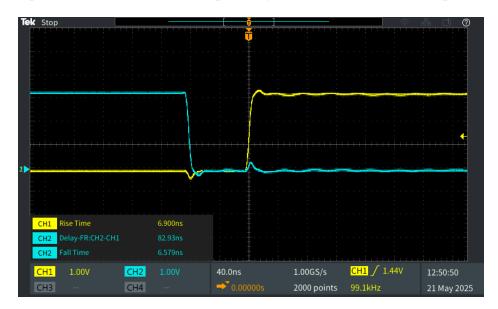

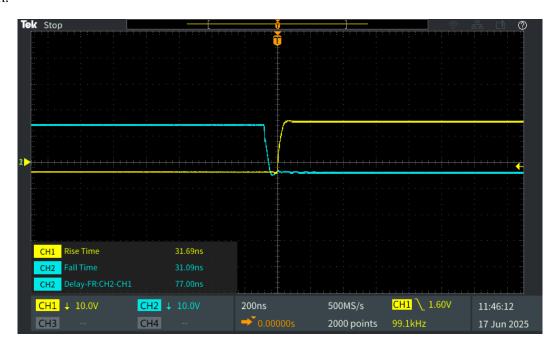

According to Figure 3.3, the switching frequency is 99.2 kHz, which corresponds well to the approximate period of  $10\mu s$ , the on time of Q1 is  $5.62\mu s$ , which gives a discrepancy from the desired value. However, this is expected since the difference of  $0.08\mu s$  is approximately equal to one clock cycle of dead time. The Q2 on time is  $4.217\mu s$  and is also slightly lower due to the dead time. Finally, Figure 3.4 shows the rise and fall time of the control signals and the dead time period, here the fall and rise time is between 6.5-7 ns and the dead-time period is 83 ns which lines up exactly with the oscillators clock period.

Figure 3.4: FPGA Gate control signals, showing the rise time, fall time and dead time

According to both graphs, the FPGA output is very close to the desired output. From this, it is shown that the code works as intended and that the FPGA output can be used to drive the converter in a DC-DC configuration.

## 3.4 Inverter Control Operating Principle

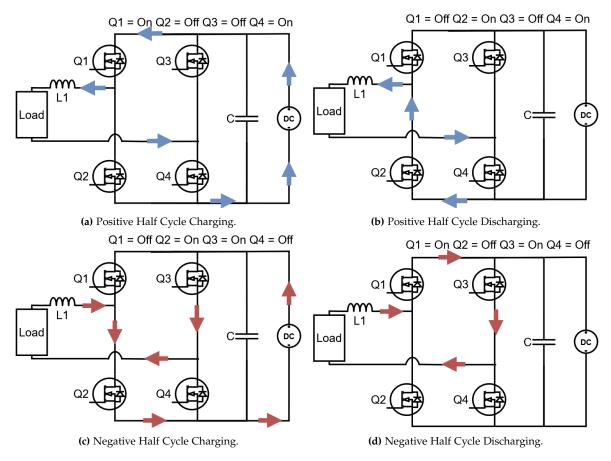

For the inverter, unipolar switching is used. This control strategy is used because it is the reverse of the operating strategy used when the converter is operating in PFC mode. This means that the current and voltage through the switches would be the same. This in turn allows the switch losses calculated in the inverter configuration to be used directly as reference for the losses that can be expected in a PFC converter configuration. In this control strategy, the first leg consisting of Q1 and Q2 is treated as one pair, here when Q1 is in the "ON" state, Q2 is in the "OFF" state, and vice versa. In the second leg, Q3 and Q4 are also complementary, so when one is off, the other is on. In this setup, the two legs will operate at different frequencies. Here, the HF leg consisting of Q1 and Q2 will operate at 100 kHz, while the LF leg Q3 and Q4 will operate at 50 Hz. During operation there are 4 different states, each of these states determines whether the inductor is charging or discharging and what the polarity is. In the positive half-cycle, Q3 is off and Q4 is on. Therefore, the inductor charges when Q1 is on and Q2 is off and discharges when Q1 is off and Q2 is on, this can be seen in Figures 3.5 (a) and (b). During the negative half-cycle, Q3 is on and Q4 is off. Here, the inductor charges when Q1 is off and Q2 is on and discharges when Q1 is on and Q2 is off. This is shown in Figures 3.5 (c) and (d). As a result, it can be concluded that the inductor charge/discharge state is only dependent on the duty cycle of Q1 and Q2. Furthermore, the duty cycle applied to the HF leg during the positive cycle just has to be inverted during the negative cycle. As such, the duty cycle only needs to be derived for one half-cycle.

Figure 3.5: Operation principle in inverter configuration

#### 3.4.1 Duty cycle derivation of inverter control structure

To control the converter, it is important to understand the relationship between the output voltage and the duty cycle of switches Q1 and Q2. This can be derived from the inductor current equations in the positive half-cycle. In the charging state, the voltage across the inductor is equal to the input voltage  $V_S$  minus the output voltage  $V_O$  as given in Equation 3.13. During discharge, the inductor voltage is equal to the output voltage  $V_O$  as seen in the equation 3.14. The equations are  $D_{Q1}$  for the duty cycle of Q1 and T for the period.

$$\Delta I_L = \frac{V_s - \langle V_o \rangle}{L} \cdot D_{Q1,pos} \cdot T$$

(3.13)  $\Delta I_L = \frac{\langle V_o \rangle}{L} \cdot (1 - D_{Q1,pos}) \cdot T$  (3.14)

According to the steady-state conditions, the change in current should be the same for charging and discharging, so equations 3.13 and 3.14 can be set equal and variables L and T cancel out, giving equation 3.15.

$$(V_s - \langle V_o \rangle) \cdot D_{O1,pos} = \langle V_o \rangle \cdot (1 - D_{O1,pos}) \tag{3.15}$$

The derivation of equation 3.15 and isolating for  $D_{Q1,pos}$  gives the relationship between the Duty cycle and the input and output voltage, as shown in equation 3.16 .

$$D_{Q1,pos} = \frac{V_o}{V_s} \tag{3.16}$$

Since the duty cycle can only be between 0 and 1 and the output voltage decreases when the duty cycle decreases, it can be concluded that the converter operates in buck mode. Similarly to the DC configuration, dead time is also needed in order to avoid shoot-through, in this case from the DC supply. In this case during dead-time it results in additional discharging of the inductor. To compensate for this, the duty cycle of  $D_{Q2,pos}$  is shown in equation 3.17.

$$D_{Q2,pos} = 1 - D_{Q1,pos} - 2 \cdot k_d \tag{3.17}$$

Now that the duty cycle for the positive half wave has been derived, the negative wave duty cycles are simply the inverted values as shown in equations 3.18 and 3.19.

$$D_{Q1,neg} = D_{Q2,pos}$$

(3.18)  $D_{Q2,neg} = D_{Q1,pos}$  (3.19)

With these equations, the relationship between the input voltage and the output voltage is known. However, in order to generate a sinusoidal output voltage waveform the duty cycle needs to vary over time, in order to do this a control system is implemented on the FPGA controller.

#### 3.4.2 Implementation of inverter control system

In order to output the correct PWM signals, a carrier and duty cycle must be created. These must be designed according to the desired output voltage, fundamental frequency, and switching frequency. The output of the carrier and duty cycle is then compared in a comparator, which then outputs the necessary PWM signals.

To create a carrier wave  $f_s$ ,  $f_c$ , N, and  $N_{dir}$  are defined, each representing the switching frequency, the clock frequency, the counter and the direction accordingly. The amplitude of the carrier signal is chosen as 7500. Then in order to obtain the correct frequency of the carrier, the step size has to be set such that the number of clock cycles it takes to go through one carrier period is equal to 10  $\mu$ s. This is calculated using equation 3.20.

$$N_{step} = \frac{2 \cdot 7500 \cdot f_s}{f_c} \tag{3.20}$$

With the step size calculated as 125 a series of if statements is constructed. This is shown in Figure 3.6.

Figure 3.6: Flowchart diagram of the generated carrier wave

The *if* statements compare the value of N to check what the value of the carrier should be. Furthermore, when N reaches 0 or 7500 the value of  $N_{dir}$  is flipped, which is then used to determine whether the carrier signal should increase or decrease. The final result is a 100 kHz carrier wave changing in steps of 125 between 0 and 7500. The carrier signal is then connected to the output so that it can be used by the comparator.

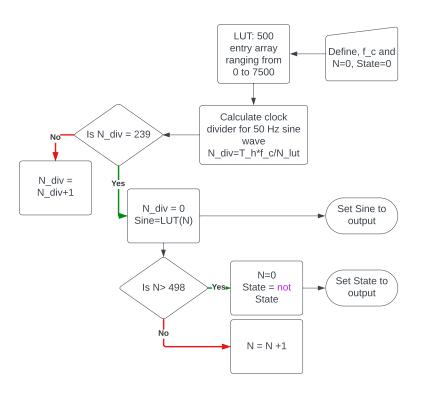

To generate a sinusoidal voltage output using PWM signals, the duty cycle must be varied over time to look like the half-cycle of a sine waveform. In an FPGA, a sine waveform can be represented using a lookup table (LUT). Here, the LUT stores multiple points on the sine waveform. These values are then accessed using a counter to produce a digital

representation of the sine waveform. To generate the sine LUT values for one half-cycle, equation 3.21 is used.

$$Lut(N) = M \cdot 7500 \cdot sin(\pi \cdot N) \tag{3.21}$$

Here,  $M = V_o/V_s$  is the modulation index that is used to generate values that give the correct output voltage. 7500 is the amplitude and is included to scale the values to the carrier wave range. N is an integer that goes from 1 to 500 in step sizes of 1. The generated value is then stored in the LUT for each value of N. This gives a LUT with 500 values. Lastly, because the LUT values at the beginning and end are very low, this will result in a very low duty cycle that can go below 1 %. At a 100 kHz switching frequency, this would result in a turn-on time of less than 100 ns. This is too short when considering the dead time that is needed and the rise time of the gate source voltage. As a result, the duty cycle at the extremes is clamped, so it cannot go below 6.5 %. With the LUT generated, it can be implemented in a VHDL structure, a flowchart of this is shown in Figure 3.7.

Figure 3.7: Flowchart diagram of the Sine Wave Look Up Table

In order to shift through the values in the LUT  $f_c$ , N, Sine and State is defined, where State is used to determine polarity, and Sine is a LUT value used for the duty cycle. Since the frequency of the duty cycle is determined by the speed at which the counter N increments through the LUT, this would result in a frequency of approximately 24 kHz when N follows the clock frequency  $f_c$ . This is much faster than the required 50 Hz. Therefore, a clock divider is required to reduce the frequency. The clock dividers values is determined using equation 3.22.

$$N_{div} = \frac{f_{sine} \cdot f_c}{500} \tag{3.22}$$

where  $f_{sine}$  is the desired frequency of the duty cycle. With this, the clock divider  $N_{div}$  is calculated as 240. Through a series of if statements, the value of  $N_{div}$  and N is checked. When  $N_{div}$  reaches its maximum value, Sine is updated to the next LUT value using N. Furthermore, when N reaches the end of the LUT table represented by 499, the State signal is inverted. This allows State to record each time a half-cycle has passed. Both the State and Sine signals are connected to the output. These are then used in combination with the carrier signal to generate the PWM signals.

The comparator uses the three inputs *Sine*, *State*, and *Carrier* to determine the value of switches Q1, Q2, Q3, and Q4. This is done using a series of *if* statements shown in Figure 3.8.

Figure 3.8: Flowchart diagram of the comparator for PWM signal generation

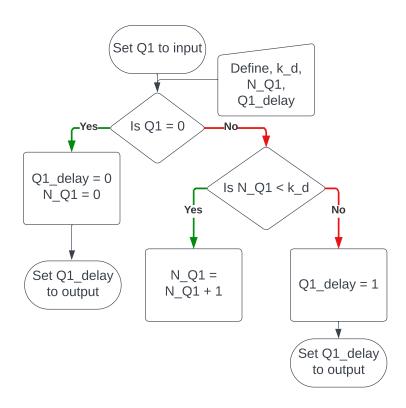

First, the signal *State* is checked to determine the polarity where Q3 and Q4 are set on the basis of this polarity. For Q1 and Q2, *State* inverts their PWM behavior, and their switching is controlled by the comparison between *Sine* and *Carrier*. Q1, Q2, Q3, and Q4 are connected to the output terminals. Using this all 4 PWM signals are generated and vary with respect to a sine waveform and the polarity. However, before this can be implemented into the FPGA dead-time is required during each switching transition. To implement dead-time, a delay structure is created. The delay structure for Q1 is shown in Figure 3.9.

Figure 3.9: Flowchart diagram of the dead time implementation shown for Q1

Here,  $k_d$ ,  $N_{Q1}$ , and  $Q1_{delay}$  are defined, representing the dead-time in the number of clock cycles, the Q1 counter, and the delayed output signal, respectively. Then a series of if statements is used to check the value of the input signal Q1. If Q1 is 1 a counter is started and the input Q1 is first transferred to the output  $Q1_{delay}$  when the counter  $N_{Q1}$  is equal to the dead-time in clock cycles  $k_d$ . This structure allows dead-time to be implemented in increments of 83.33 ns. This same structure is connected to Q2 Q3 and Q4 as well to implement dead time on all PWM signals.

With this, all 4 control structures, the Carrier generator, the Sine LUT, the PWM comparator, and the delay block are finalized. As such, this can then be implemented into the FPGA and the PWM signals can be tested.

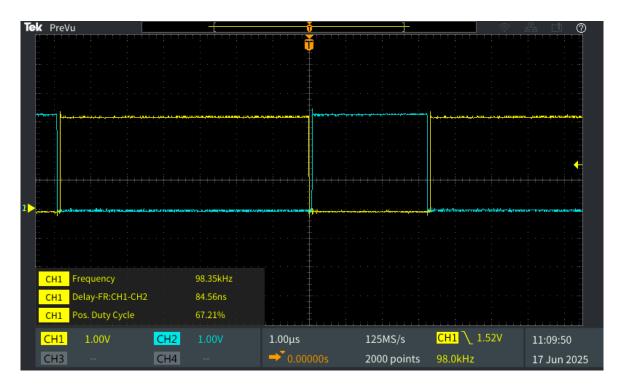

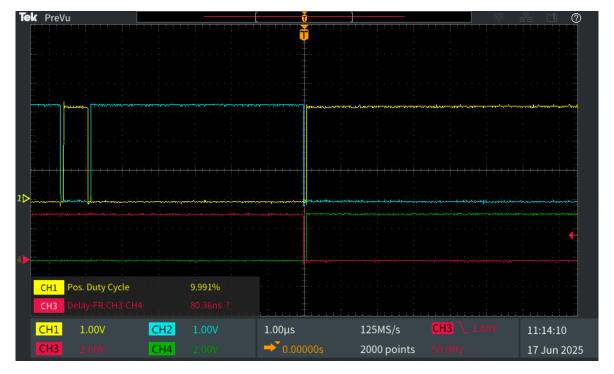

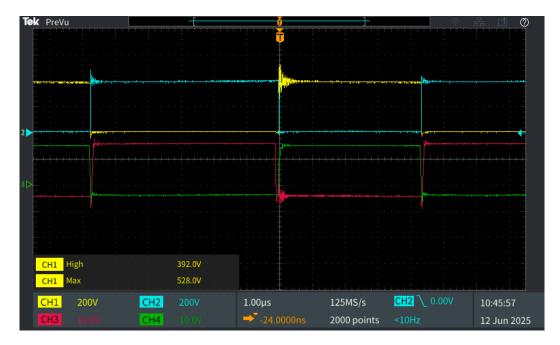

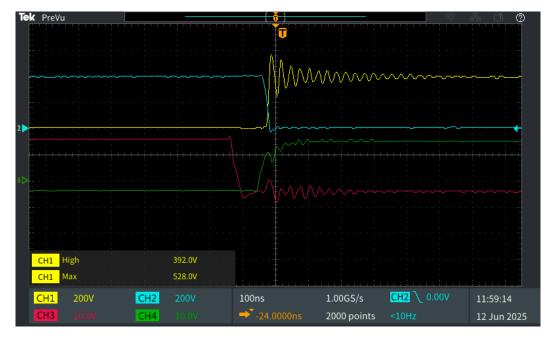

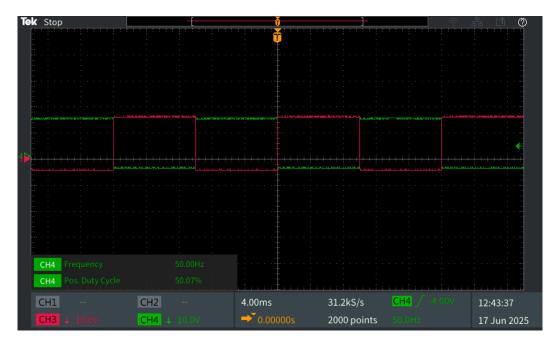

In Figure 3.10 the PWM signals of Q1 and Q2 are shown represented as "CH1" and "CH2", respectively. Here, the frequency is 98.35 kHz, which is close to the expected frequency target, indicating that the carrier frequency is correct. Furthermore, there is also a dead time of 84 ns between switching transitions, which indicates that the delay block is working as intended. The Q1 PWM signal has a duty cycle of 67 %. Compared to the Q1 duty cycle in Figure 3.11, which is 9.9 %, this shows that the Q1 duty cycle is changing over time.

Figure 3.10: PWM signals of Q1 and Q2 showing correct frequency and dead time

From Figure 3.11. The four PWM signals Q1 Q2 Q3 and Q4 are shown. Here, Q3 and Q4 are represented as "CH3" and "CH4", respectively. It can be seen that when Q3 and Q4 switch, so do Q1 and Q2 and their duty cycle inverts. Indicating that the "State" signal is working as intended to change polarity. It can also be seen that there is a dead time between Q3 and Q4, showing that the delay block also works here.

Figure 3.11: PWM signals at the end of a half cycle, showing a low duty cycle of Q1

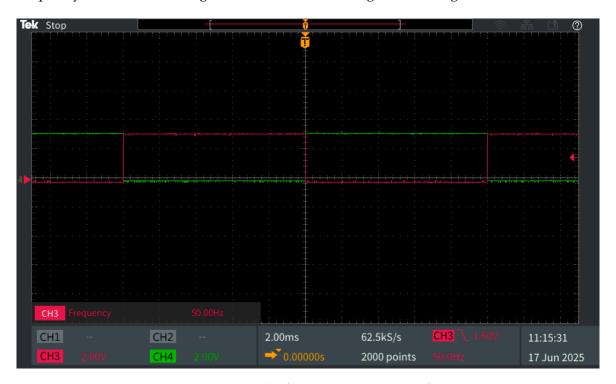

In Figure 3.12, Q3 and Q4 are shown over a longer time span. Here, it can be seen that the frequency is 50 hz, indicating that the clock divider logic is working as intended.

Figure 3.12: PWM signals of Q3 and Q4 with a 50 Hz frequency

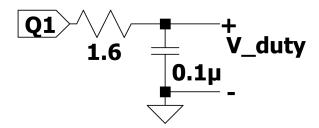

To ensure that the PWM signals behave correctly over an entire half-cycle, the duty cycle is evaluated. In order to show the duty cycle, an RC filter is constructed here the cut-off frequency is set to 1000 Hz. a 100 nF capacitor and a 1.6  $\Omega$  resistor are used. This is then connected to the PWM signal of Q1. The schematic of this is shown in Figure 3.13

Figure 3.13: RC filter used to measure the duty cycle of Q1

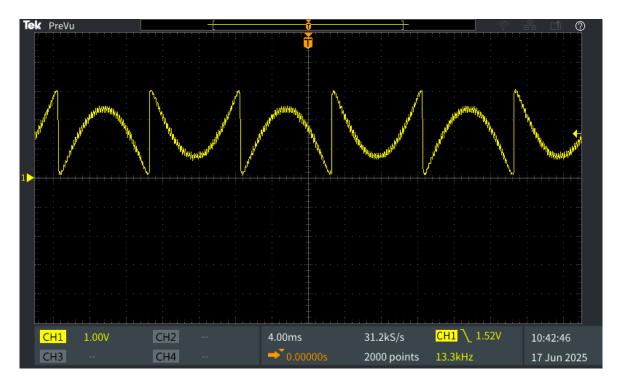

The voltage is then measured across the capacitor to display the duty cycle. This is shown in Figure 3.14. Looking at the duty cycle, it can be seen that it follows a sinusoidal waveform. Furthermore, the half-cycle frequency is 100 Hz, which is the desired frequency. Additionally, after each half-cycle the duty cycle flips, which indicates that the polarity is working.

Figure 3.14: Duty cycle of Q1 measured through an RC filter

Looking at the edges of the duty cycle where the maximum and minimum voltages occur, it can be seen that these range between 0.3 V and 3V. The duty cycle does not go above or below this range even though the Q1 PWM output from the controller is 0 or 3.3 V. This shows that the duty cycle clamping is working so that the turn on/off time does not get too small.

It is shown that the inverter control code is working as intended and can be used to drive the converter in the inverter configuration.

# Power Stage, Gate Driver Design and Passive Component Selection

In order to build the converter four switches are required. The choice of these switches is important because the conduction and switching characteristics directly impact the total losses of the converter. It is therefore important to consider how much loss can be expected in a given switch such that the efficiency of the converter can be as high as possible. In addition, the choice of switches also affects the necessary gate driver circuit required to operate them as intended. To this end, this chapter will decide the choice of switches based on a calculation of the estimated losses. The gate driver and the gate driver circuit will then be based on the operating criteria of the chosen switches.

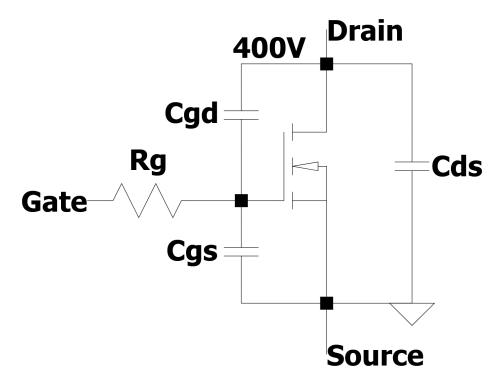

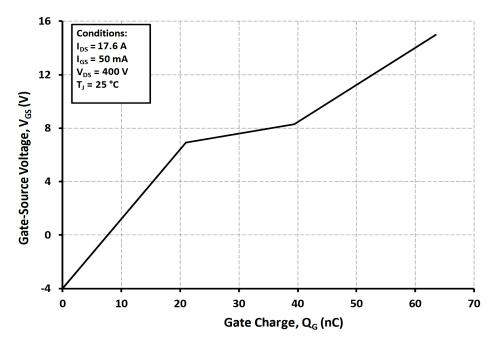

#### 4.1 Selection of SiC MOSFETs

One of the main design requirements of the switches is to reduce the losses so that the converter efficiency is higher than that of a Migatronic's existing configuration. According to Figure 2.2 the total losses currently seen in the switches and diodes are 60 W. As such, the goal is to use switches with total losses lower than this. To this end, the two primary losses that are relevant are the conduction losses and the switching losses. It is therefore also important to consider each converter leg individually, as the switching frequency is different. The two switches primarily considered are the SiC MOSFET's C3M0025065K and C3M0045065K from Wolfspeed, as these are already available in the laboratory, and they both are within the current rating required and have a sufficient breakdown voltage for this project. To compare both switches, the device characteristics of each switch are given in table 4.1.

| Switch Model:                          | C3M0045065K | C3M0025065K |

|----------------------------------------|-------------|-------------|

| On-State Resistance [ $m\Omega$ ]      | 45          | 25          |

| Turn-On Switching Energy $[\mu J]$     | 57          | 121         |

| Turn-Off Switching Energy [µJ]         | 14          | 53          |

| Gate Threshold Voltage [V]             | 2.6         | 2.3         |

| Recommended Vgs,on [V]                 | 15          | 15          |

| Recommended Vgs,off [V]                | -4          | -4          |

| Internal Gate Resistance $[\Omega]$    | 3           | 1.3         |

| Recommended Gate Resistance $[\Omega]$ | 2.5         | 2.5         |

| Body Diode Forward Voltage [V]         | 4.8         | 5           |

Table 4.1: Device characteristics of two SiC MOSFET's from Wolfspeed [21] [20]

Based on the device characteristics given in Table 4.1 the estimated losses that each switch leg will produce can be calculated. Here, the conduction losses consist of two parts. The losses when the switch is on and the losses during the dead-time when the body diode conducts. This can be calculated using Equation 4.1

$$P_{conduction} = I_{ac}^2 \cdot R_{on} \cdot \frac{T - t_d}{T} + I_{ac} \cdot V_f \cdot t_d$$

(4.1)

Where  $R_{on}$  is the switch on resistance,  $V_f$  is the body diode forward voltage; and T,  $t_d$  are the time period and dead time, respectively.

The total switching losses can be calculated as the sum of the turn on and off energy multiplied by the switching frequency. This is then multiplied by two to get the losses for both switches as given in Equation 4.2.

$$P_{switching} = 2 \cdot (E_{turn,on} + E_{turn,off}) \cdot f_s \tag{4.2}$$

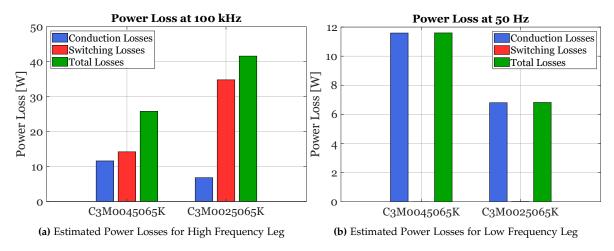

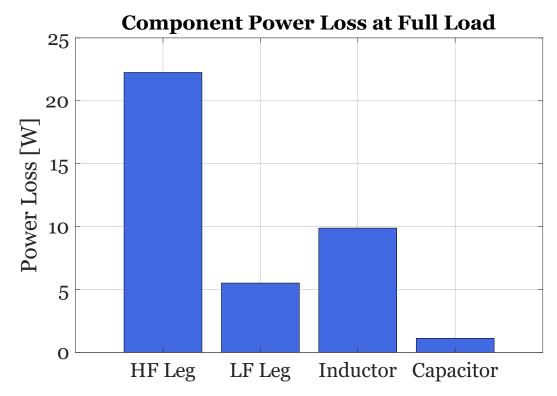

With these equations, the estimated losses of each switch can be calculated and the results are shown in Figure 4.1

Figure 4.1: Comparison of estimated switch power losses for each converter leg

As shown in Figure 4.1, the losses differ significantly for each converter leg due to the difference in frequency. In the HF leg, the C3M0045065K is the best choice as the superior switching characteristics make the total losses less than the C3M0025065K. In contrast, the C3M0025065K's better conduction properties excel in the LF leg, since the switching losses here are negligible. As a result, the C3M0045065K is chosen for the high frequency leg and the C3M0025065K is chosen for the low frequency leg. This gives a combined loss for both legs of 33 W. Approximately half of the diode and MOSFET losses in Migatronic's existing converter.

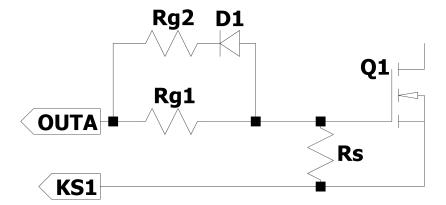

#### 4.2 Gate Driver Choice and Driver Circuit

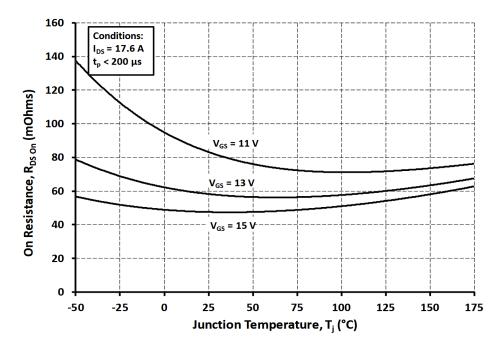

In order to turn the MOSFETs on and off, a gate driver is required. The gate driver should be chosen with regard to the recommended specifications of the MOSFET manufacturer as this helps to reduce switching losses and accidental turn on. The first consideration is the Gate driver turn on and turn of voltage. These values are important to consider as they directly impact ON resistance during conduction. This correlation is shown in Figure 4.2

Figure 4.2: The Corrolation between On resistance and Gate Driver voltage shown for C3M0045065K [21]

As seen, the best turn on voltage is 15 V as this gives the lowest ON resistance, which is also the recommended voltage given by the datasheet shown in Table 4.1.

To turn of the MOSFET the gate source voltage has to be below the threshold voltage of 2.6 V as this is the point when the MOSFET changes from its conducting state to its blocking state. However, the recommended turn-off voltage, as seen in Table 4.1, is -4 V. This negative bias voltage is recommended in order not to have an accidental turn-on triggered as a result of voltage spikes during switching. The last requirement is a gate driver that can deliver enough current to turn on the switch fast enough. The required current can then be calculated using Equation 4.3.

$$I_p = \frac{V_{gs+} - V_{gs-}}{R_{IG} + R_{EG}} \tag{4.3}$$

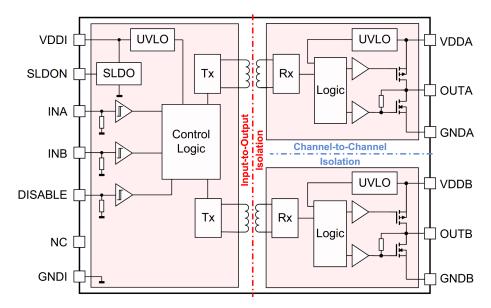

Using the internal resistance and the recommended gate resistance together with the recommended gate voltage, the minimum required drive current is 3.45 A. To this end, the Infineon "2EDS9265H" gate driver is chosen. This driver features a dual channel setup such that each switch leg needs only one driver. The driver can source 4 A during turn on and sink 8 A during turn off and can supply up to 20 V across the gate source. Furthermore, this driver implements galvanic isolation between the control and power side. This is implemented for safety reasons as it decouples the signal ground from the power ground. Allowing the control side to be designed with a different ground reference than the power side. In addition, galvanic isolation also protects the control side circuit from transients that are present at the gate driver from the parasitic capacitance coupling between the gate and the drain. A block diagram of the gate driver is shown in Figure 4.3

Figure 4.3: Block diagram of Infineon "2EDS9265H" gate driver [6]

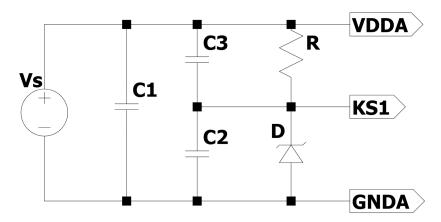

The left side of the block diagram consists of the control signal ports; here, "InA" and "INB" are connected to the signal ports of the FPGA. To power the control side, a 3.3 V or 5 V signal is required at the "VDDI" port. To enable the 5 V supply mode "SLDON" is connected to ground and a 1  $k\Omega$  resistor is connected to "VDDI". The 5 V is supplied by the FPGA power pin. This is then connected to a common signal ground "GNDI". A filter capacitor is also connected between "VDDI" and "GNDI" to stabilize the voltage sufficiently, as recommended in the datasheet[6]. The right side of the block diagram consists of two isolated channels, which supply the gate source voltage to the MOSFETs. In order to supply the -4 V during the turn off, an external circuit is required for each channel which can provide a negative voltage bias, A schematic of the circuit is shown in Figure 4.4.

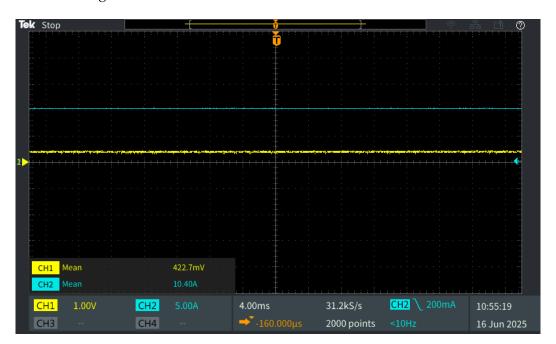

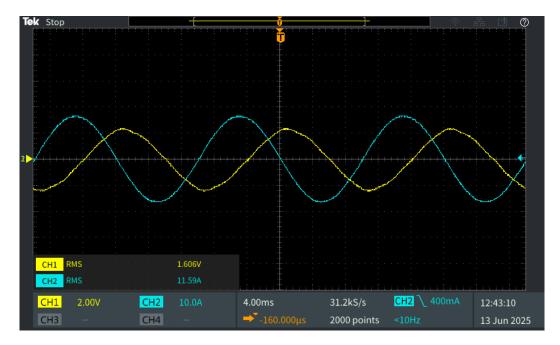

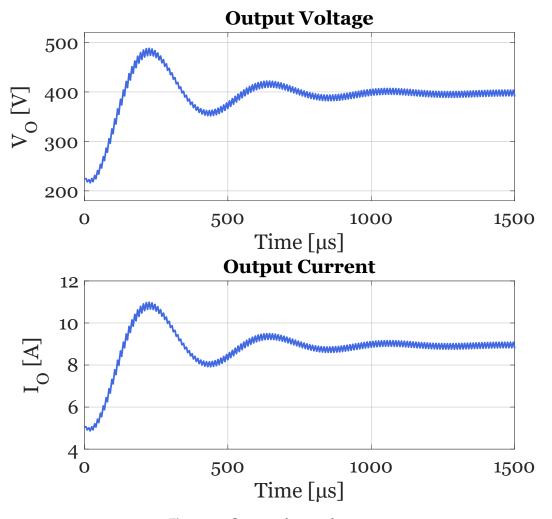

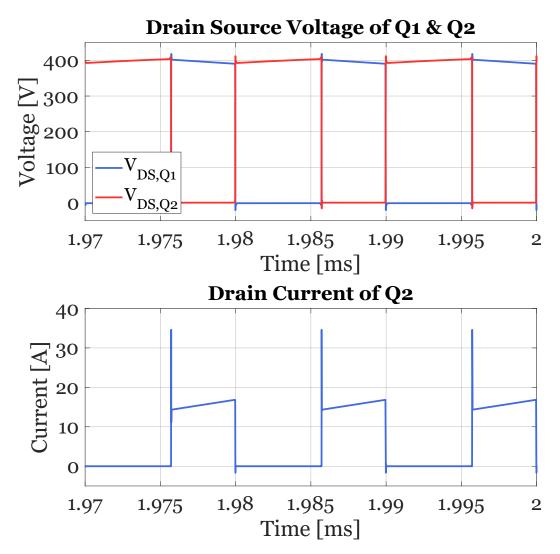

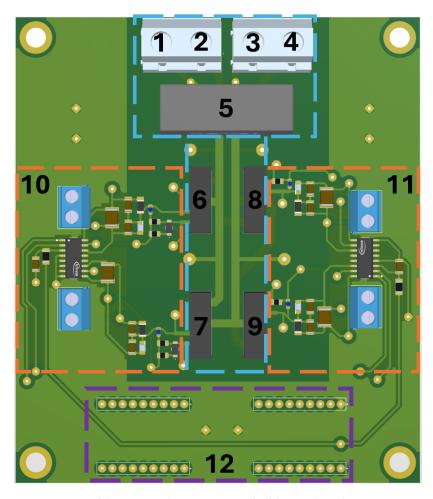

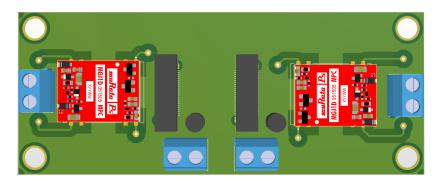

Figure 4.4: Negative bias voltage circuit using a Zener Diode