# A Dual-Model Detection Framework Based on Address Validation and Boolean Control Flow

- Runtime Software Attacks -

Master Thesis Franck Alex Olivier Molou & Casper Rømer Halling Larsen

> Aalborg University Electronics and IT

#### Electronics and IT

Aalborg University https://www.aau.dk

### AALBORG UNIVERSITY

### STUDENT REPORT

#### Title:

A Dual-Model Detection Framework Based on Address Validation and Boolean Control Flow

#### Theme:

Runtime Software Attacks

### **Project Period:**

Spring Semester 2025

### Participant(s):

Franck Alex O. Molou Casper Rømer Hallling Larsen

### Supervisor(s):

Edlira Dushku

Page Numbers: 111

### **Date of Completion:**

June 3, 2025

#### **Abstract:**

Runtime software attacks pose a significant threat to embedded and IoT systems, particularly in safety-critical domains such as medical devices. Unlike traditional malware, these attacks hijack control flow without injecting new code, using techniques such as Return-Oriented Programming (ROP). This thesis explores both offensive and defensive aspects of runtime attacks through a vulnerable insulin pump controller as a real-world proof-of-concept.

We first construct a functional ROP exploit on a standalone binary to demonstrate how attackers can bypass authentication and trigger unauthorized system calls using chained instruction-level gadgets. Building on this, we propose two lightweight runtime detection techniques for resource-constrained environments.

The first method, Address-based ROP Detection (ARD), validates return addresses at runtime against a static whitelist of legitimate control-flow targets. The second method introduces a Boolean State Validator (BSVD) model that encodes program logic into Boolean state transitions, enabling semantic anomaly detection.

Both techniques are implemented and evaluated using dynamic binary instrumentation (Intel PIN) and static analysis (Ghidra, angr). Results show reliable control-flow hijack detection with minimal overhead, without requiring source code or hardware changes.

# Acknowledgments

We would like to express our sincere gratitude to our supervisor, Edlira Dushku, for her invaluable guidance, encouragement and critical feedback throughout this thesis. Her expertise, ideas, and support have been essential to the successful completion of this work. Wer are especially grateful for her idea to let us explore her idea regarding the Boolean control flow graph as part of the detection approach, which played a central role in complementing our initial detection idea and shaping the direction of this research.

# **List of Acronyms**

| Acronym | Definition                         |  |  |  |  |

|---------|------------------------------------|--|--|--|--|

| ROP     | Return-Oriented Programming        |  |  |  |  |

| JOP     | Jump-Oriented Programming          |  |  |  |  |

| СОР     | Call-Oriented Programming          |  |  |  |  |

| JIT     | Just-In-Time                       |  |  |  |  |

| RET     | Ret instruction                    |  |  |  |  |

| VM      | Virtual Machine                    |  |  |  |  |

| PoC     | Proof of Concept                   |  |  |  |  |

| PAC     | Pointer Authentication Codes       |  |  |  |  |

| IoT     | Internet of Things                 |  |  |  |  |

| CFG     | Control Flow Graph                 |  |  |  |  |

| ARD     | Address-Based ROP Detection        |  |  |  |  |

| BSVD    | Boolean State Validation Detection |  |  |  |  |

| B-CFG   | Boolean Control Flow Graph         |  |  |  |  |

| DEP     | Data Execution Prevention          |  |  |  |  |

| ASLR    | Address Space Layout Randomization |  |  |  |  |

| CPU     | Central Processing Unit            |  |  |  |  |

| ALU     | Arithmetic-Logic Unit              |  |  |  |  |

| SIMD    | Single Instruction Multiple Data   |  |  |  |  |

| NX      | Non-Executable Memory              |  |  |  |  |

Table 1: List of Acronyms Used Throughout the Thesis

# **Contents**

| 1 | Intro | oduction                                 | 1  |

|---|-------|------------------------------------------|----|

|   | 1.1   | Problem Statement                        | 2  |

|   | 1.2   | Thesis Outline                           | 3  |

| 2 | Back  | eground                                  | 4  |

|   | 2.1   | Introduction to Low-Level Computing      | 4  |

|   | 2.2   | Computer Architecture                    | 4  |

|   | 2.3   | CPU Registers and their role in exploits | 5  |

|   | 2.4   | Memory and Addresses (Pointers)          | 6  |

|   | 2.5   | The Stack and Stack Frames               | 6  |

|   | 2.6   | Stack Alignment on x86-64 Systems        | 7  |

|   | 2.7   | Memory & Stack                           | 7  |

|   | 2.8   | Vulnerabilities                          | 7  |

|   | 2.9   | Buffer Overflow Vulnerabilities          | 8  |

|   | 2.10  | Exploits                                 | 8  |

|   | 2.11  | Return-Oriented Programming (ROP)        | 9  |

|   | 2.12  | Control-Flow Graphs (CFG)                | 10 |

|   | 2.13  | Boolean Networks                         | 11 |

| 3 | Lite  | rature Review                            | 13 |

|   | 3.1   | Control-Flow Hijacking Attacks           | 14 |

|   | 3.2   | ,                                        | 17 |

|   | 3.3   |                                          | 19 |

|   | 3.4   |                                          | 22 |

|   | 3.5   | •                                        | 24 |

|   | 3.6   |                                          | 25 |

| 4 | Met   | hodology                                 | 28 |

|   | 4.1   |                                          | 28 |

|   | 42    |                                          | 29 |

| Contents | vi |

|----------|----|

|          |    |

|     | 4.3   | Insulin-pump setup                        | 30  |

|-----|-------|-------------------------------------------|-----|

| 5   | Des   | ign                                       | 32  |

| _   | 5.1   | System Overview                           | 32  |

|     | 5.2   | Static Model Generation                   | 33  |

|     | 5.3   | Detection Engines and Runtime Flow        | 37  |

|     |       | O                                         |     |

|     | 5.4   | Log Architecture                          | 38  |

| 6   | Imp   | lementation                               | 41  |

|     | 6.1   | Rop Exploit construction                  | 41  |

|     | 6.2   | Exploratory Static Modeling Tools         | 43  |

|     | 6.3   | Address-based ROP Detection (ARD)         | 45  |

|     | 6.4   | ARD Runtime Attack Demonstration          | 50  |

|     | 6.5   | Boolean State Validation Detection (BSVD) | 55  |

|     | 6.6   | BSVD Runtime Attack Demonstration         | 59  |

|     | 6.7   | Hash-based Detection (PoC)                | 62  |

|     | 0.7   | That based Detection (100)                | 02  |

| 7   | Eval  | uation                                    | 64  |

|     | 7.1   | Objectives of Evaluation                  | 64  |

|     | 7.2   | Metrics and Results                       | 70  |

|     | 7.3   | Discussion                                | 77  |

| 8   | Con   | clusion                                   | 79  |

| 0   | Con   | Clusion                                   | 19  |

| 9   | Futu  | re Work                                   | 80  |

| Bil | oliog | raphy                                     | 82  |

| 10  | Apn   | endix                                     | 84  |

|     |       | Appendix A Code-implementation            |     |

|     |       |                                           |     |

|     | 10.2  | Prototype Call Graph Extraction Tools     | LU/ |

# Chapter 1

# Introduction

In the modern computing landscape, software is the backbone of digital infrastructure, but it is also a primary attack surface. Among the most insidious forms of threats are runtime software attacks, which manipulate program execution without injecting new code. Unlike traditional malware that drops executable payloads, runtime attacks work by hijacking the control flow of running programs through vulnerabilities like buffer overflows, use-after-free conditions, and memory disclosure. These exploits are especially difficult to detect, as they operate entirely within the bounds of existing executable memory and valid instructions.

A classic example is the Heartbleed vulnerability [2], which exploited a simple bound check error in the OpenSSL library to leak sensitive data from memory. Other advanced techniques, such as Return-Oriented Programming (ROP), chain together benign instruction sequences (called gadgets) already present in the binary to perform arbitrary computations. Such attacks bypass common defenses like Data Execution Prevention (DEP) and Address Space Layout Randomization (ASLR), posing severe challenges to traditional security mechanisms.

Runtime attacks are not limited to desktop or server environments – they pose a particular threat to embedded and IoT devices, such as medical controllers, which often lack advanced memory protection features. These resource-constrained systems are vulnerable due to hardcoded credentials, unsafe coding practices, and limited runtime verification. In safety-critical systems such as insulin pumps, the impact of a successful runtime attack can be catastrophic, affecting not just data confidentiality but also patient health.

1.1. Problem Statement 2

### 1.1 Problem Statement

Despite extensive academic and industry efforts, detecting runtime software attacks in a reliable and low-overhead manner remains an open challenge. Existing approaches like Control-Flow Integrity and Control-Flow Attestation either impose significant performance overhead or require hardware support not universally available in IoT systems.

This thesis investigates the feasibility of detecting runtime attacks through lightweight control-flow tracing, focusing on low-level, execution-time anomalies that can reveal malicious behavior without relying on deep symbolic reasoning or source code access. To evaluate this, a realistic and vulnerable target system – a simulated insulin pump – is constructed. A custom-made ROP exploit demonstrates how control flow can be hijacked to bypass privilege checks and invoke unauthorized actions.

Subsequently, the thesis introduces two original detection mechanisms:

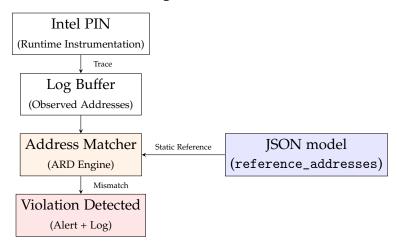

**Address-based ROP Detection (ARD)** – a monitor that validates RET instructions against statically extracted control-flow whitelists.

**Boolean State Validation Detection (BSVD)** – a novel Boolean control-flow graph abstraction that enables semantic enforcement of high-level program logic.

### 1.1.1 Research Areas

This thesis investigates three interrelated areas within the domain of runtime security for embedded systems. First, it examines how runtime software attacks are capable of subverting a program's control flow without injecting new code. This includes an analysis of techniques such as ROP and other code reuse strategies that rely on chaining existing instructions.

Second, the thesis explores the feasibility of designing and implementing a lightweight ROP detection mechanism. The proposed solution combines binary instrumentation with static analysis, aiming to provide practical runtime protection without imposing excessive overhead on resource-constrained systems.

Third, the effectiveness and efficiency of the proposed approach are evaluated. This includes measuring performance impact and analyzing detection accuracy in realistic embedded environments, where both computational resources and reliability requirements pose significant constraints.

Based on these areas, the research is guided by the following three questions:

- 1. How do runtime software attacks subvert control flow without injecting new code?

- **2.** Can a practical, lightweight ROP detection system be implemented using binary instrumentation and static analysis?

1.2. Thesis Outline

**3.** What is the performance impact and detection effectiveness of the proposed approaches in real-world embedded contexts?

### 1.2 Thesis Outline

This thesis is structured to provide a practical and technical investigation of runtime software attacks and their mitigation in embedded systems. Chapter 2 introduces essential background concepts such as memory layout, control-flow, and ROP techniques, while Chapter 3 reviews related work on control-flow hijacking and lightweight defenses. Chapters 4 and 5 cover the experimental setup and architectural design of our detection framework, including the use of static CFGs and Boolean modeling. Chapter 6 presents the implementation of a ROP exploit and two detection systems: Address-Based ROP Detection (ARD) and Boolean State Validation Detection (BSVD). Chapter 7 evaluates these techniques in terms of accuracy and performance overhead. Chapter 8 concludes the thesis with key findings, while Chapter 9 outlines future directions for extending the work. Chapter 10 contains appendices with supplementary implementation artifacts and scripts.

# Chapter 2

# Background

## 2.1 Introduction to Low-Level Computing

At their core, all computer programs, regardless of whether they are written in Python, C, or any other high-level language, must eventually be translated into machine instructions executed directly by the CPU. This translation process involves one or more intermediate stages, often producing assembly code, a low-level human-readable representation of machine instructions. The assembly language defines a link between source code and hardware behavior, exposing how instructions manipulate registers, memory, and control flow.

# 2.2 Computer Architecture

Modern processors still follow the classical fetch-decode-execute loop, yet the microarchitecture details are far from simple. Each core contains an Arithmetic-Logic Unit (ALU) for integer math, specialized floating-point and Single Instruction Multiple Data (SIMD) units, and a control engine that breaks complex instructions into smaller micro-operations. Deep pipelines and out-of-order execution keep these units busy by speculatively scheduling instructions; the same speculation famously underpins side-channel weaknesses such as Spectre and Meltdown.

Beneath the core, a hierarchical cache system (L1, L2, L3) hides main-memory latency, while the paging subsystem translates virtual to physical addresses in 4 KB blocks, known as memory pages. This granularity is significant because Address Space Layout Randomization (ASLR) shifts memory regions by page-aligned offsets, reducing the effective entropy of randomized addresses. As a result, attackers often exploit this predictability to perform partial address overwrites or brute-force aligned base addresses during ASLR bypass attempts.

Finally, the x86-64 privilege model separates the kernel code in ring 0 from the user code in ring 3. At its core, the x86-64 architecture defines four privilege levels, known as protection rings. Ring 0 represents the most privileged level and is reserved for kernel- and system-level code, while Ring 3 is used for user-space applications with limited access rights. A successful privilege-escalation exploit pivots execution from Ring 3 into Ring 0, effectively granting the attacker unrestricted control over the system by bypassing hardware-enforced isolation.

## 2.3 CPU Registers and their role in exploits

### 2.3.1 General Register Purpose and Layout

CPU registers are small high-speed memory cells within the processor that temporarily hold data, addresses, or control information. During execution, the CPU continuously loads data from memory into registers to perform operations efficiently.

The most relevant registers for the scope of understanding runtime attacks are:

**General-Purpose Registers** (rax, rbx, rcx, etc.): Used for arithmetic, logic, and data-transfer operations.

**Instruction Pointer (RIP)**: Stores the memory address of the next instruction to be executed. Manipulation of RIP directly (e.g., via a return address overwrite) is a core objective in most control-flow hijacking attacks.

**Stack Pointer (RSP)**: Points to the top of the stack, used to manage function calls and returns. Attackers often pivot or manipulate RSP to divert execution to attacker-controlled data.

**Base Pointer (RBP)**: Helps manage the current stack frame, often used to locate local variables relative to the frame.

### 2.3.2 Register Semantics in Runtime Attacks

Registers exist because even the fastest cache line costs several cycles to fetch, whereas data already sitting in a register can be consumed in the very next pipeline stage. On x86-64 the sixteen general-purpose registers (e.g., RAX, RBX), two dedicated stack/frame pointers (RSP, RBP), and the instruction pointer (RIP) are the usual protagonists in low-level exploits. Vector registers (XMM0-31, YMM, ZMM) power SIMD instructions and, by requiring 16-byte alignment, quietly motivate the stack alignment constraints discussed later. Gadgets such as pop RDI; ret load attacker-supplied values into these registers, so understanding what each one implicitly means for the ABI is a key element in building a viable ROP chain. Refer to section 2.6 for ABI documentation.

On x86-64 systems, the System-V AMD64 calling convention specifies that the first six function arguments are passed through registers in a specific order: rdi, rsi, rdx, rcx,

r8, and r9. This convention becomes crucial when constructing ROP chains intended to call system functions (such as execve or system). To do so successfully, attackers must use gadgets such as pop rdi; ret to place controlled values in these argument registers before triggering a function call. Thus, a deep understanding of register roles in the calling convention is essential to craft viable and reliable syscall-style payloads.

## 2.4 Memory and Addresses (Pointers)

Memory in modern computers is modeled as a linear array of storage locations, each with a unique address. Programs manipulate data through these memory addresses, with pointers acting as variables specifically designed to store them. In high-level programming, pointers are mainly used for dynamic memory management and for interaction with data structures like linked lists or trees. However, at a low level, pointers are the mechanism by which functions, variables, and even executable instructions are located and accessed.

For attackers, pointers represent a crucial target: By manipulating pointers, they can redirect the control flow of a program to unintended memory regions (such as injected shell-code or ROP chains). The following simple C snippet shows how a pointer references the memory location of a variable:

```

int number = 5; int *pointer = &number;

```

In exploitation, this same principle is abused to overwrite pointers (e.g., function pointers, return addresses) to control where the CPU will execute next.

### 2.5 The Stack and Stack Frames

The stack is a structured memory region designed to support function calls and local variable storage. It follows a Last-In-First-Out (LIFO) discipline where data is "pushed" onto the stack when a function is called and "popped" off when it returns.

Each function call generates a stack frame containing:

Local variables,

**Saved base pointer (RBP)** of the previous frame,

The return address, where execution resumes after the function finishes.

An attacker exploiting a stack-based vulnerability (e.g., Buffer Overflow 2.9) aims to overwrite data in the current frame, particularly the return address, which will eventually be popped into RIP, directing execution elsewhere.

## 2.6 Stack Alignment on x86-64 Systems

On the x86-64 architecture, the ABI specifies that the stack must be 16-byte aligned before invoking functions like system() or standard library calls. Misaligned stacks can cause crashes or unpredictable behavior, as many system instructions assume proper alignment (e.g., SIMD instructions like movaps).

In real-world exploits, attackers often compensate for alignment issues by inserting "dummy" ret gadgets into their ROP chains to adjust the RSP register, restoring the required 16-byte alignment before transferring control to sensitive library functions.

Without maintaining proper alignment, the crafted payload might fail due to alignment checks or segmentation faults.

## 2.7 Memory & Stack

A UNIX or Windows process presents a split personality: From the programmer's perspective, it is a flat address space, but underneath it is divided into segments. Executable instructions live in a read-only text segment; constants follow in rodata; global variables occupy data and bss; dynamic allocations grow upward from the heap; and the call stack grows downward from high addresses. Because every segment is mapped through page tables, an attacker who can leak page-aligned addresses or spray entire pages can erode Address-Space Layout Randomization.

The stack itself is managed by the RSP register. When entering a function, the compiler usually pushes the old base pointer, sets RBP := RSP, and then subtracts the space for local variables. Overwriting data inside that reserved window, say, by copying unchecked input into a fixed-sized array, lays the groundwork for a classic stack-smash.

### 2.8 Vulnerabilities

Security-critical software flaws in native code fall into four broad families. Spatial memory-safety bugs write or read past an object's boundary, overrunning buffers, or indexing arrays out of bounds. Temporal bugs misuse objects after their lifetime ends, leading to use-after-free or double-free conditions. Type-safety violations reinterpret a representation under the wrong signedness or structure, while pure logic errors omit or misorder essential checks.

Consider a simple example:

```

char name[16];

strcpy(name, argv[1]); // length not checked

```

If the attacker supplies more than fifteen bytes, the overrun first tramples on the saved base pointer and then the return address, an almost textbook gateway to control-flow hijacking.

### 2.9 Buffer Overflow Vulnerabilities

A buffer overflow occurs when more data is written to a memory buffer than it can accommodate. Since C and assembly do not inherently perform boundary checks on buffer sizes, a poorly validated input can lead to adjacent memory regions being overwritten.

This becomes critical when the overflow affects sensitive data such as:

Return addresses,

Function pointers,

Local variables controlling program logic

The following example is a local buffer on the stack, where overflowing data can overwrite the return address:

```

char buffer[10]; gets(buffer);

```

This is dangerous since the function "gets()" allows for unlimited input size.

By providing crafted input, an attacker can overwrite the saved return address with the location of injected shellcode or a "ROP chain".

## 2.10 Exploits

Turning a vulnerability into an exploit is an engineering process. First, the attacker needs a trigger: a way to reach the buggy code path with data of their choosing. Next comes corruption: overwriting or disclosing the right words in memory to gain influence over execution. If the goal is code execution rather than mere data corruption, the attacker must seize control flow, typically by replacing a return address or function pointer with an attacker-selected destination such as injected shellcode, a libc function, or a crafted ROP chain. A payload then executes: spawning a shell, escalating privileges, or exfiltrating secrets. Finally, sophisticated intrusions install persistence or wipe forensic traces, though that last step lies outside the scope of most academic proof-of-concepts.

Classic payload styles include direct code injection (effective on systems without DE-P/NX), return-to-libc calls that reuse trusted code, gadget-chaining techniques such as ROP and JOP that bypass nonexecutable memory, and pure data-only attacks that flip security-critical flags while leaving control flow intact.

## 2.11 Return-Oriented Programming (ROP)

"ROP" is a post-buffer overflow exploitation technique that bypasses memory protections such as non-executable stacks (DEP/NX). Instead of injecting new executable code, the attacker reuses ("recycles") existing executable code fragments, called gadgets, within the target binary or its libraries.

Each gadget is a short instruction sequence (for example, pop rdi; ret) that ends with a ret instruction, causing the control to return to the next gadget on the stack. By chaining these gadgets, an attacker can construct arbitrary computation ("Turing-complete" payloads), ultimately leading to actions such as spawning a shell or disabling security mechanisms.

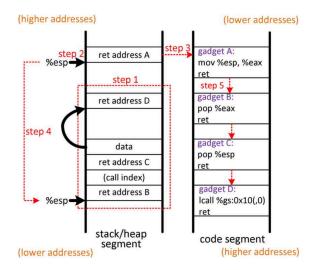

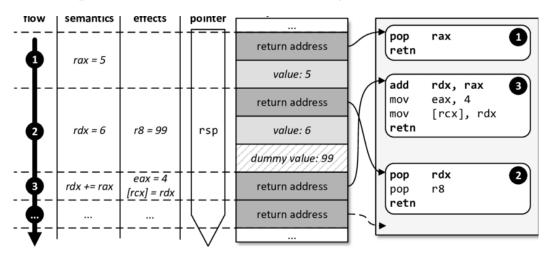

Figure 3.1 illustrates a classic (ROP) attack. In This attack, each gadget ends with a RET instruction, allowing the attacker to link them through crafted return addresses on the stack.

Figure 2.1: An example of a Return-Oriented Programming (ROP) attack. Adapted from [11]

**Step 1:** The attacker places a sequence of gadget return addresses onto the stack (e.g., RET address B, RET address C, etc.), effectively creating a malicious execution path.

**Step 2:** Through an exploit (e.g. buffer overflow), the stack pointer %esp is redirected to the point at the start of this designed ROP chain.

**Step 3:** The program executes a ret instruction that fetches the first gadget address from the stack and transfers control to gadget A.

**Step 4:** Gadget A runs a benign instruction (e.g., mov %esp, %eax) and ends with a RET, which pops the next address from the stack.

**Step 5:** The process continues with gadgets B, C, and D. Each gadget performs a simple operation and returns, causing execution to flow through the attacker's desired path without injecting new code.

## 2.12 Control-Flow Graphs (CFG)

"CFG" represents the spatial structure of a program's machine code. It is a directed graph G = (V, E), where each vertex corresponds to a "basic block", a maximal sequence of instructions that is entered only at the beginning and exited only at the end. The edges in the graph represent possible control flow transitions between basic blocks.

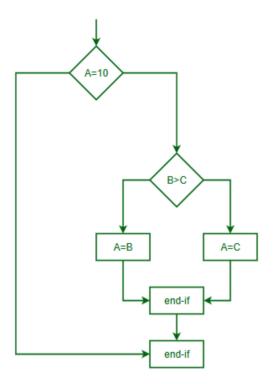

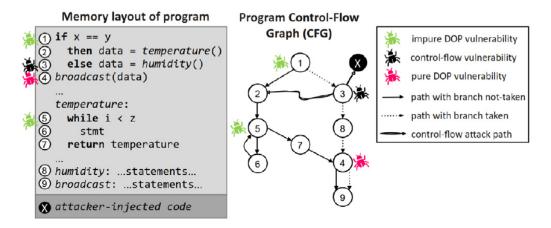

Figure 2.2: Control Flow Graph (CFG) representing conditional logic. Adapted from [9].

Figure 2.2 shows a CFG, a directed graph that is used to represent the flow of control in a program. Each node in the graph denotes a basic block (a straight-line code sequence without branches), and the edges represent possible control flow paths based on conditional decisions.

The graph starts with a decision node that checks if A = 10.

If false, the control flows to a nested condition that checks if  $\mathbf{B} > \mathbf{C}$ .

Based on the result, one of two assignments is executed:

2.13. Boolean Networks

If

$$B > C$$

, then  $A = B$ .

Else,  $A = C$ .

After executing either assignment, control converges at an end-if node and continues to the final end-if node.

If the first condition (A = 10) was true, the control loops back without entering the nested decision structure.

Construction and granularity. Compilers build a CFG during the very first stages of optimization. Straight-line sequences become nodes; conditional jumps, indirect branches, and call/return pairs become edges. For dynamic analyses, the graph is refined at runtime by instrumenting branch targets, turning theoretical possibilities into observed paths, an important distinction when an exploit relies on rarely executed error handling code.

**Static reachability, dominators, and loops.** Static data-flow frameworks treat the CFG as the carrier of information for liveness, alias analysis, and, in our security context, taint propagation. Dominators identify blocks that must be traversed before reaching a given node, making them natural choke points for mitigations, such as stack canaries. Backedges mark natural loops and therefore potential iteration counts: if a buffer write sits inside such a loop, the maximum overflow length may depend on the loop bound.

CFG in exploitation. Attackers exploit two CFG-centred observations. First, if they can redirect RIP to any instruction that ends a basic block with a direct ret, they effectively move along an existing edge, blending with legitimate control flow, a principle at the heart of ROP. Second, coarse-grained Control-Flow Integrity approximates the legal CFG too conservatively; edges that cannot occur in the compiled program are left in place, providing the attacker with "shadow" transitions that can still be reached under runtime corruption.

From graphs to mitigations. Fine-grained Control-Flow Inegrity tightens the legal edge set to the exact CFG emitted by the compiler, raising the bar for gadget chaining. Hardware vendors experiment with enforcing this policy at the instruction decode stage (control flow enforcement technology, ARM branch target identification), showing that the concept of CFG spans software, microarchitecture, and formal verification alike.

### 2.13 Boolean Networks

Where CFG captures the spatial structure of machine code, Boolean networks are discrete dynamical systems that model the evolution of binary-valued systems over time, where each component (or node) updates its state according to a Boolean function of other components. These models, originating in circuit theory and biology, are increasingly applied to security-critical system behaviors

2.13. Boolean Networks 12

global state at time t is a vector  $\mathbf{x}(t) = (x_1(t), \dots, x_n(t)) \in \{0, 1\}^n$ . Each component  $x_i$  represents a binary variable, typically corresponding to a logic signal in a digital circuit or the activity state of a gene. Its value is updated according to a Boolean function:

$$x_i(t+1) = f_i(x_{j_1}(t), \dots, x_{j_{k_i}}(t)), \qquad f_i : \{0,1\}^{k_i} \longrightarrow \{0,1\}.$$

**Synchronous versus asynchronous evolution.** In a synchronous discipline, every node evaluates its update function against the same snapshot  $\mathbf{x}(t)$ , reproducing the behavior of a clocked sequential circuit. In an asynchronous discipline only a subset of nodes, often exactly one chosen non-deterministically-updates per step, giving rise to a richer state transition graph that models biological timing noise and hardware glitches.

Attractors and safety properties. Because the state space is finite, iterating the global update map  $F: \{0,1\}^n \to \{0,1\}^n$  eventually enters a cycle. Fixed points correspond to stable operating modes (e.g. "CPU idle", "gene off"), whereas longer cycles model oscillators or multiphase control logic. From a security perspective, proving that no input can steer the network into an unsafe attractor is tantamount to proving that a hardware pipeline cannot leak data after a speculative misprediction.

A minimal worked example. Consider the three-node network

$$x_1(t+1) = \neg x_3(t),$$

$x_2(t+1) = x_1(t) \land x_3(t),$

$x_3(t+1) = x_2(t).$

Clocked synchronously and starting from (0,0,0), the trajectory is  $(0,0,0) \rightarrow (1,0,0) \rightarrow (1,0,0)$ , hitting the fixed point (1,0,0) in two steps. Re-running the same logic asynchronously may reveal extra paths and even new attractors, illustrating how update discipline affects reachability analysis.

Why include Boolean networks in a low-level thesis? Modern side-channel and speculative execution defenses are increasingly verified with formal Boolean-level models. Expressing pipeline stages, hazard detectors, and privilege checks as a Boolean network provides a language in which information-flow security reduces to a reachability query, which is conceptually identical to proving the absence of an unsafe attractor.

Boolean networks offer a formalism well suited for verifying information-flow properties and control invariants in low-level systems. For example, modern speculative execution defenses and hardware privilege checks are increasingly modeled using Boolean-level abstractions. By framing a control-flow violation or security breach as a reachability query in a Boolean state space, these models provide a rigorous basis for detecting and preventing runtime misbehavior.

# Chapter 3

# Literature Review

Securing modern computing systems against runtime attacks has become increasingly critical as cyber threats evolve. Prominent runtime attack techniques include ROP, JOP, and Call-Oriented Programming (COP), which fall under the category of code-reuse attacks. These methods enable attackers to chain existing instruction sequences to perform malicious operations without introducing new code.

Research has extensively analyzed runtime attacks and proposed numerous countermeasures. However, memory corruption vulnerabilities such as buffer overflows and use-after-free exploits remain widely abused. Defenses range from software-based mechanisms to hardware-assisted solutions, but practical deployment remains a challenge.

This literature review explores state-of-the-art research on runtime attacks and defenses, organized thematically rather than by individual studies. Key focus areas include

Control-Flow Hijacking Attacks

Memory Corruption Vulnerabilities

Control-Flow Integrity and Attestation

ROP Techniques

Runtime Security in IoT Devices

Limitations and Open Challenges

This thematic approach offers a coherent understanding of attack methodologies, defense mechanisms, and remaining gaps in runtime security. The next section examines control-flow hijacking techniques and their impact on software security.

### 3.1 Control-Flow Hijacking Attacks

Control-flow hijacking is a critical category of runtime attacks that allows adversaries to manipulate the execution flow of a program without injecting new code. By exploiting memory corruption vulnerabilities, attackers can redirect execution to unintended instruction sequences, effectively bypassing security mechanisms. Over the years, these attacks have evolved, becoming more sophisticated and resistant to traditional defenses.

### 3.1.1 Evolution of Control-Flow Hijacking

Initially, attackers relied on direct code injection techniques, inserting malicious code into writable memory regions. However, the introduction of DEP rendered this approach ineffective by marking memory pages as nonexecutable. This led to the rise of code-reuse attacks, in which adversaries exploit existing executable code to perform malicious actions.

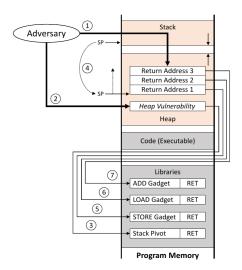

One of the most prevalent code-reuse techniques is ROP, in which attackers bundle short instruction sequences that end in a return instruction [3]. As illustrated in Figure 3.1, ROP attacks pivot execution flow by chaining gadgets to construct an arbitrary execution sequence. As mentioned earlier, ROP allows adversaries to execute arbitrary computations without injecting new code, effectively circumventing DEP. Attackers locate useful gadgets in shared libraries or executables and construct sequences that perform operations such as stack pivoting, function pointer overwriting, and privilege escalation.

Figure 3.1: Illustration of a ROP attack chaining.

In this figure, the adversary exploits a heap vulnerability (step 1–2) to pivot the stack pointer (SP) to a malicious ROP chain prepared in memory (step 3–4). This chain contains return addresses pointing to instruction sequences, or gadgets, located in shared libraries

(steps 5–7). Each gadget performs a specific operation and ends with a ret instruction, allowing the attacker to execute arbitrary logic without injecting new code. This technique effectively bypasses non-executable memory protections such as Data Execution Prevention.

To counteract ROP, defenses such as shadow stacks and return address validation were introduced. However, attackers adapted by developing JOP and COP, which avoid reliance on return instructions and instead manipulate indirect jumps and function calls to hijack execution flow [10].

### 3.1.2 Memory Disclosure and Just-In-Time Attacks

A crucial enabler of modern control-flow hijacking is memory disclosure vulnerabilities. These vulnerabilities allow attackers to leak runtime memory layouts, bypassing ASLR. By leveraging memory leaks, attackers can locate executable regions of memory, making ASLR ineffective in preventing exploitation.

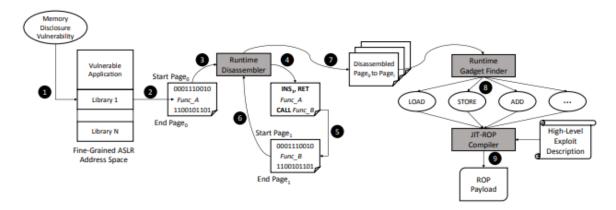

A particularly advanced variant of ROP is Just-In-Time Return-Oriented Programming (JIT-ROP), where attackers dynamically construct ROP chains at runtime based on leaked memory addresses [13]. JIT-ROP differs from traditional ROP in that:

**Gadgets** are discovered dynamically instead of being predefined.

**Attackers** use runtime analysis to find executable pages and create exploit chains.

**JIT compilers**, commonly found in web browsers and scripting environments, are frequently targeted since they generate new executable memory at runtime.

Figure 3.2 illustrates the workflow of a JIT-ROP attack, demonstrating how attackers leverage memory disclosure vulnerabilities to dynamically generate gadget chains. This technique significantly reduces the effectiveness of ASLR, as gadgets are identified on-the-fly rather than relying on predetermined memory locations. Attackers often pair JIT-ROP with side-channel analysis to precisely map executable code regions and launch runtime exploits.

**Figure 3.2:** provides an overview of the JIT-ROP workflow, highlighting how attackers dynamically construct gadget chains in real-time.

### 3.1.3 Defensive Mechanisms Against Control-Flow Hijacking

Several defensive mechanisms have been introduced to mitigate control-flow hijacking attacks, each providing varying levels of protection, often with an associated performance cost. One of the foundational defenses is DEP, which enforces non-executable memory policies to prevent attackers from injecting and directly executing code in writable regions such as the stack or heap. However, DEP is ineffective against code reuse attacks such as ROP, JOP, and COP, where existing executable code within the program or linked libraries is leveraged to bypass this restriction [4].

To complement DEP, systems also implement ASLR, which randomizes the placement of executable code, libraries, and stack frames in memory to hinder an attacker's ability to predict code locations. Although ASLR has proven effective in many scenarios, it can be circumvented by memory disclosure vulnerabilities, such as heap spraying or relative memory leaks, which reveal enough of the randomized memory layout for the attacker to mount a successful exploit [5].

Control-Flow Integrity introduces a more systematic defense by restricting the program's control flow to a predefined graph determined at compile time. This helps prevent attackers from executing arbitrary control-flow transfers. However, while fine-grained Control-Flow Integrity can substantially reduce the attack surface, many implementations in the real world are coarse-grained, making them susceptible to control-flow bending attacks, where an attacker stays within the allowed control-flow graph but executes logic in an unintended and malicious way [12].

In addition, Execute-Only Memory (XOM) has emerged as a mitigation strategy that prevents the reading of executable code sections by user-space processes. By making code memory unreadable, XOM reduces the effectiveness of information disclosure attacks, which are often used to find ROP gadgets or function addresses. However, XOM requires

substantial hardware and compiler support to be fully effective, limiting its deployment in some environments [13].

Finally, newer architectures, such as ARMv8.3 +, have adopted pointer authentication (PAC). PAC leverages cryptographic signatures (PAC codes) to protect control-flow elements such as function pointers and return addresses from unauthorized modifications. By validating these signatures before use, PAC significantly increases the difficulty of successfully executing traditional ROP and JOP attacks on supported hardware platforms [14].

Despite advances in defensive techniques, control flow hijacking remains a key research challenge due to evolving attack methodologies. Attackers continuously refine their exploitation strategies, leading to an ongoing arms race between security researchers and adversaries. The next section will discuss memory corruption vulnerabilities, which are the basis for many runtime attacks.

## 3.2 Memory Corruption Vulnerabilities

Memory corruption vulnerabilities form the foundation for many control-flow hijacking attacks, allowing attackers to manipulate program execution by exploiting unsafe memory operations. These vulnerabilities are particularly prevalent in low-level programming languages such as C and C++, which lack built-in memory security mechanisms. Exploiting memory corruption often leads to arbitrary code execution, privilege escalation, or unauthorized access to sensitive data [12].

### 3.2.1 Common Types of Memory Corruption

Several types of memory corruption vulnerabilities – most notably buffer overflows – have been extensively studied in the context of runtime attacks and control-flow hijacking. In stack-based buffer overflows, attackers can overwrite critical data such as return addresses, control data, and function pointers to redirect the program's execution flow [13]. Closely related are Heap-based Overflows, which target dynamically allocated memory on the heap. These vulnerabilities enable attackers to corrupt the metadata structures used by memory allocators, facilitating the execution of arbitrary code through techniques such as heap exploitation [13].

Another prevalent vulnerability is the use-after-free (UAF), which arises when a program accesses memory after it has already been deallocated. Attackers can exploit this by reclaiming the freed memory block and injecting malicious payloads, leading to unauthorized control-flow transfers [14]. Format string vulnerabilities are another class of flaws that occur when user-controlled input is unsafely passed to formatted output functions such as printf(). These vulnerabilities allow attackers to read or write arbitrary memory addresses, posing significant security risks [22].

Finally, Integer Overflows and underflows occur when arithmetic operations exceed or fall below the storage capacity of a variable, often resulting in incorrect memory allocations or faulty pointer arithmetic. These conditions can be exploited to trigger buffer overflows or to bypass bounds checks within the program [22]. Each of these vulnerabilities provides an entry point for attackers to apply advanced exploitation techniques such as ROP, JOP, or heap spraying to hijack the program control flow.

### 3.2.2 Exploitation Techniques

Memory corruption vulnerabilities are exploited through a variety of techniques to gain control over the execution flow of a program. One of the most well-known techniques is stack-based buffer overflow, where attackers overwrite return addresses stored on the stack to redirect execution to attacker-controlled code or existing executable code within the program's memory, such as ROP chains [23]. In parallel, Heap exploitation targets the dynamic memory region of a process by corrupting heap management structures, such as malloc and free metadata, to overwrite adjacent memory or manipulate function pointers, leading to the execution of arbitrary code [23].

Another prominent strategy is pointer subversion, where attackers hijack control flow by modifying sensitive control-flow objects, including function pointers, virtual table entries (vtables), or exception handlers. This technique is frequently used in modern exploits to bypass mitigations such as Control-Flow Integrity, which aim to restrict indirect control transfers [24]. Furthermore, heap spraying is often employed as a preparatory step, where attackers fill large portions of the heap with predictable, attacker-controlled data. This increases the probability that an overflow or a UAF condition will cause execution to land within the sprayed region, facilitating exploitation [24].

These exploitation techniques have evolved alongside the development of defensive mechanisms. As mitigations such as DEP, ASLR, and Control-flow Integrity have become more widespread, modern attackers frequently employ multistage exploits that combine memory disclosure, heap manipulation, and control flow hijacking to reliably achieve execution control even in hardened environments.

### 3.2.3 Mitigation Strategies

To counteract memory corruption vulnerabilities, a range of mitigation strategies have been proposed and widely deployed. One common technique is the use of stack canaries, which are special guard values inserted between local variables and return addresses. If a buffer overflow occurs, a corrupted canary value can be detected, preventing control-flow redirection. However, canaries can be bypassed if an attacker can leak stack memory and predict their value [25].

In addition, defenses such as ASLR, DEP, and Control-Flow Integrity are widely used

(see Section section 3.5). Although these techniques provide baseline protection, they are frequently circumvented through code reuse and memory disclosure attacks.

More recent solutions include Pointer Authentication Codes (PAC) and memory tagging, which introduce hardware-assisted protections for pointers and memory integrity, particularly in ARM architectures. Finally, bounds checking and safe memory allocators such as PartitionAlloc and Hardened Malloc help mitigate heap-based exploits by enforcing stricter memory access policies [25].

Despite these advancements, memory corruption remains a persistent security challenge due to evolving exploitation strategies and limitations in defense scalability.

The following section will focus on Control-Flow Integrity and attestation as advanced methods to further improve runtime security.

## 3.3 Control-Flow Integrity and Attestation

Control-Flow Integrity is a fundamental security mechanism designed to prevent control-flow hijacking attacks by enforcing legitimate execution paths within a program. It ensures that indirect control transfers follow predefined control-flow edges, significantly reducing the effectiveness of ROP, JOP and COP attacks [22]. Figure 3.3 visually represents different control-flow attack vectors, categorizing various hijacking techniques.

Figure 3.3: visually represents different control-flow attack vectors, demonstrating how control and data manipulation techniques can be exploited.

### 3.3.1 Principles of Control-Flow Integrity

The fundamental principle behind Control-Flow Integrity is the creation of a CFG during compile time, which models all valid control-flow transfers within a program. At runtime,

indirect control transfers, such as function pointer calls or returns, are checked against the permitted edges in the CFG to detect and block unauthorized deviations from the intended execution flow [22]. Control-Flow Integrity implementations generally fall into two categories depending on the granularity of enforcement.

Coarse-grained Control-Flow Integrity enforces broader control-flow policies by permitting larger sets of valid control-flow transfers. This approach reduces performance overhead but leaves room for attacks such as control-flow bending, where adversaries stay within the permitted control-flow graph but still execute unintended code paths [22]. In contrast, fine-grained Control-Flow Integrity applies stricter constraints to each indirect control transfer, significantly reducing the attack surface by allowing only narrowly defined control-flow edges. However, this comes at the cost of higher computational overhead and a more complex implementation [22].

Although Control-Flow Integrity remains an effective mitigation against traditional control-flow hijacking techniques such as ROP or JOP, attackers have developed sophisticated evasion strategies. In particular, control-flow bending allows adversaries to remain within the bounds of a coarse-grained CFG while still abusing valid program logic to achieve malicious objectives [22].

#### 3.3.2 Control-Flow Attestation and Remote Verification

Control-Flow Attestation extends Control-Flow Integrity principles by enabling remote verification of a system's execution flow. Figure 3.4 compares key features of different Control-Flow Integrity techniques, illustrating their respective advantages and weaknesses. This is particularly useful for security-critical environments such as IoT and cloud computing, where external verifiers need assurance that a device has followed the expected execution path [24].

Control-Flow Attestation techniques include: **1. Hash-Based Attestation**: Computes and transmits cumulative hashes of executed control-flow events to detect deviations [24]. **2. Execution Path Logging**: Stores control-flow transitions for later analysis, allowing detection of anomalies in execution patterns [24]. **3. Whitelist-Based Enforcement**: Ensures that only predefined control-flow paths are executed, rejecting any unauthorized deviations [24].

Recent advancements in hardware security have introduced features such as Intel Control-Flow Enforcement Technology (CET) and ARM Pointer Authentication (PA) to enhance the enforcement of control-flow integrity at the processor level [24].

| CFI<br>Techniques | Base<br>HW | d on<br>SW | Compiler<br>Modified | Shadow<br>Stack | CFG | Label | Coarse<br>Grained | Fine<br>Grained | Backward<br>Edge | CFI<br>Enforcement      |

|-------------------|------------|------------|----------------------|-----------------|-----|-------|-------------------|-----------------|------------------|-------------------------|

| CFI1 [51,52]      |            | 1          |                      | 1               | 1   | 1     | 1                 |                 | 1                | Inlined CFI             |

| CCFI [46]         | 1          | 1          | 1                    |                 |     |       |                   | 1               | 1                | Dynamic Analysis        |

| binCFI [42]       |            | 1          |                      |                 |     | 1     | ✓                 |                 |                  | Static Binary Rewriting |

| CCFIR [59]        |            | 1          |                      |                 |     | 1     | ✓                 |                 | ✓                | Binary Rewriting        |

| HW-CFI [41]       | 1          | 1          | 1                    | 1               | /   | ✓     |                   | 1               | ✓                | Landing Point           |

| PICFI [44]        |            | 1          | ✓                    |                 | /   |       |                   | 1               | ✓                | Static Analysis         |

| KCoFI [61]        |            | 1          | 1                    |                 |     | /     | ✓                 |                 | 1                | SVA Instrumentation     |

| Kernel CFI [62]   |            | 1          |                      |                 | 1   |       |                   | 1               | ✓                | Retrofitting Approach   |

| IFCC [43]         |            | 1          | 1                    |                 | 1   |       |                   | 1               |                  | Dynamic Analysis        |

| CFB [45]          |            | 1          |                      | 1               | 1   |       |                   | 1               | 1                | Precise Static CFI      |

| SAFEDISPATCH [65] |            | 1          | 1                    |                 |     |       | ✓                 |                 |                  | Static Analysis         |

| C-Guard [66]      |            | 1          | 1                    |                 | 1   |       | ✓                 |                 |                  | Dynamic Instrumentation |

| RAP [49]          |            | 1          | 1                    |                 | 1   |       |                   | 1               | ✓                | Type Based              |

| O-CFI [47]        | 1          | 1          |                      |                 |     |       | ✓                 | 1               | ✓                | Static Rewriting        |

**Figure 3.4:** compares key features of different Control-Flow Integrity techniques, illustrating their effectiveness and weaknesses in various environments.

# 3.3.3 Challenges and Limitations of Control-Flow Integrity and Control-Flow Attestation

Although Control-Flow Integrity and Control-Flow Attestation offer robust security guarantees against control-flow hijacking, several inherent challenges limit their practical deployment. One of the primary concerns is performance overhead, especially with finegrained Control-Flow Integrity implementations, which introduce noticeable execution latency. This can make Control-Flow Integrity unsuitable for performance-critical applications, such as real-time embedded systems, where low-latency execution is essential [22]. Furthermore, bypass techniques have emerged, demonstrating that attackers can still circumvent Control-Flow Integrity protections using methods such as memory disclosure vulnerabilities and control-flow bending. These techniques allow adversaries to exploit the logic of unintended programs while staying within the legitimate boundaries defined by the control-flow graph [22].

Scalability also poses a challenge, particularly for Control-Flow Attestation solutions designed to support remote attestation. Logging every control-flow transition or execution step can introduce significant storage and computational overhead, making Control-Flow Attestation less feasible for resource-constrained devices or large-scale deployments [24]. As shown in Table 3.1, existing Control-Flow Integrity techniques present a trade-off between security strength and runtime efficiency, shedding light on the complexity of adopting these defenses in various computing environments.

The next section will examine ROP and its implications for control-flow defenses.

| CFI Technique                              | Security Strength | Overhead | Bypassability            |

|--------------------------------------------|-------------------|----------|--------------------------|

| CCFI (Cryptographic CFI)                   | High              | 52%      | Replay attacks           |

| BinCFI (CFI for COTS Binaries)             | Moderate          | 15%      | Gadget Synthesis         |

| CCFIR (Randomization-based CFI)            | Moderate          | 8.6%     | Code Disclosure Attacks  |

| KCoFI (Kernel-Level CFI)                   | High              | 27%      | Memory Disclosure Bypass |

| IFCC (Forward-Edge CFI in LLVM)            | Moderate          | 5%       | Control Jujutsu Attack   |

| SAFEDISPATCH (C++ Virtual Call Protection) | Low               | 2.1%     | Vtable Hijacking         |

| RAP (Reuse Attack Protector)               | High              | 6.2%     | ret2usr Attack           |

**Table 3.1:** presents a security and performance evaluation of different Control-Flow Integrity techniques, highlighting their trade-offs.

## 3.4 ROP Techniques

ROP has been extensively studied due to its potent capability to bypass modern memory protection mechanisms such as DEP and ASLR. DEP marks memory regions (e.g., the stack or heap) as non-executable, aiming to prevent code injection attacks. However, ROP circumvents DEP by reusing existing executable code snippets (gadgets) already loaded in memory. Similarly, ASLR randomizes the memory layout of a process to prevent attackers from reliably predicting the location of code. However, ROP can still function by leveraging information leaks or side channels to locate gadgets dynamically [4].

### 3.4.1 Evolution of ROP Attacks

ROP emerged as a response to modern security mechanisms that prevent direct code injection. By chaining together existing instruction sequences that end with a return instruction, attackers manipulate the execution flow while avoiding detection [4].

**Figure 3.5:** illustrates execution constraints for ROP on x86\_64 architectures, detailing register dependencies and stack behavior

3.4. ROP Techniques

Figure 3.5 illustrates execution constraints for ROP on x86\_64 architectures, emphasizing the importance of register dependencies and stack manipulation in successful exploitation. Over time, ROP techniques have evolved significantly, resulting in various refinements tailored to overcome modern defensive mechanisms.

The original form, known as traditional ROP, involves chaining short instruction sequences, called gadgets, each ending with a RET instruction, to perform arbitrary computations by carefully controlling the stack [4]. Building on this foundation, attackers developed Sigreturn-Oriented Programming (SROP), which abuses system call return mechanisms to manipulate execution state and bypass certain Unix-based signal handling defenses [4]. More recently, JIT-ROP techniques have emerged that dynamically discover and construct ROP chains during run-time. JIT-ROP leverages memory disclosure vulnerabilities to bypass protections such as ASLR, assembling functional ROP chains even in hardened environments [4].

Each of these advancements has improved ROP's adaptability, making it one of the most persistent and evolving exploitation techniques.

### 3.4.2 Automated ROP Chain Generation

To streamline the creation of ROP payloads, attackers employ various tools that automate the process of discovering and chaining gadgets. Some of the most widely used tools include: **1. ROPgadget**: A framework that identifies useful gadgets within binary files, allowing attackers to automate the construction of ROP chains [5]. **2. ROPme**: A tool that generates optimized ROP payloads based on predefined exploitation goals [5]. **3. QROP**: An advanced tool that selects the most efficient ROP gadgets to evade detection mechanisms [5].

These automation techniques have significantly contributed to the prevalence of ROP-based attacks despite ongoing security improvements.

### 3.4.3 Bypassing Modern Defenses

As defensive mechanisms against ROP have become more sophisticated, attackers have responded by developing advanced techniques to bypass these protections. One such method is ROP chain obfuscation, where attackers modify the structure of gadget sequences to evade signature-based detection systems. By introducing variations in gadget order, using uncommon instructions, or inserting benign-looking operations, attackers can make ROP payloads harder to detect through static or heuristic analysis [10].

Another evasion strategy involves ROP combined with COP. In this approach, traditional ROP chains are blended with legitimate function call redirections to circumvent Control-Flow Integrity checks. COP takes advantage of the fact that some Control-Flow Integrity

implementations allow indirect calls to valid functions, allowing attackers to hijack control flow while still adhering to the constraints of coarse-grained Control-Flow Integrity policies [10].

Additionally, attackers have leveraged ROP techniques within Just-In-Time (JIT) environments by exploiting JIT compilation to introduce new gadgets at runtime. Since JIT compilers generate machine code on the fly, attackers can manipulate JIT-compiled code regions to create custom gadgets dynamically, effectively bypassing static analysis defenses and layout randomization schemes [10].

Despite these advanced evasion strategies, ROP and related exploitation techniques remain highly effective, particularly in environments with limited resources and limited defenses. IoT devices, due to their architectural limitations and deployment contexts, are especially vulnerable to such attacks. The following section will examine the unique runtime security challenges faced by IoT platforms and embedded systems.

### 3.5 Runtime Security for IoT Devices

The enormous growth of the Internet-of-Things (IoT) has exposed millions of small, network-connected devices to adversaries who routinely exploit runtime software vulnerabilities. Compared to desktop or cloud platforms, IoT nodes tend to ship with minimal CPU and memory budgets, immature update mechanisms, and limited hardware protection features. These factors combine to create an attractive attack surface for memory-corruption and control-flow hijacking exploits that can culminate in persistent firmware compromise [12].

### 3.5.1 Constraints That Amplify Risk

Three structural constraints dominate IoT security. First, tight resource envelopes exclude heavyweight defences such as fine-grained Control-Flow Integrity or full ASLR [13]. Second, the firmware life cycle is often weakly protected: bootloaders are rarely verified, update channels lack proper authentication, and rollback countermeasures are rare, enabling durable firmware implants or remote downgrades,[14]. Third, commodity hardware safeguards – Intel Control-Flow Enforcement Technology (CET), ARM Pointer Authentication Codes (PAC), or even simple eXecute-Only Memory (XOM – are either absent or disabled in most commodity IoT microcontrollers, leaving them vulnerable to classic code-reuse attacks such as ROP and JOP [22]. The situation is exacerbated by the fact that devices typically operate in untrusted networks, giving attackers continuous opportunities for remote code-execution attempts and side-channel surveillance.

### 3.5.2 Typical Runtime Exploits

Runtime exploits on IoT platforms usually rely on memory-corruption bugs. By overwriting forward or backward control-flow edges, an adversary can assemble ROP or JOP chains directly from the existing firmware image or linked libraries. Just-in-time ROP refines this idea by leaking code pointers at runtime, which nullifies coarse ASLR and enables gadget discovery on the fly [13]. Code-reuse in general remains attractive because Data-Execution Prevention (DEP) is either missing or disabled on many microcontrollers. Beyond transient memory attacks, insecure update paths enable direct firmware tampering: once an attacker injects a malicious image, it survives reboots and grants long-term footholds on the target network,[22].

### 3.5.3 Mitigation Strategies Under Resource Constraints

Robust defences must therefore deliver meaningful coverage without violating the tight performance and energy budgets of embedded systems. Secure-Boot frameworks, often paired with lightweight Trusted Execution Environments (TEEs), ensure that only authenticated code reaches runtime and that secrets remain isolated during execution,[23]. On the control-flow side, coarse yet effective CFI variants and compiler-inserted shadow stacks reduce hijacking opportunities while respecting microcontroller limitations. Recent IoT-class systems-on-chip have started to expose TrustZone-M partitions, PAC, and XOM, offering a modest but growing substrate for in-hardware enforcement. Finally, remote attestation protocols allow a back-end service to verify that devices still run untampered firmware; although these schemes imperfectly scale to a fleet of millions, they provide an essential forensic signal and a basis for quarantining compromised nodes,[25].

Despite these advances, the extreme diversity of IoT hardware and the absence of uniform security standards continue to impede the deployment of comprehensive runtime protection. The following section synthesises the residual weaknesses and points to open research directions for next-generation IoT security.

# 3.6 Limitations and Open Challenges

Despite advances in runtime attack mitigation techniques, several limitations persist, leaving room for further research and innovation. Understanding these limitations is crucial for designing more effective security mechanisms and improving the resilience of modern computing systems against runtime exploits [12].

### 3.6.1 Gaps in Existing Defenses

Despite the wide deployment of runtime protection mechanisms, several limitations continue to undermine their effectiveness. A significant issue is the performance overhead

introduced by fine-grained Control-Flow Integrity and other runtime monitoring techniques. These approaches often incur high computational costs, rendering them impractical for performance-critical systems such as embedded devices and IoT platforms with limited processing power [13].

In parallel, attackers have developed increasingly sophisticated methods to bypass widely adopted defenses. Techniques such as memory disclosure vulnerabilities and JIT-ROP have proven to be effective in circumventing protections such as ASLR and DEP, allowing the reliable construction of exploitation chains even in hardened environments [14].

Another critical gap is incomplete hardware support for modern security features. Although newer architectures integrate hardware-based mitigations such as Intel's Control-Flow Enforcement Technology (CET) and ARM's PAC, many legacy systems and a large portion of IoT devices lack these protections. This makes them particularly susceptible to runtime attacks, including control-flow hijacking and code-reuse techniques [22].

# 3.6.2 Practical Feasibility of Control-Flow Integrity and Control-Flow Attestation

Although Control-Flow Integrity and Control-Flow Attestation have shown strong potential in securing runtime environments, their practical deployment introduces several challenges.

One key obstacle is the trade-off between security and flexibility, since the fine-grained Control-Flow Integrity enforces strict control-flow constraints that can conflict with legitimate program behavior. This rigidity may disrupt valid dynamic control flows commonly used in complex applications, making adoption difficult in real-world systems [23]. Furthermore, scalability issues arise with Control-Flow Attestation when attempting to apply remote attestation techniques to large IoT ecosystems. Verifying the runtime integrity of millions of devices in distributed environments imposes significant communication, storage, and processing overhead, which hinders the feasibility of such solutions on a scale [23].

Furthermore, recent research has revealed that side-channel attacks can undermine the guarantees offered by Control-Flow Integrity. These attacks exploit observable patterns such as cache access timings or power consumption to infer control-flow information, allowing adversaries to bypass or weaken Control-Flow Integrity protections without directly violating the control-flow graph [24]. These challenges illustrate the gap between theoretical security guarantees and the practical constraints faced when deploying Control-Flow Integrity and Control-Flow Attestation in resource-constrained and large-scale environments.

### 3.6.3 Future Research Directions

To address the current limitations of runtime security mechanisms, future research should prioritize several key areas. One critical focus is the development of lightweight security mechanisms that offer strong runtime protection while maintaining minimal performance overhead, making them suitable for resource-constrained environments such as IoT and embedded systems [25]. In parallel, there is a need to advance hardware-based defenses by enhancing features such as PAC, Memory tagging, and hardware-enforced Control-Flow Integrity. Strengthening these hardware-level protections can significantly improve resilience against sophisticated runtime attacks [25].

Another promising direction is the adoption of adaptive and AI-driven security models. By integrating machine learning techniques, security mechanisms can dynamically adapt to novel attack patterns, reducing the dependence on static control-flow enforcement policies and improving detection accuracy [25]. Finally, future research should explore the integration of Control-Flow Integrity and Control-Flow Attestation into hybrid security frameworks. Combining these techniques could offer more comprehensive protection by complementing runtime enforcement with verifiable attestation of control-flow integrity in distributed systems [25].

Given the ongoing evolution of attack strategies, continuous innovation is necessary to refine and extend existing runtime protection techniques. Addressing these research challenges will be vital to deliver scalable and effective defenses against emerging runtime threats.

# Chapter 4

# Methodology

### 4.1 Tools

Throughout the development and experimentation of this thesis, several tools were used to construct, analyze, and evaluate runtime software attacks and their detection.

The **GNU Compiler Collection (GCC)** [17], was used to compile vulnerable C programs with specific flags such as -fno-stack-protector and -no-pie to disable stack canaries and position-independent execution, thereby enabling traditional memory corruption exploits.

**GDB (GNU Debugger)** [18], was the primary tool for dynamic analysis. It allowed step-by-step execution, register inspection, memory examination, and post-crash analysis. It was particularly useful for identifying instruction pointers overwritten during buffer overflows.

The **Pwntools** Python library [8], was used to generate cyclic patterns (cyclic()) to determine the exact offset where the return address is overwritten. It was also used to automate the creation and injection of exploit payloads.

**ROPgadget** [21], was used to statically scan the compiled binaries for useful ROP gadgets such as pop rdi; ret, which are essential for chaining ROP-based attacks without injecting new code.

**Objdump** [19], was used to disassemble binaries to locate symbols, inspect PLT entries, and confirm the presence of function calls such as system() that can be used during attacks.

Cutter, a GUI front-end for radar2, was used for visual binary analysis, particularly to identify function boundaries and analyze the layout of CFG's [16]. It helped in understanding how functions like emergency\_shutdown could be reached through crafted input.

**Python** [7], was also used beyond Pwntools, in the design and implementation of our custom tools for analysis. Custom scripts parsed execution traces and log files, and constructed Boolean representations to flag abnormal control flow paths.

**Angr** was used for symbolic execution and static CFG recovery. It was leveraged to automatically analyze the structure of vulnerable binaries and verify reachable states during simulated execution, without relying on actual inputs.

**Intel PIN** was used for dynamic binary instrumentation, enabling runtime analysis of executed instructions with minimal overhead. It provided a programmable environment in which our custom C++ tool could be developed and integrated. This tool was built as a PIN pintool, capable of hooking into the execution flow at instruction granularity, logging control-flow transfers, and extracting contextual information for later detection analysis. The PIN framework made it possible to instrument binaries non-invasively, preserving their original structure while collecting precise runtime behavior essential for validating our detection approach.

**Linux (Kali Linux)** served as the primary operating system for the execution of the experiments. It offered compatibility with exploit-development tools and a controlled environment for vulnerability research and testing.

## 4.2 Environment setup

All experiments, analysis tools, and runtime monitoring mechanisms in this project were developed and tested in a controlled virtualized environment to ensure repeatability and isolation.

### Virtualized Execution Platform

A dedicated virtual machine (VM) was created to host the entire experimental environment:

**Hypervisor**: Oracle VirtualBox

**Guest OS**: Kali Linux 2024.1 (64-bit)

Base image: Clean install with root access and essential development packages

Memory and CPU: 4 GB RAM, 2 virtual CPUs

This setup was chosen for its compatibility with security research tooling, ease of snapshot management, and availability of pre-installed debugging utilities.

### **Binary Analysis and Exploitation Tooling**

To construct and analyze runtime attacks, the following tools were installed:

**Pwntools**: Python-based exploitation framework used to generate payloads, control program input, and script interaction with vulnerable binaries.

**Cutter** (GUI for radare2): Used for reverse engineering and inspection of binary internals, including symbol tables, code disassembly, and function boundaries.

**GDB** (GNU Debugger): Used in conjunction with cyclic patterns and pwndbg to identify buffer overflow offsets and analyze crash behavior at the instruction level.

**Python Environment**: Python 3.11 with virtual environment setup for dependency isolation. All scripts for static analysis and payload construction were developed using this environment.

## Static Analysis Setup with angr

To perform static control-flow extraction, the angr framework was installed within the same Python environment. The CFG generation and sensitive function marking scripts were written in Python using angr's CFGFast() module and VEX IR parsing API.

#### Intel PIN Instrumentation Environment

To enable runtime instrumentation, the Intel PIN dynamic binary instrumentation (DBI) framework was downloaded and installed:

**Version**: Intel PIN 3.24 (compatible with the host kernel and gcc version)

Installation: Decompressed and configured inside the VM

**Tool Development**: Custom Pintools (rop\_detector Listing 10.2, boolean\_rop\_detector Listing 10.4), were written in C++ and built using the provided makefile and headers from the PIN SDK.

All instrumentation binaries were compiled and tested within the Kali VM to ensure compatibility with target ELF binaries.

## 4.3 Insulin-pump setup

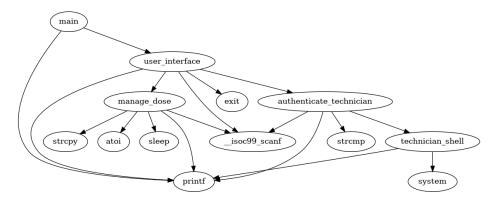

To simulate a vulnerable embedded application and facilitate realistic runtime attack development, a custom insulin pump controller was written in C and executed within the same virtualized environment used for binary analysis (see Listing 10.1.1 for source code overview).

**Language:** C (compiled using gcc with flags -g -fno-stack-protector -z execstack)

**Purpose:** Emulate real-world embedded control logic with deliberate vulnerabilities for exploit development

**Features:** Menu-driven insulin dosing logic, password-protected technician access, and a hidden diagnostic shell

**Source Location:** Maintained within a Git repository inside the Kali Linux VM **Build Process:** Compiled manually with debugging symbols enabled to facilitate runtime instrumentation

The application, shown in Listing 10.1.1, includes an intentionally unsafe input operation using scanf("%s", buffer), which introduces a classic stack-based buffer overflow vulnerability. This allows crafted input to potentially overwrite return addresses on the stack and hijack control flow. A hidden privileged function, technician\_shell(), is present in the binary and mimics insecure maintenance backdoors found in real embedded medical systems.

#### User Interface and Control Flow

The controller implements a simple terminal-based interface via the user\_interface() function, providing users with the option to administer an insulin dose, attempt technician login, or exit the program. Input is handled directly via standard input, and all control logic is kept deliberately simple to facilitate exploit development and analysis.

The authentication logic prompts for a plaintext password and compares it to a hardcoded string. If the input matches, it directly launches a system shell via system("/bin/sh"). This insecure design simulates low-assurance access mechanisms found in prototype or poorly secured embedded devices.

### **Deployment Context**

The binary was executed and tested entirely within the isolated Kali Linux guest VM environment using direct terminal interaction. No hardware interfacing was implemented, as the purpose of the simulation was to isolate and examine binary-level weaknesses relevant to runtime exploitation and ROP attacks.

## Chapter 5

# Design

This chapter presents a high-level design of the runtime detection frameworks developed in this thesis. Our objective is to detect ROP attacks in vulnerable embedded applications by observing and validating control flow at runtime. To this end, we designed two complementary detection techniques, each targeting different characteristics of ROP behavior.

## 5.1 System Overview

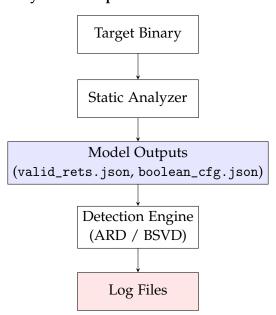

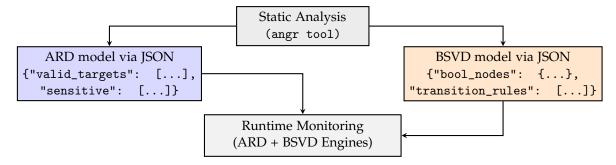

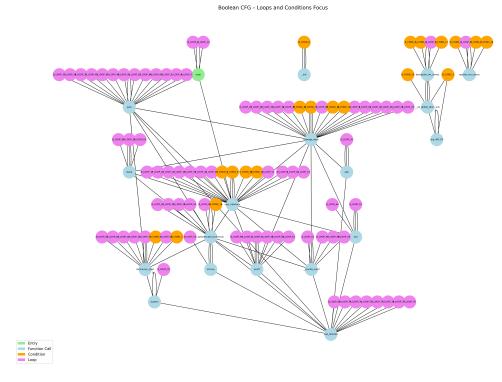

The runtime detection framework proposed in this thesis is designed to monitor low-level program execution for control-flow violations, specifically targeting ROP-style attacks. The architecture is structured into two distinct phases: Firstly, an offline static analysis phase and an online runtime monitoring phase. Figure 5.1 provides an overview of this flow.

The process begins with a "Target Binary", representing the program under test. This binary undergoes offline processing by the "Static Analyzer", which extracts control-flow information prior to execution. Rather than instrumenting or rewriting the binary, the analyzer parses its structure to identify return addresses and semantic function transitions.

The output of this phase is a set of Model Outputs, including:

valid\_rets.json: a whitelist of legitimate return addresses used by the ARD engine.

boolean\_cfg.json: a semantically enriched Boolean control-flow graph defining allowed function-level transitions for the BSVD engine.

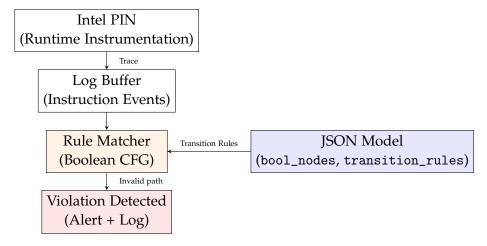

These artifacts are consumed by the Detection Engine, which operates at runtime. The system supports two alternative detection modes: