Mykolas Poska, Rokas Sukauskis

Advanced Power Electronics APEL4-2-24, Spring Semester 2024

**Master Thesis**

#### **Advanced Power Electronics**

Aalborg University https://www.aau.dk

### **AALBORG UNIVERSITY**

STUDENT REPORT

#### Title:

Development and Analysis of Modular Multilevel Converter Integrated with Battery Storage for Grid Support

Theme:

**Master Thesis**

**Project Period:**

Spring Semester 2024

**Project Group:**

APEL4-2-24

**Participants:**

Rokas Sukauskis Mykolas Poska

**Supervisors:**

Amin Hajizadeh

Page Numbers: 144

**Date of Completion:**

3rd June 2024

#### **Abstract:**

This thesis investigates grid support using battery energy storage systems. Initially, a problem analysis is conducted to understand various converters, energy storage systems, and control algorithms used in grid support. The focus then shifts to Modular Multilevel Converters (MMC) integrated with second-life batteries in each submodule via bidirectional buck-boost converters. Dynamic modeling of the MMC for output current control and circulating currents is developed, accompanied by electrical circuit simulations. Various control algorithms, including output current control, active/reactive power control, circulating current suppression, and balancing strategies, are analyzed and implemented. A small-signal model of the bidirectional buck-boost converter is derived, and controllers are tuned for a constant current and constant voltage protocol for battery charging and discharging. Second-life batteries are examined, and an electrical equivalent model is defined, with parameters identified based on the state of charge and charge-discharge cycles to simulate aging pro-Integration of batteries into the MMC is performed, with preliminary analyses showing that battery-integrated MMCs can assist with active power supply and demand regulation. Finally, further research aspects are identified to enhance system model accuracy and simulation fidelity.

## **Contents**

| Li | st of | Figures                            |                                               | v                    |

|----|-------|------------------------------------|-----------------------------------------------|----------------------|

| Li | st of | Tables                             |                                               | ix                   |

| Pr | eface |                                    |                                               | 1                    |

| 1  | 1.1   |                                    | Challenges                                    | <b>2</b><br>2        |

|    | 1.2   | Batter                             | y Energy Storage System                       | 2                    |

| 2  | Prol  | olem A                             | nalysis                                       | 3                    |

|    | 2.1   | Grid S<br>2.1.1<br>2.1.2           | Support Applications                          | 3<br>3<br>4<br>5     |

|    | 2.2   | 2.1.3<br>Batteri<br>2.2.1<br>2.2.2 | Energy Arbitrage                              | 6<br>6<br>6          |

|    | 2.3   |                                    | Converters for Battery Connection to the Grid | 11<br>11<br>12<br>14 |

|    |       | 2.3.4<br>2.3.5<br>2.3.6            | Solid-State Transformer                       | 14<br>16<br>19<br>21 |

|    | 2.4   |                                    | Requirements and Standards                    | 24<br>24<br>26       |

|    | 2.5   | Conclu                             | usion                                         | 26                   |

| 3  | Task  | c Staten                           | nent                                          | 28                   |

Contents

| Mod                 | deling                    |                                                                                                                                                                                                                                  | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|---------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 4.1 Modeling of MMC |                           |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                     | 4.1.1                     |                                                                                                                                                                                                                                  | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                     | 4.1.2                     |                                                                                                                                                                                                                                  | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                     | 4.1.3                     | e e e e e e e e e e e e e e e e e e e                                                                                                                                                                                            | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                     | 4.1.4                     | Dynamic Modelling of MMC                                                                                                                                                                                                         | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                     | 4.1.5                     | Modulation                                                                                                                                                                                                                       | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                     | 4.1.6                     |                                                                                                                                                                                                                                  | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 4.2                 | Model                     |                                                                                                                                                                                                                                  | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                     | 4.2.1                     | · ·                                                                                                                                                                                                                              | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                     | 4.2.2                     |                                                                                                                                                                                                                                  | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                     | 4.2.3                     | <u> </u>                                                                                                                                                                                                                         | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                     | 4.2.4                     |                                                                                                                                                                                                                                  | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                     | 4.2.5                     |                                                                                                                                                                                                                                  | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 4.3                 | Battery                   |                                                                                                                                                                                                                                  | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                     |                           |                                                                                                                                                                                                                                  | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                     |                           |                                                                                                                                                                                                                                  | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 4.4                 | Submo                     |                                                                                                                                                                                                                                  | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Con                 | trol                      |                                                                                                                                                                                                                                  | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                     |                           | Definition of Control Lavers                                                                                                                                                                                                     | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                     |                           |                                                                                                                                                                                                                                  | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                     |                           |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                     | 5.0.4                     | Battery integration into MMC SMs                                                                                                                                                                                                 | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Disc                | cussion                   |                                                                                                                                                                                                                                  | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 6.1                 | Future                    | e Work                                                                                                                                                                                                                           | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                     | 6.1.1                     | Optimization of the models and simulation                                                                                                                                                                                        | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                     | 6.1.2                     | Battery parameter identification using experimental battery pack data                                                                                                                                                            | 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                     | 6.1.3                     |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                     | 6.1.4                     | ·                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                     | 6.1.5                     | •                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                     | 6.1.6                     | ,                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Con                 | clusion                   | l                                                                                                                                                                                                                                | 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| bliog               | raphy                     |                                                                                                                                                                                                                                  | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Ū                   |                           | previations                                                                                                                                                                                                                      | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| -100                |                           | - V - ATT A V - L V                                                                                                                                                                                                              | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                     | 4.1 4.2 4.3 4.4 Con bliog | 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.1.6 4.2 Model 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5 4.3 Batter 4.3.1 4.3.2 4.4 Submo  Control 5.0.1 5.0.2 5.0.3 5.0.4  Discussion 6.1 Future 6.1.1 6.1.2 6.1.3 6.1.4 6.1.5 6.1.6  Conclusion  bliography | 4.1 Modeling of MMC 4.1.1 Structure of MMC 4.1.2 Voltage Addition 4.1.3 Component Selection 4.1.4 Dynamic Modelling of MMC 4.1.5 Modulation 4.1.6 Electrical Circuit and Transfer Function Validation 4.2 Modelling of Submodules 4.2.1 Battery Side Bidirectional DC-DC Buck-Boost Converter 4.2.2 Converter Design 4.2.3 Modualation 4.2.4 Component Selection 4.2.5 Mathematical Modeling 4.3 Battery Modeling 4.3.1 Li-ion Battery 4.3.2 Thevenin Model 4.4 Submodule Model  Control 5.0.1 Definition of Control Layers 5.0.2 Control of Modular Multilevel Converter 5.0.3 Battery Charge/Discharge Control 5.0.4 Battery integration into MMC SMs  Discussion 6.1 Future Work 6.1.1 Optimization of the models and simulation 6.1.2 Battery parameter identification using experimental battery pack data 6.1.3 More in-depth controller tuning 6.1.4 Real-life experiments 6.1.5 Battery current ripple reduction 6.1.6 FLBs and SLBs comparison for a larger period time in operation  Conclusion |  |  |  |  |

| Contents | 1V |

|----------|----|

| Comens   | IV |

|          |    |

## C Battery Charging

**140**

# **List of Figures**

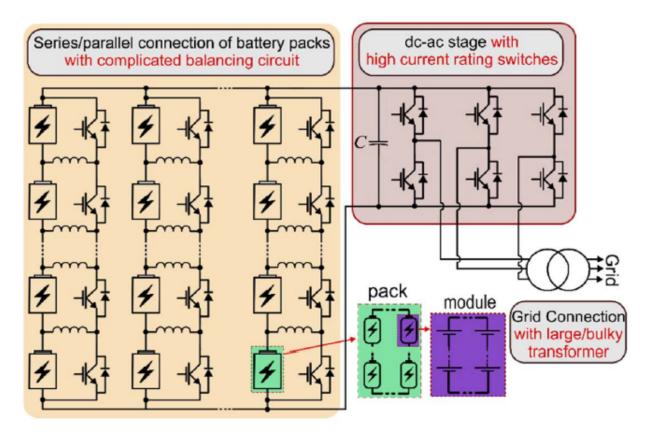

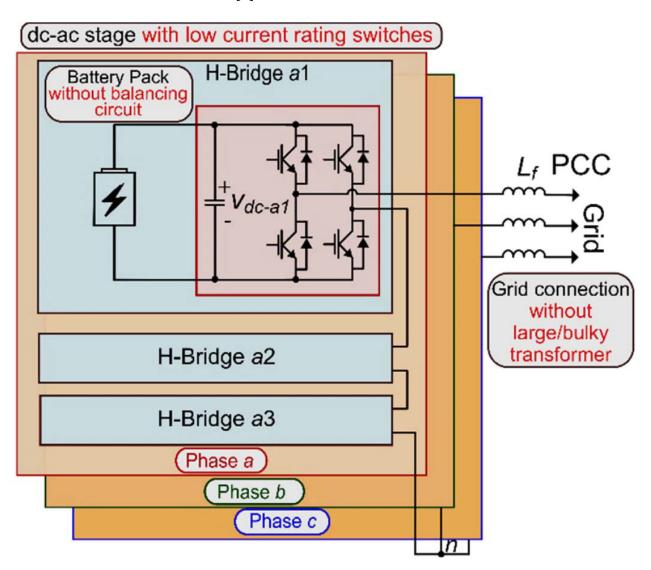

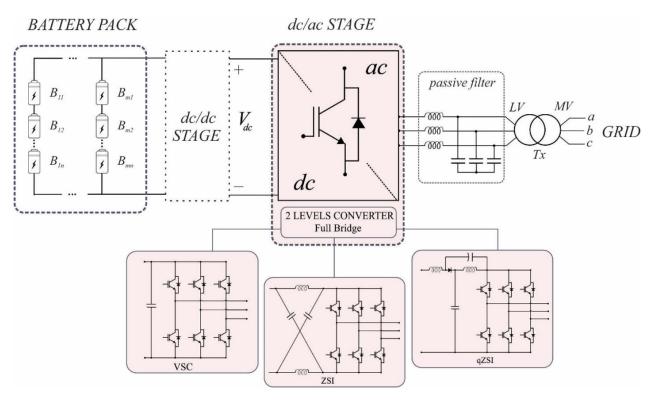

| 2.1  | Battery unit connected to the grid through 2-level VSC and step-up transformer [7] | 12         |

|------|------------------------------------------------------------------------------------|------------|

| 2.2  | Cascaded H-bridge converter [7]                                                    | 13         |

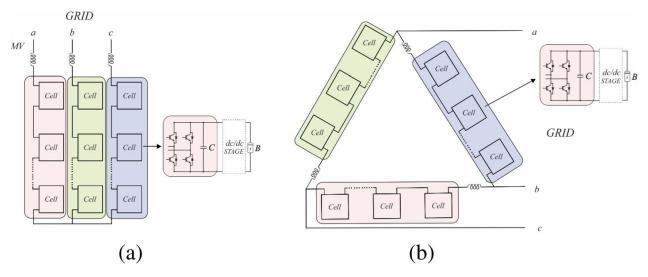

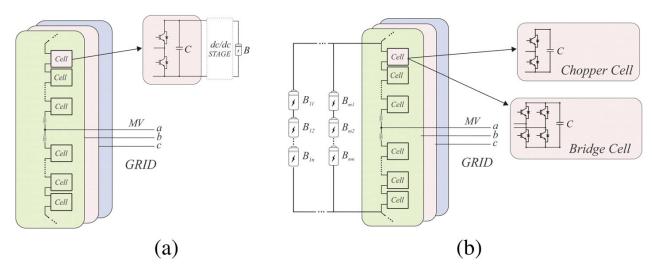

| 2.3  | Modular multilevel converter. Diagram (a) shows centralized battery con-           | 10         |

| 2.0  | nection. Diagram (b) shows distributed battery connection [7]                      | 14         |

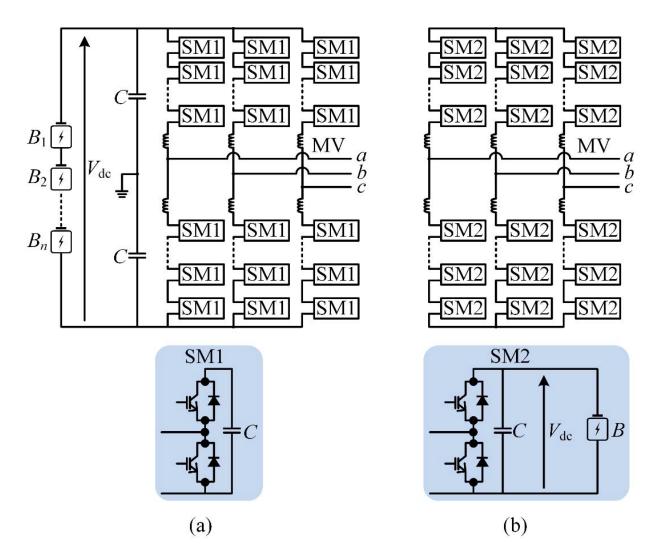

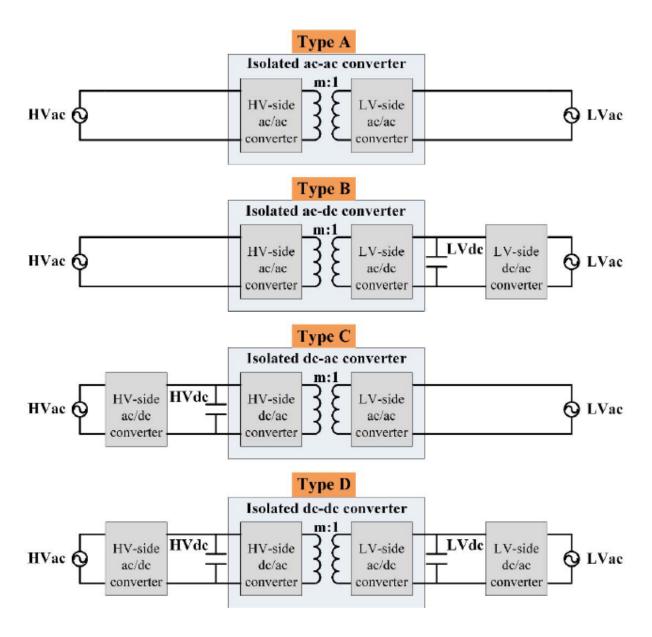

| 2.4  | Representation of different SST types [7]                                          | 16         |

| 2.5  | Most common converter topologies and components for battery connec-                |            |

|      | tion to the grid using transformer [15]                                            | 18         |

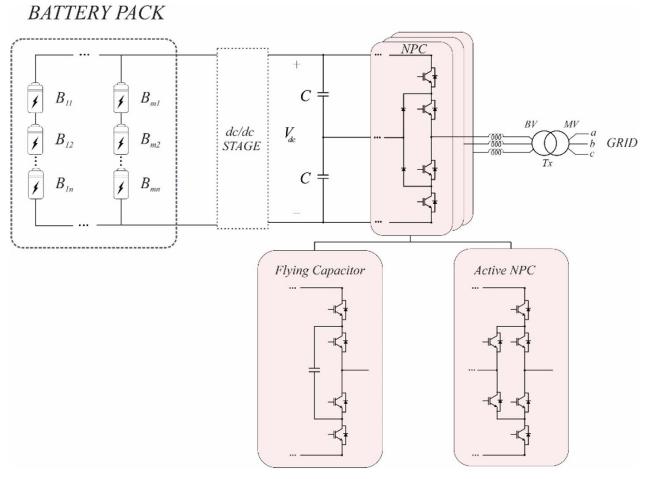

| 2.6  | More advanced converter topologies and components for battery connec-              |            |

|      | tion to the grid using transformer [15]                                            | 19         |

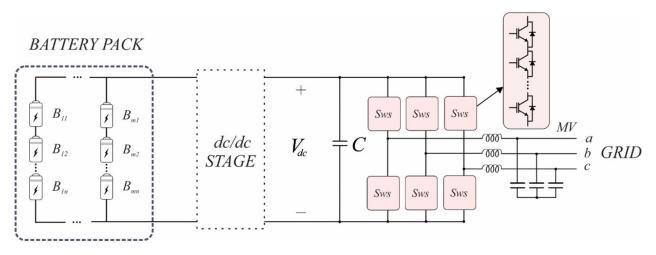

| 2.7  | Diagram of 2-level VSC with series connected semiconductor switches [15]           | 20         |

| 2.8  | (a) CHB in star configuration, (b) CHB in delta configuration [15]                 | 20         |

| 2.9  | MMC with (a) dispositions of batteries in cells, (b) disposition of batteries      |            |

|      | in DC-link [15]                                                                    | 21         |

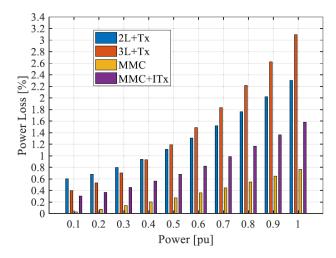

| 2.10 | Comparison of power losses for each converter topology at different power          |            |

|      | levels [15]                                                                        | 23         |

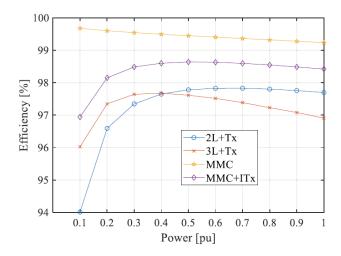

|      | Efficiency for each converter topology at different power levels [15]              | 23         |

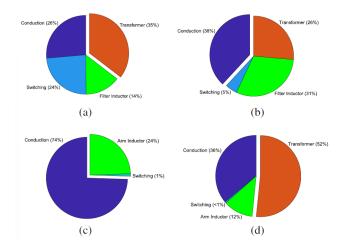

| 2.12 | Detailing of losses between conduction, switching, inductor and trans-             |            |

|      | former at nominal power (1 pu) (a) 2 L+Tx, (b) 3 L+Tx, (c) MMC, (d)                |            |

|      | MMC +ITx [15]                                                                      | 24         |

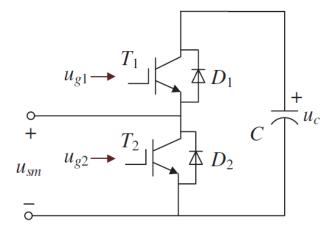

| 4.1  | Example half-bridge submodule configuration                                        | 32         |

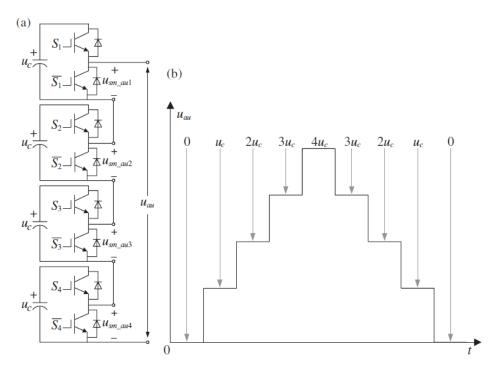

| 4.2  | Stepped Voltage Synthesis [21]                                                     | 34         |

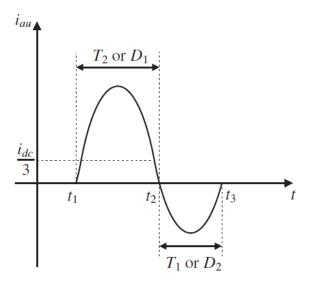

| 4.3  | Arm Current Waveform [23]                                                          | 37         |

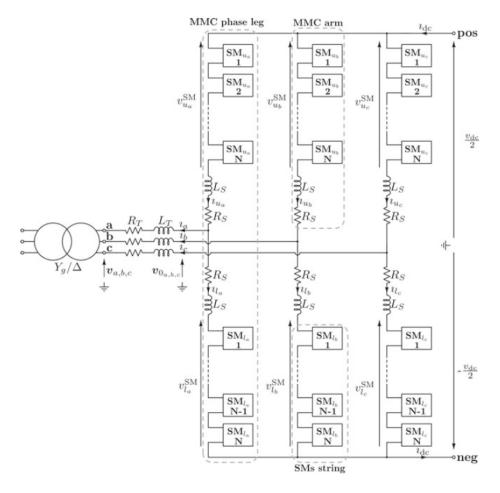

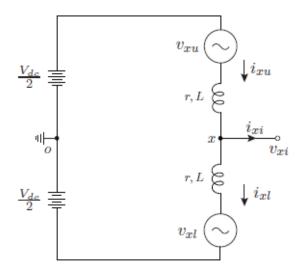

| 4.4  | Circuit diagram of grid connected MMC [21]                                         | 40         |

| 4.5  | Decoupled DC side circuit representation [25]                                      | 41         |

| 4.6  | Upper Arm Current Transfer Function                                                | <b>4</b> 4 |

| 4.7  | Lower Arm Current (Circulating Current) Transfer Function                          | 45         |

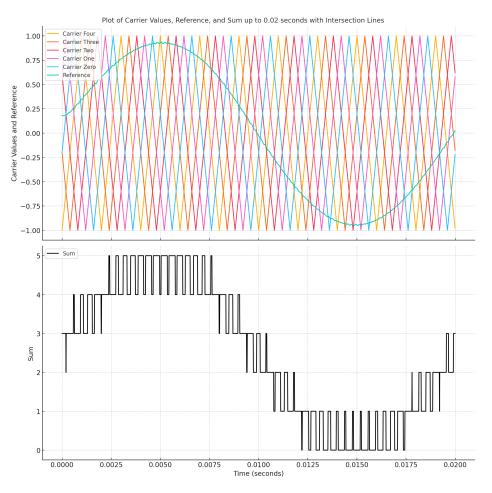

| 4.8  | PS-PWM Modulation                                                                  | 47         |

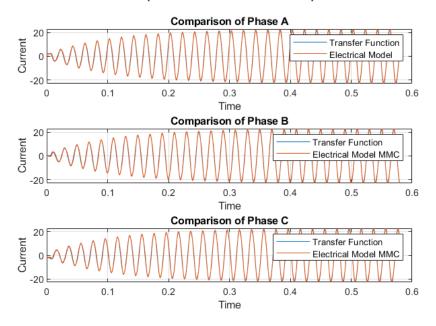

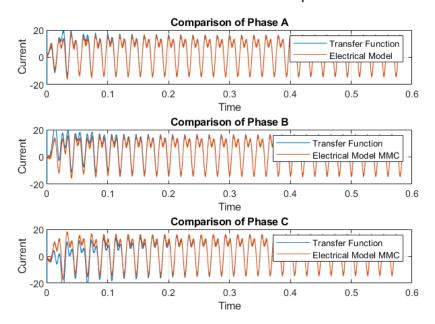

| 4.9  | MMC Output Current Model Comparison                                                | 49         |

| 4.10 | MMC Output Current Model Comparison (zoomed in)                                    | 49         |

List of Figures vi

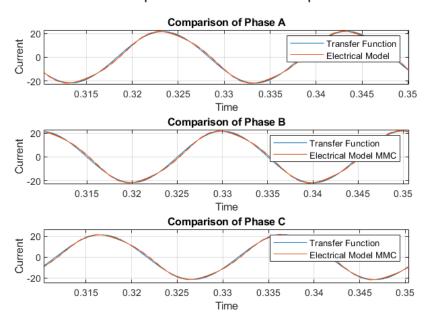

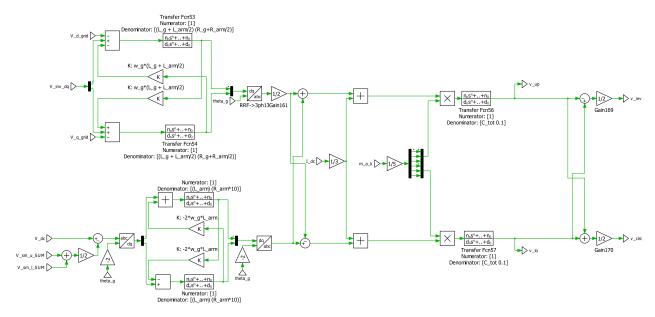

| 4.11 | MMC Circulating Current Model Comparison                                        | 50 |

|------|---------------------------------------------------------------------------------|----|

| 4.12 | MMC Circulating Current Model Comparison (zoomed in)                            | 51 |

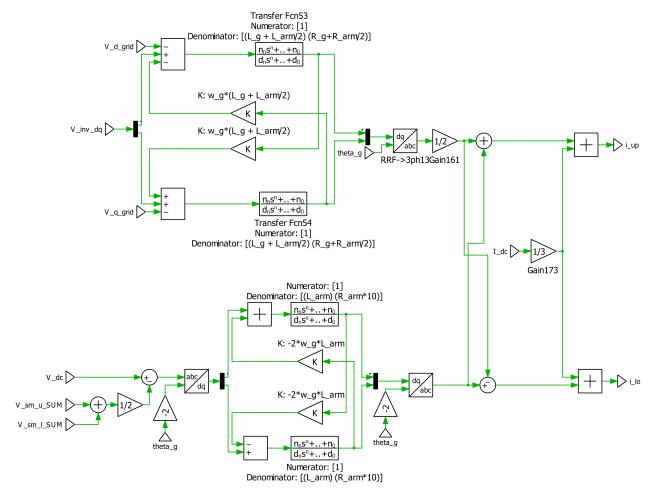

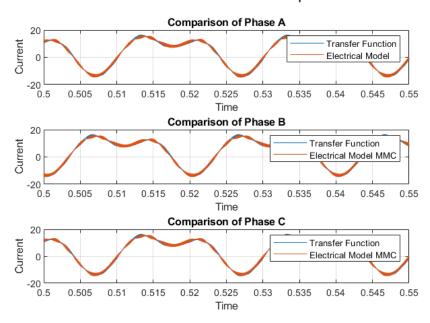

|      | Transfer function model for upper and lower arm currents                        | 52 |

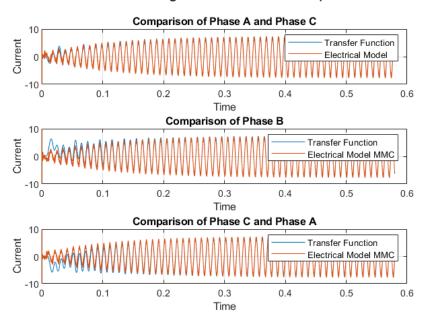

| 4.14 | MMC Arm Current Model Comparison                                                | 53 |

| 4.15 | MMC Arm Current Model Comparison (zoomed in)                                    | 53 |

| 4.16 | Transfer function model with added submodule capacitor dynamics                 | 54 |

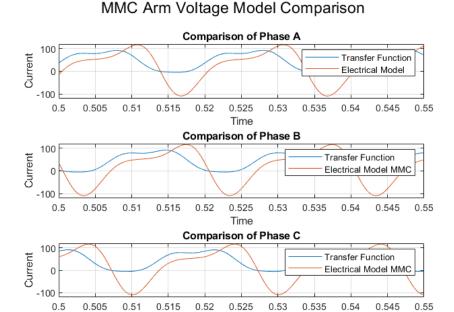

| 4.17 | MMC Arm Voltage Model Comparison                                                | 55 |

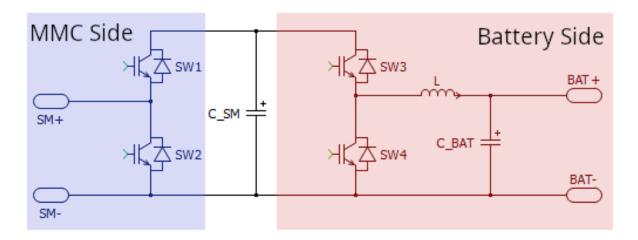

| 4.18 | Modified submodule with battery integration                                     | 56 |

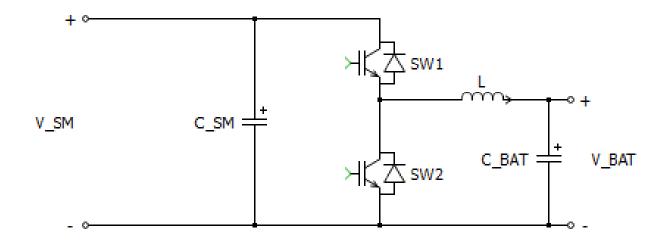

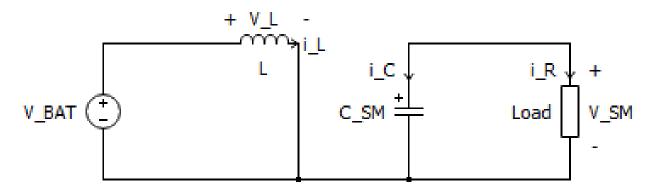

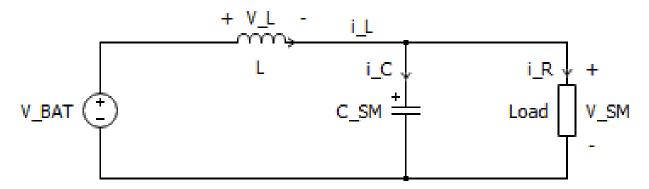

|      | Battery Side DC/DC Buck-Boost Converter                                         | 57 |

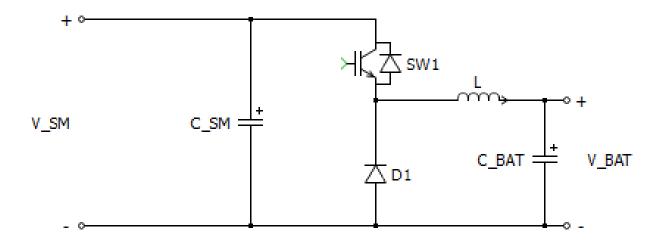

|      | DC-DC Buck Converter                                                            | 57 |

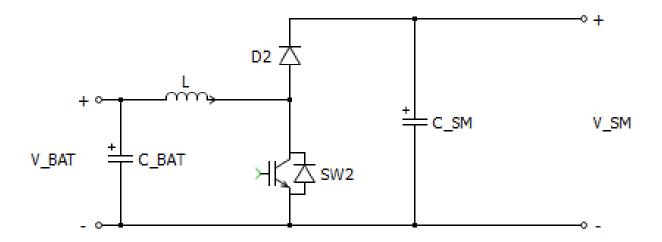

| 4.21 | DC-DC Boost Converter                                                           | 58 |

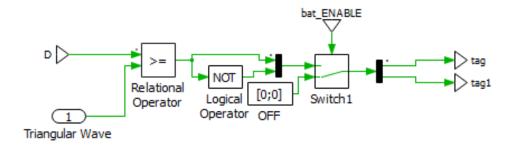

| 4.22 | Modulation logic for the DC-DC converter                                        | 58 |

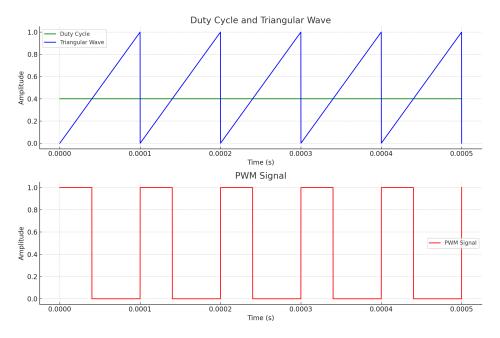

| 4.23 | Modulation Waveform (Duty Cycle 0.4)                                            | 59 |

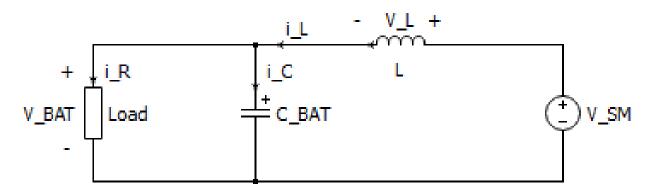

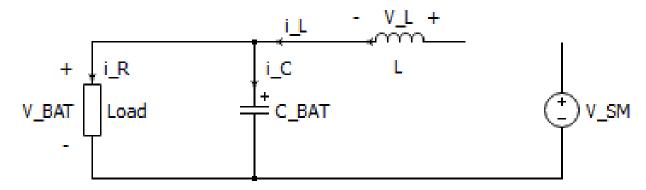

| 4.24 | EEC of Buck Converter when $SW_1$ is closed                                     | 63 |

| 4.25 | EEC of Buck Converter when $SW_1$ is open                                       | 64 |

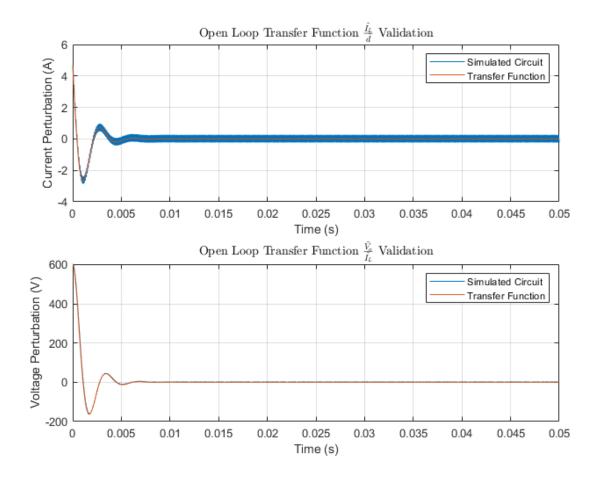

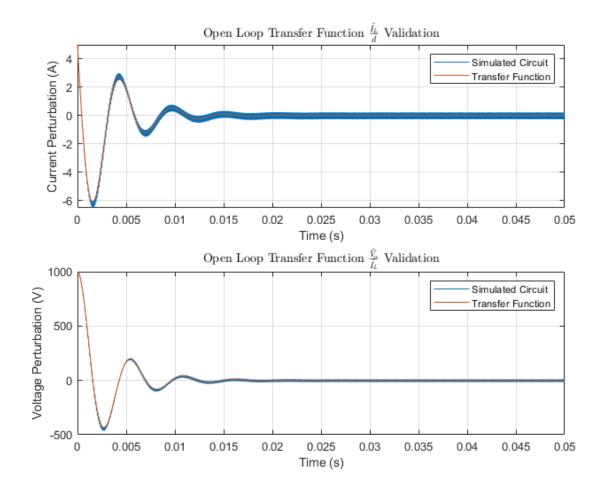

|      | Open-loop buck mode transfer function validation                                | 67 |

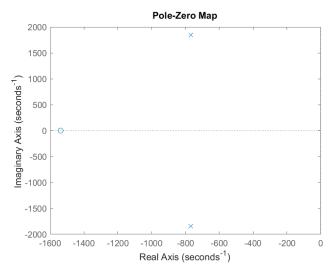

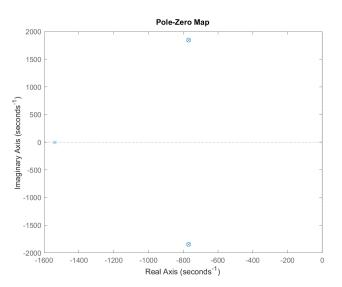

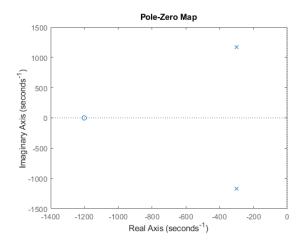

|      | Pole-zero map of $\frac{\tilde{I_L}}{\tilde{d}_{\tilde{L}}}$                    | 68 |

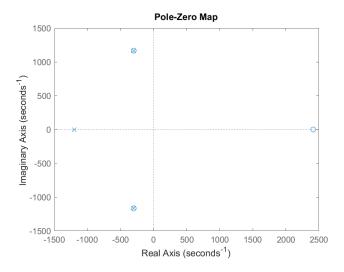

| 4.28 | Pole-zero map of $\frac{V_{SM}}{\tilde{I}_I}$                                   | 68 |

|      | EEC of Boost Converter when $SW_2$ is closed                                    | 69 |

|      | EEC of Boost Converter when $SW_2$ is open                                      | 70 |

|      | Open-loop boost mode transfer function validation                               | 73 |

|      | Pole-zero map of $\frac{\tilde{I_L}}{\tilde{d}}$                                | 74 |

|      | Pole-zero map of $\frac{\tilde{V}_{\tilde{B}AT}}{\tilde{I}_{I}}$                | 74 |

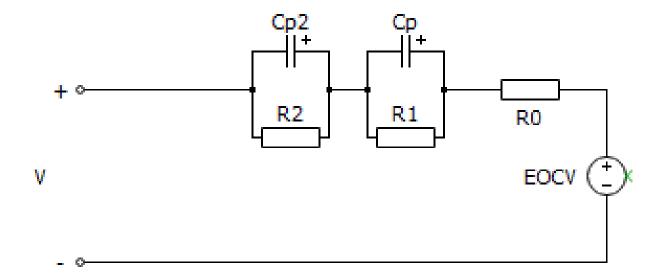

| 4.34 | Second-order Thevenin model in PLECS                                            | 76 |

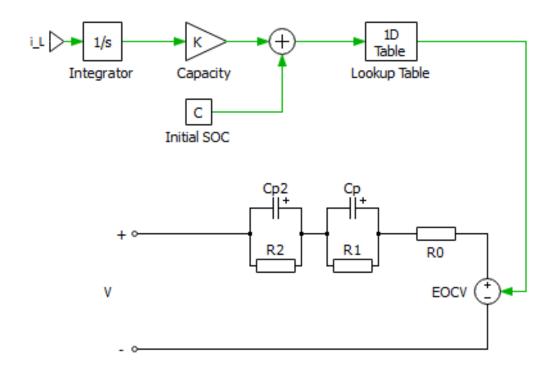

| 4.35 | Battery model with coulomb counting in PLECS                                    | 77 |

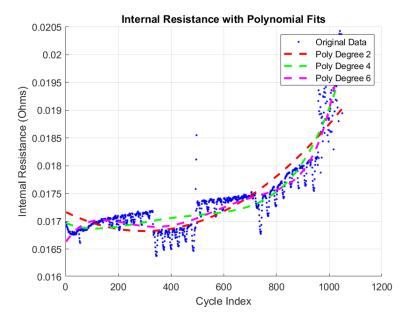

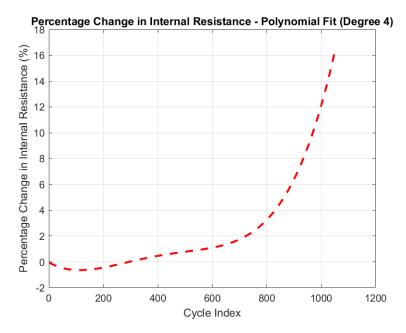

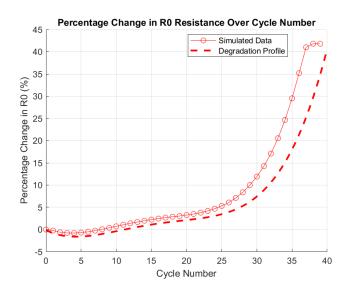

| 4.36 | Degradation of $R_0$ with polynomial fits                                       | 78 |

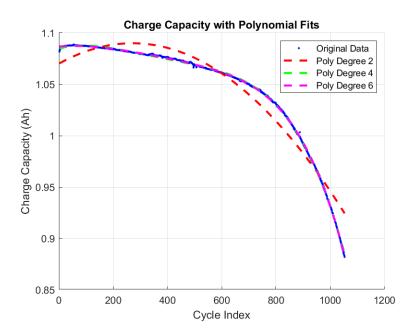

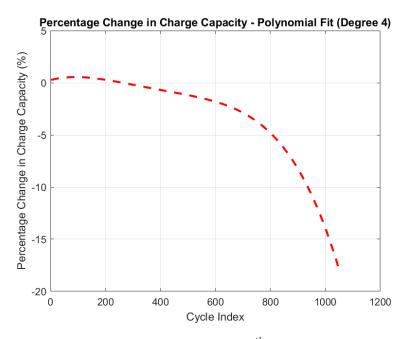

| 4.37 | Degradation of <i>Q</i> with polynomial fits                                    | 78 |

| 4.38 | Degradation Profile of $R_0$ , $4^{th}$ order polynomial fit                    | 79 |

| 4.39 | Degradation Profile of $Q$ , $4^{th}$ order polynomial fit                      | 79 |

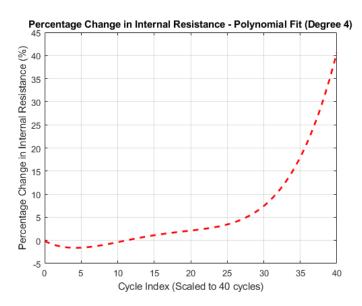

|      | Degradation Profile of $R_0$ , $4^{th}$ order polynomial fit (Scaled)           | 80 |

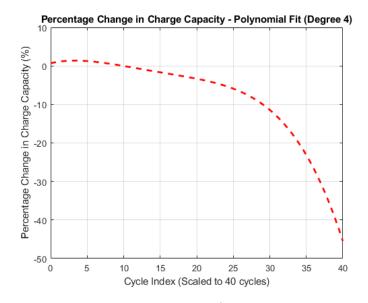

| 4.41 | Degradation Profile of $Q$ , $4^{th}$ order polynomial fit (Scaled)             | 80 |

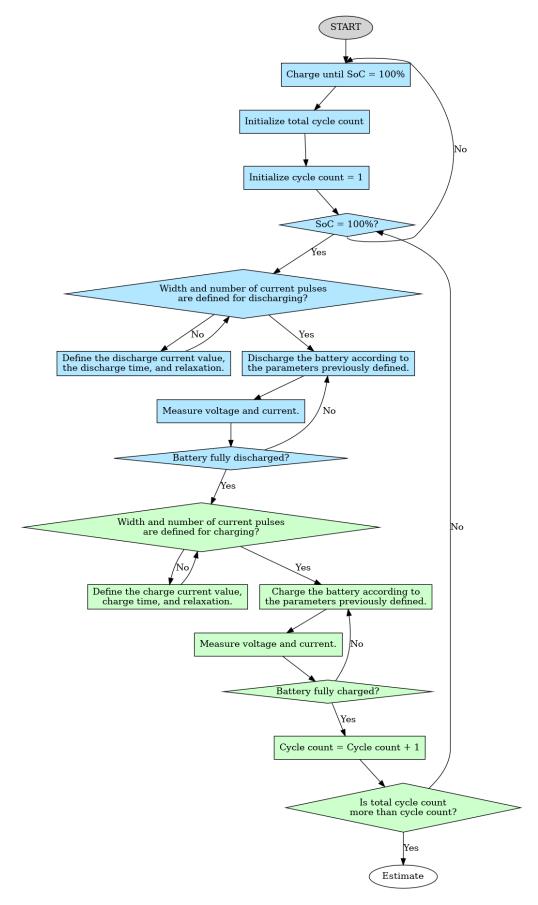

| 4.42 | Flowchart of the data acquisition process                                       | 82 |

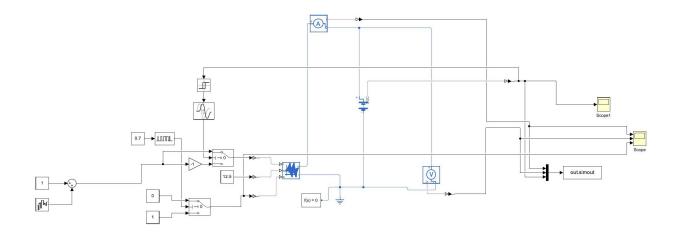

|      | Battery Testing Environment Simulation                                          | 83 |

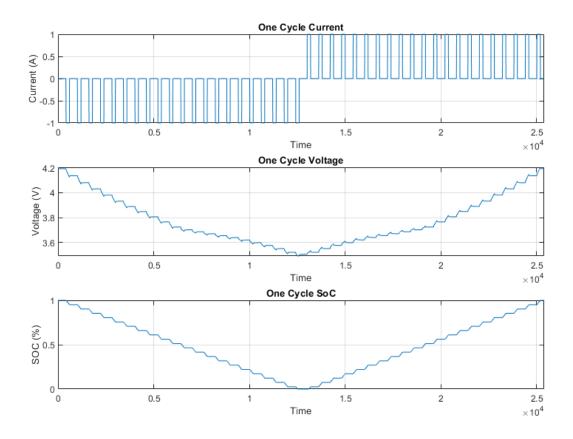

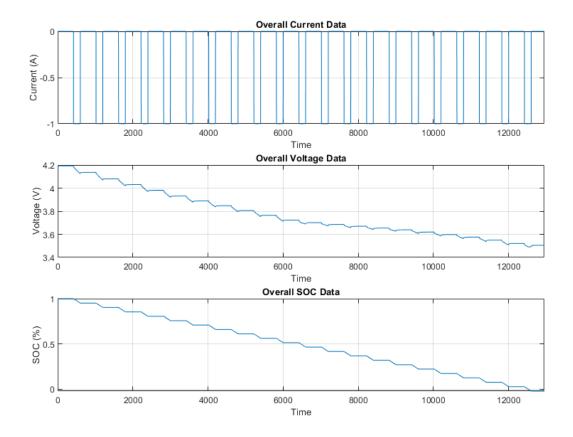

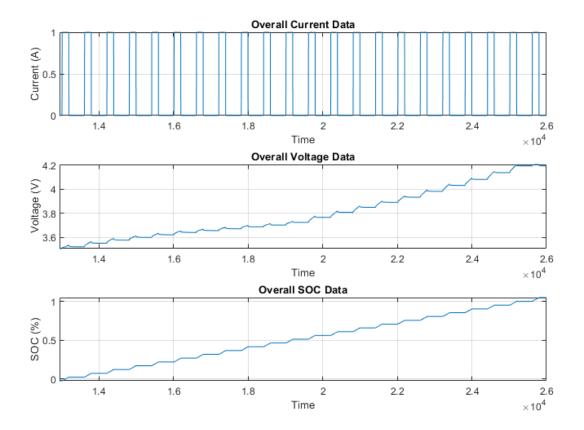

|      | Current, Terminal Voltage and SOC over one cycle                                | 84 |

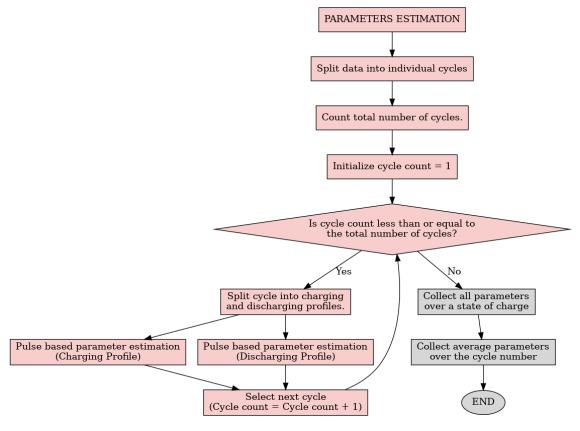

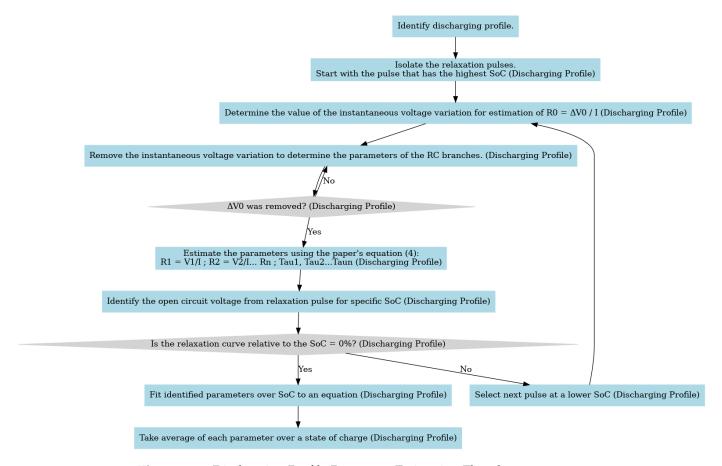

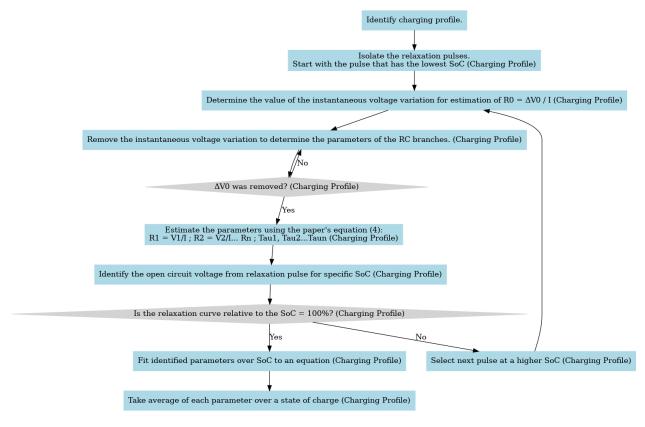

|      | Parameter Identification Flowchart                                              | 85 |

|      | Discharging Profile Parameter Estimation Flowchart                              | 86 |

|      | Discharge Profile of the collected data                                         | 87 |

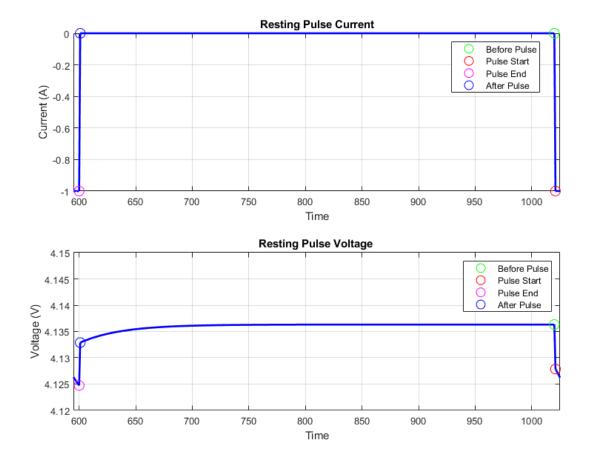

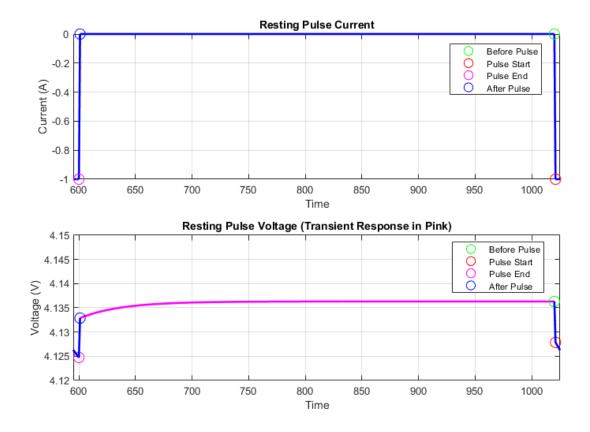

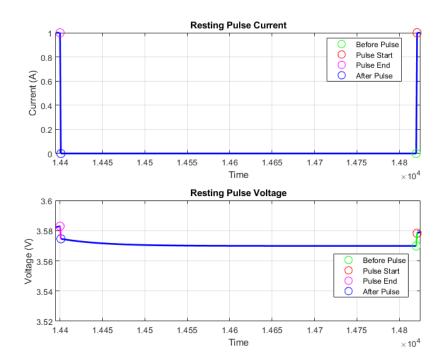

|      | Individual Resting Pulse $V_{OCV}$ and $I \dots \dots \dots \dots \dots \dots$  | 88 |

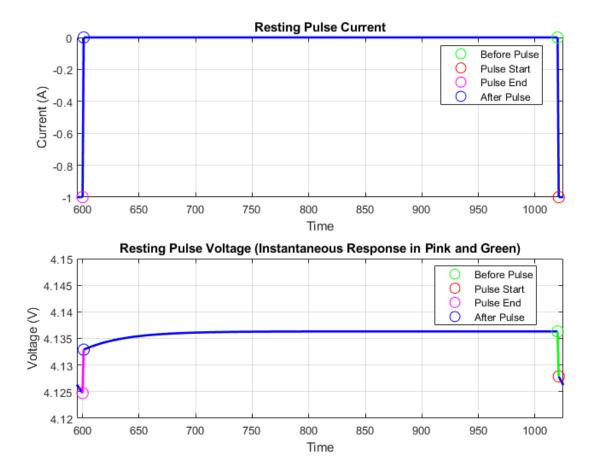

| 4.49 | Individual Resting Pulse $V_{OCV}$ and $I$ (Instantaneous Response Highlighted) | 89 |

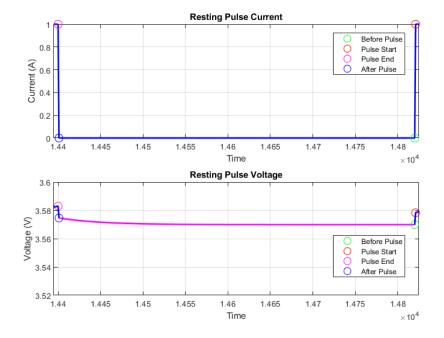

List of Figures vii

| 4.50        | Individual Resting Pulse $V_{OCV}$ and $I$ (Transient Response Highlighted) | 90  |

|-------------|-----------------------------------------------------------------------------|-----|

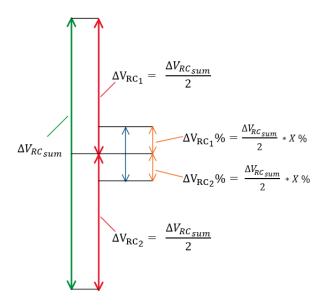

|             | $\Delta V_{RC_1}$ and $\Delta V_{RC_2}$ lower bound selection               | 91  |

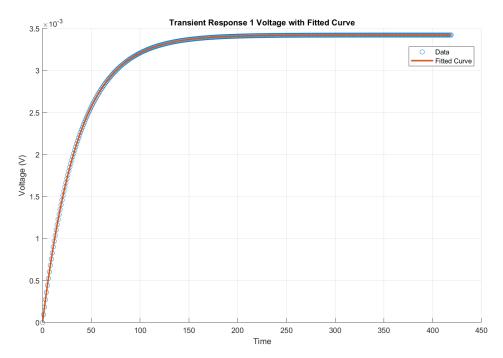

|             | Curve Fitting of the 2-RC Transient Response                                | 92  |

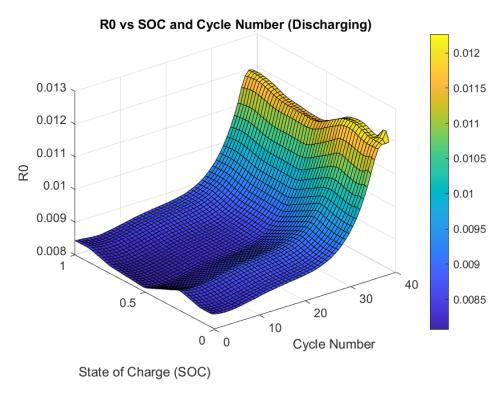

|             | R <sub>0</sub> parameter over SoC and Cycle Number (Discharging)            | 93  |

|             | Comparison of identified $R_0$ degradation with the degradation profile     | 93  |

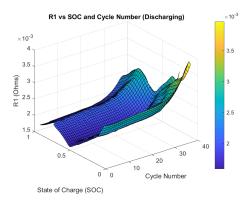

|             | $R_1$ parameter over SoC and Cycle Number (Discharging)                     | 94  |

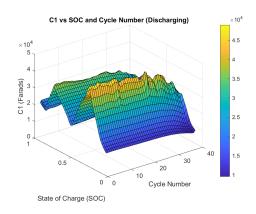

|             | $C_p$ parameter over SoC and Cycle Number (Discharging)                     | 94  |

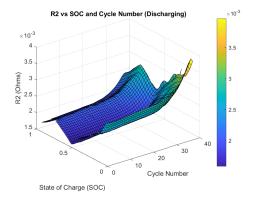

|             | $R_2$ parameter over SoC and Cycle Number (Discharging)                     | 94  |

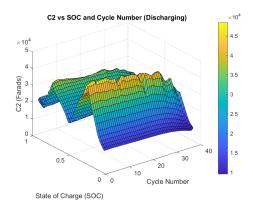

|             | $C_{p2}$ parameter over SoC and Cycle Number (Discharging)                  | 94  |

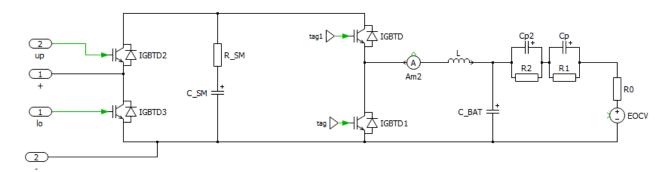

|             | Submodule simulation in PLECS                                               | 96  |

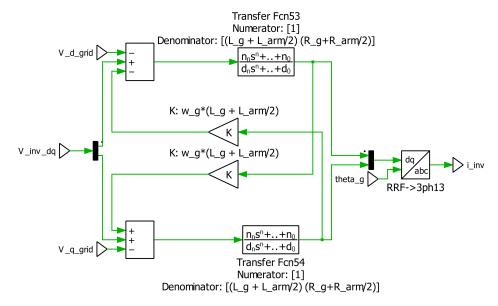

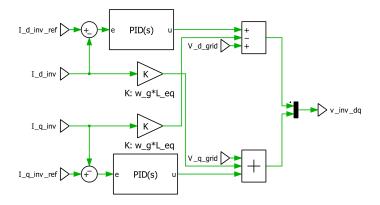

| 5.1         | Output current controller in dq-frame with cross-coupling and feedfor-      | 0.0 |

|             | ward terms.                                                                 | 99  |

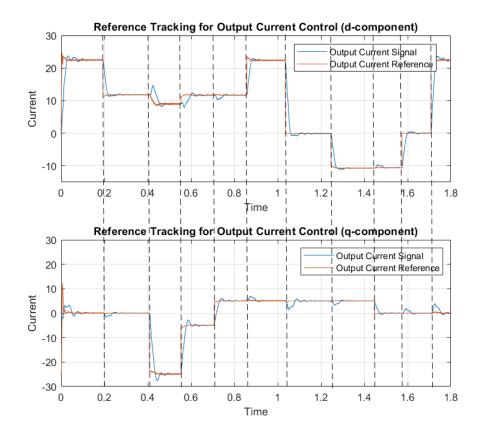

| 5.2         | Output current controller performance for reference tracking. Upper graph   |     |

|             | shows d-component, lower graph shows q-component and dashed lines           | 00  |

| - 0         | indicate the interaction between d and q components                         | 99  |

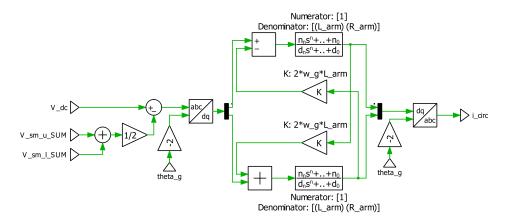

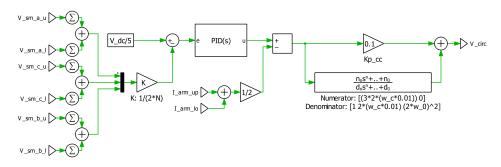

| 5.3         | Circulating current suppression control diagram                             | 100 |

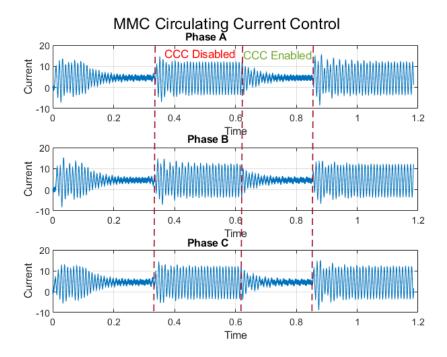

| 5.4         | Circulating currents in each phase when circulating current controller is   | 100 |

|             | disabled and enabled                                                        | 102 |

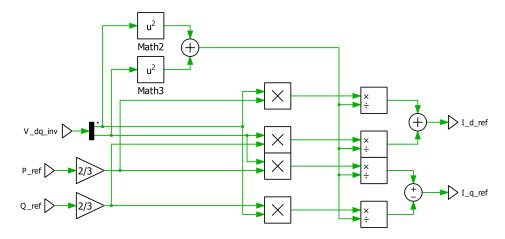

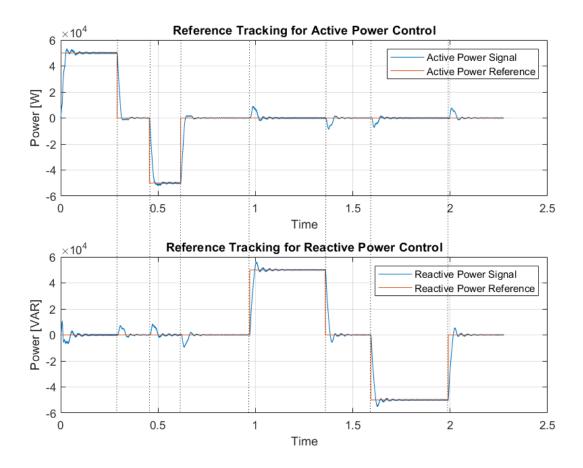

| 5.5         | Block diagram of instantaneous P/Q controller                               |     |

| 5.6         | Active and reactive power reference following                               | 104 |

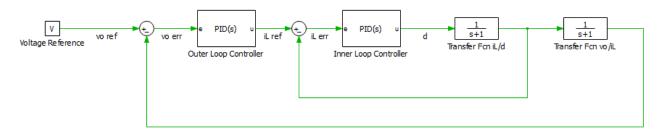

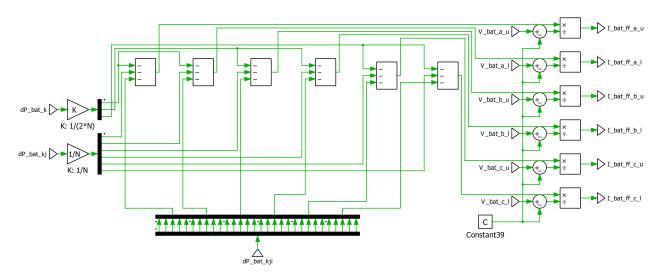

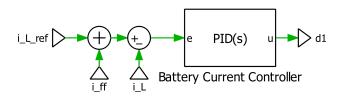

| 5.7         | DC-DC converter cascaded control scheme                                     |     |

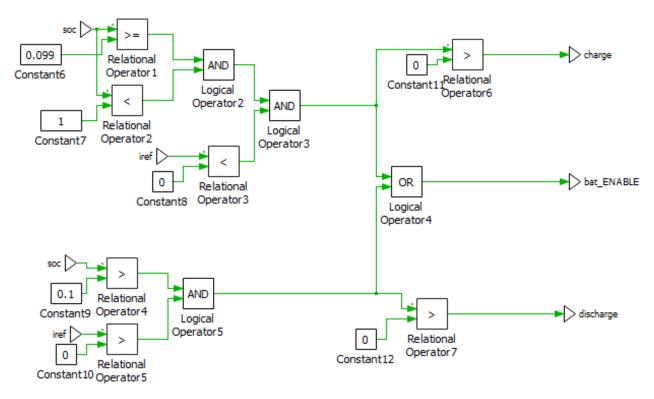

| 5.8         | Battery Enable/Disable Logic                                                |     |

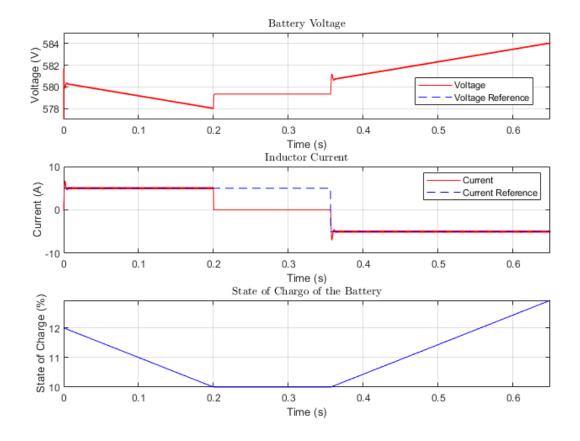

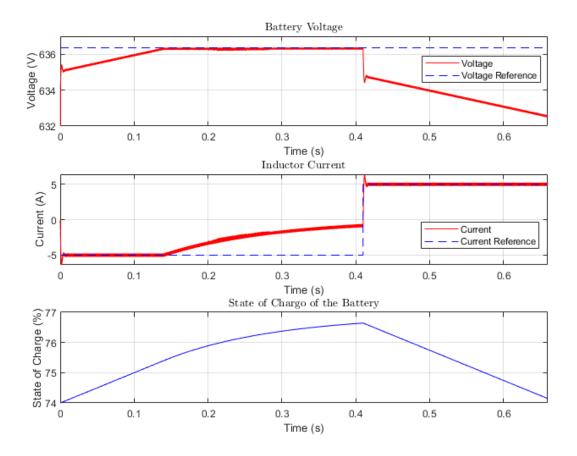

| 5.9         | Voltage, Current and SoC plots for battery enable/disable logic             |     |

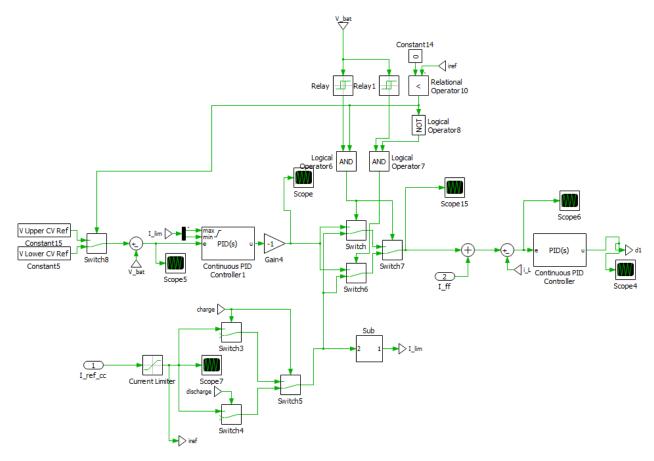

| 5.10        | CC-CV Control                                                               | 108 |

|             | Voltage, Current and SoC plots of the CC/CV control                         |     |

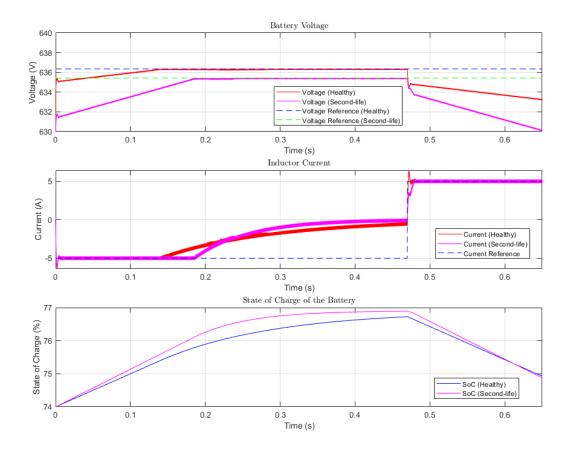

|             | Battery Voltage, Current and SoC comparison at 100% and 70% SoC             |     |

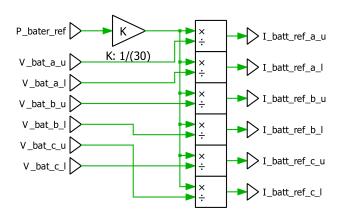

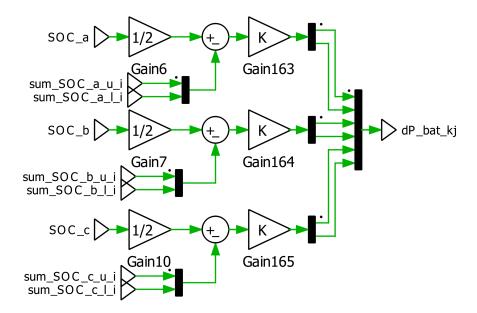

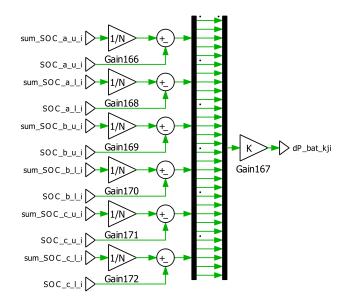

|             | Reference current calculation for each battery controller                   |     |

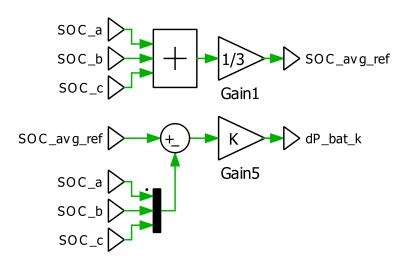

|             | SOC averaging and delta power for phase SOC balancing within total SOC      |     |

|             | Delta power control for arm SOC balancing within phase SOC                  |     |

|             | Delta power control for submodule SOC balancing within arm SOC              |     |

| 5.17        | Block diagram of current feedforward component calculation for battery      |     |

| F 10        | SOC balancing                                                               | 115 |

| 5.18        | Current feedforward component placement in battery current controller       | 11/ |

| <b>F</b> 10 | for battery SOC balancing                                                   | 116 |

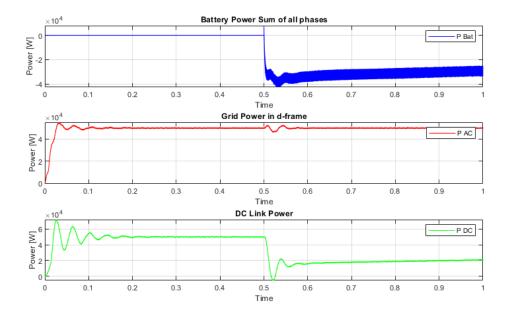

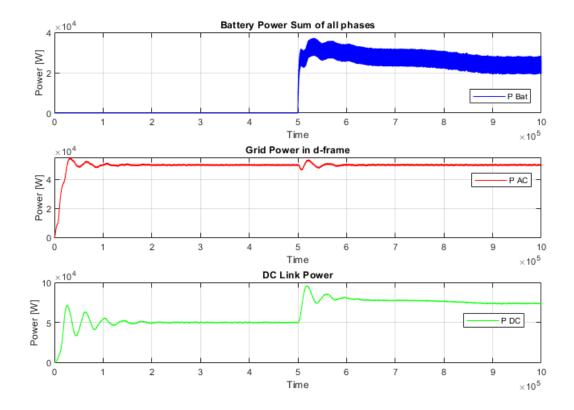

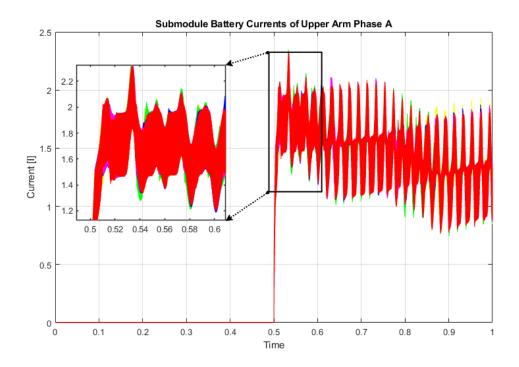

|             | Active power change during discharging of the battery                       |     |

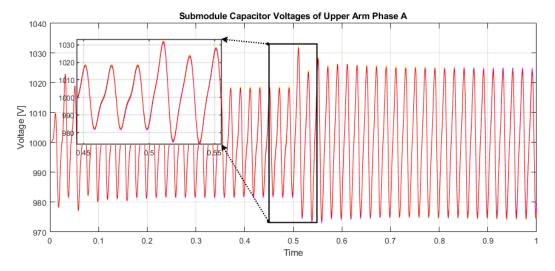

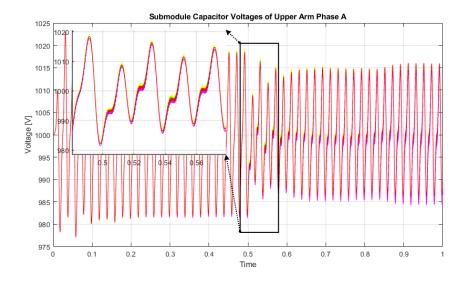

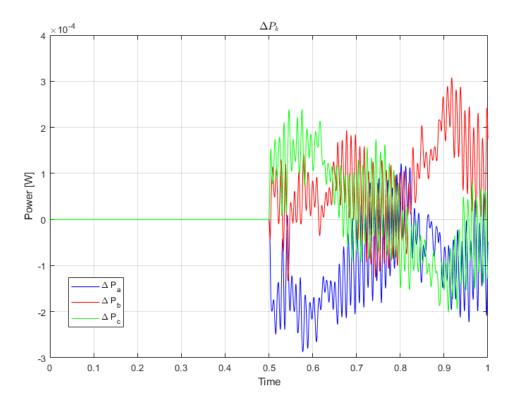

|             | Submodule Capacitor Voltage for Upper Arm Phase A (discharging)             |     |

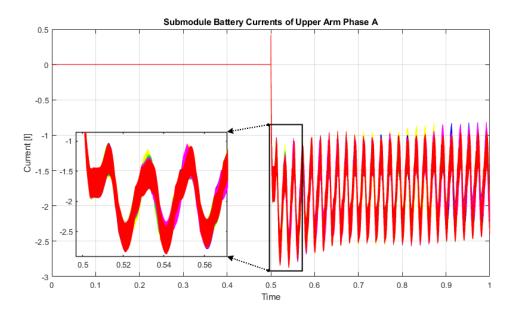

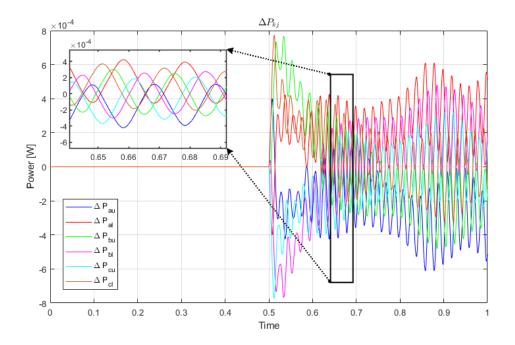

|             | Battery Currents Upper Arm Phase a (discharging)                            |     |

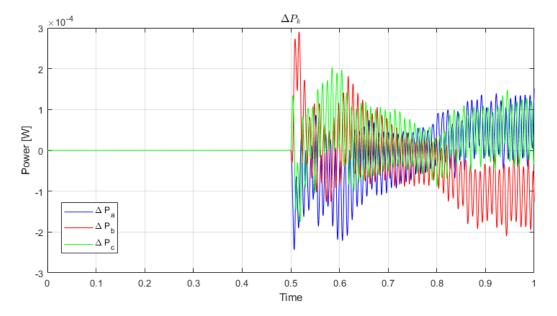

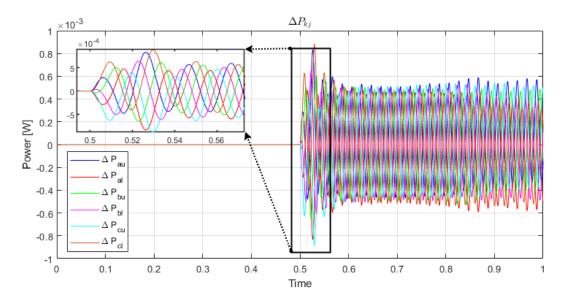

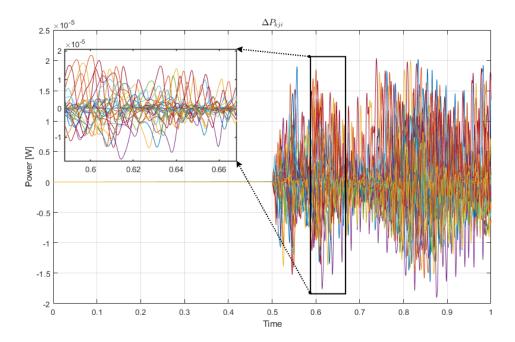

| 5.22        | $\Delta P_k$ (discharging)                                                  | 119 |

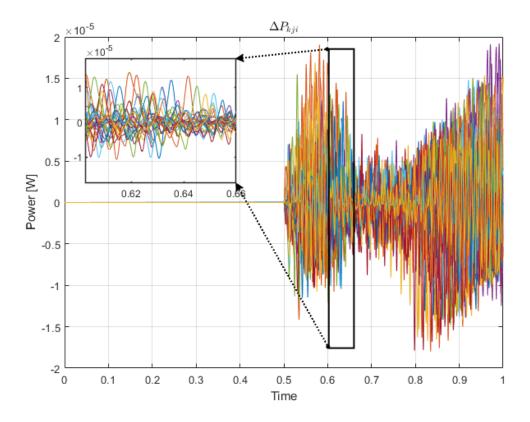

|             | $\Delta P_{kj}$ (discharging)                                               |     |

| 5.24        | $\Delta P_{kji}$ (discharging)                                              | 120 |

List of Figures viii

| 5.25 | Active power change during charging of the battery                                 | <u>'</u> 1 |

|------|------------------------------------------------------------------------------------|------------|

| 5.26 | Submodule Capacitor Voltages Upper Arm Phase a (charging) 12                       | 22         |

| 5.27 | Battery Currents Upper Arm Phase a (charging)                                      | 23         |

|      | $\Delta P_k$ (charging)                                                            |            |

|      | $\Delta P_{kj}$ (charging)                                                         |            |

|      | $\Delta P_{kji}$ (charging)                                                        |            |

| C.1  | Charging Profile Parameter Estimation Flowchart                                    | 10         |

| C.2  | Charge Profile of the collected data                                               | 1          |

|      | Individual Resting Pulse $V_{OCV}$ and $I$ (Instantaneous Response Highlighted) 14 |            |

| C.4  | Individual Resting Pulse $V_{OCV}$ and $I$ (Transient Response Highlighted) 14     | 12         |

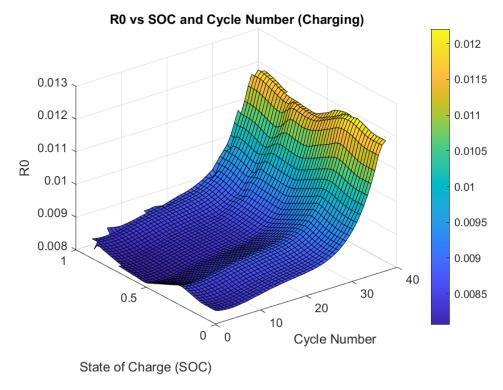

| C.5  | $R_0$ parameter over SoC and Cycle Number (Charging)                               | 13         |

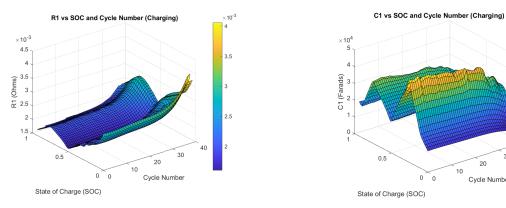

| C.6  | $R_1$ parameter over SoC and Cycle Number (Charging)                               | 13         |

|      | $C_1$ parameter over SoC and Cycle Number (Charging)                               |            |

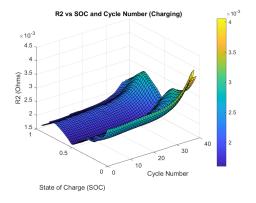

|      | R <sub>2</sub> parameter over SoC and Cycle Number (Charging)                      |            |

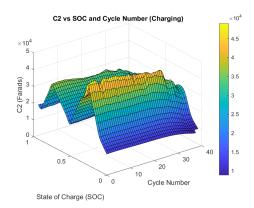

| C.9  | C <sub>2</sub> parameter over SoC and Cycle Number (Charging)                      | 14         |

## **List of Tables**

| 2.1 | Notable second-life battery projects [14]                            | 8   |

|-----|----------------------------------------------------------------------|-----|

| 2.2 | Comparison of 2 L + Tx, $3$ L + Tx, MMC and MMC + ITx [15]           |     |

| 4.1 | Comparison of MMC submodules [21]                                    | 32  |

| 4.2 | Modes of operation for a submodule in a MMC [21]                     | 33  |

| 4.3 | Power device voltage stress in different operation modes of MMC [23] | 36  |

| 4.4 | Power device voltage stress in different operation modes of MMC [23] | 36  |

| 4.5 | Comparison of Different Modulation Schemes for MMC                   | 46  |

| 4.6 | System Parameters                                                    | 48  |

| 4.7 | Final bidirectional DC-DC converter parameters                       | 62  |

| 4.8 | Simulated battery parameters                                         | 84  |

| 5.1 | Proportional and integral gains for dq controller                    | 98  |

| 5.2 | PR controller gains with fundamental and cutoff frequencies          | 100 |

| 5.3 | PI controller gains for phase leg average capacitor balancing        | 101 |

| 5.4 | Inner and outer PID controller gains                                 | 105 |

## **Preface**

This project was created by master students of the group APEL4-2-24 attending Aalborg University, Esbjerg. Anytime in the project the terms "we", "our" or "the group" is used, they refer to the student group listed below.

Aalborg University, 3rd June 2024

Rokas Sukauskis <rsukau17@student.aau.dk> Mykolas Poska <mposka18@student.aau.dk>

## Chapter 1

## Introduction

## 1.1 Grid Challenges

As the demand and integration of renewable energy systems is increasing, the industry is presented with new challenges. Demand fluctuation, the intermittent nature of renewable power generation, and the essential need for efficient energy storage solutions. One promising approach to maintaining the quality and reliability of the power system under these conditions is through the integration of Energy Storage Systems (ESS), with a particular focus on Battery Energy Storage Systems (BESS). BESSs are gaining attention due to the ongoing electrification of transportation and their potential to provide vital grid services, including load leveling, peak shaving, and facilitating the integration of renewable energy sources [1, 2].

## 1.2 Battery Energy Storage System

Batteries play a critical role in modern grid infrastructure, offering a flexible and scalable solution to energy storage challenges. As the grid transitions towards a more sustainable and renewable-centric model, the importance of battery storage is increasingly recognized. However, this surge in battery usage brings to the forefront the issue of battery waste and the environmental implications of battery production, usage, and disposal. Addressing these concerns is crucial for the sustainable growth of battery storage solutions and their continued role in enhancing grid stability and renewable energy integration.

## Chapter 2

## **Problem Analysis**

## 2.1 Grid Support Applications

As the use of renewable energy sources grows, the challenge of managing their inherently variable energy output becomes crucial. These renewable sources can produce differing amounts of electricity depending on the time of the day, making it essential to constantly balance electricity generation with consumption to ensure a stable power grid. This has brought grid support into focus as a key issue. Terms like flexibility and resilience are encompassed withing the grid support topic. Flexibility refers to the ability of power systems to adapt to changes and manage variations in electricity demand and supply, particularly from renewable sources. Resilience, on the other hand, is the power system's capacity to withstand and recover from disruptions, ensuring continuous and reliable service [3]. Some of the techniques used for grid support includes, peak shaving, voltage and frequency regulation and energy arbitrage.

As the electricity demand fluctuates throughout the day and the number of end-users rises, ensuring the grid's capacity to meet peak demands becomes crucial for its efficient and reliable operation. The growth in peak load presents challenges, including potential power outages and the escalating costs associated with electricity generation and transmission [4]. Traditional methods to manage peak demand involve cycling in conventional power plants, such as coal or gas power plants [5]. However, these facilities are burdened with high Operation and Maintenance (O&M) costs, substantial fuel consumption, and significant carbon dioxide emissions [4].

### 2.1.1 Peak Shaving

In response to these challenges, peak shaving is becoming an important area of research. Peak shaving is a technique that is used to level out the increased peaks in electricity use, that occurs when there is an increased demand of power by industrial and commercial consumers. By reducing peak electricity demand, the strain on the grid is lessened,

leading to lower operational costs and enhanced system reliability. Implementing peak shaving benefits grid operators by improving power quality, promoting efficient power utilization, enabling cost reductions, and facilitating the integration of renewable energy sources. End-users also gain through reduced electricity costs [4, 6, 7].

Research into peak shaving strategies includes exploring ESS, vehicle-to-grid (V2G) technologies, and Demand Side Management (DSM). ESS, in particular, offers promising potential for peak shaving by storing energy during off-peak times for use during peak periods. This approach not only mitigates the need for high-demand power generation but also contributes to overall electricity cost reductions. Various ESS technologies, such as BESS and Second-Life Battery Energy Storage Systems (SLBESS), are under consideration [4].

#### 2.1.2 Voltage and Frequency Regulation

Renewable energy sources are designed to supply power to the grid within a specified voltage and frequency, and cease to produce power when exceeding these specified limits. These limits are country specific. Transmission System Operators (TSOs) develop Grid Codes (GCs) [8]. These are necessary to integrate and adopt renewable energy systems. As the technology advances, the GCs are constantly updated. The requirements set by the GC typically focus on a single active feature at any given time. These requirements encompass the following:

- Reduction of the active power for over frequency and increase of the active power for under frequency as a response to frequency variation.

- In static grid support, the power generator must adhere to adjustable reactive power settings. This involves maintaining either a constant power factor (PF) or reactive power (Q), where Q changes based on grid voltage variations, denoted as Q(v). The PF can vary according to the active power operation, represented as  $\cos\phi$  (P).

- Dynamic grid support, such as low and high voltage ride-through capabilities, requires the power generator to supply reactive current according to a specific voltage transient curve.

The compliance with relevant GCs are mandatory [9]. To keep the renewable energy systems running within the specified limits, techniques for voltage and frequency regulation are employed. Voltage regulation ensures the voltage supplied to end-users remains within a predetermined range, mitigating fluctuations in electricity demand or generation. This regulation is critical for the protection of electrical appliances and the maintenance of consistent power quality. Frequency regulation, in contrast, aims to balance electricity generation and consumption across the grid, maintaining the system frequency at a standard value, typically 50 or 60 Hz, depending on the geographical

region. These mechanisms are essential for the stability and efficiency of the electrical supply system, ensuring reliable and safe electricity distribution. For the implementation of voltage and frequency regulation, ESS can be used. In [9], two methods for the power control, P(f) and combined P(f) - Q(v) are reviewed. The P(f) active power control method, that is responsive to line frequency variations. This method works by automatically adjusting the power flow direction of the ESS converters in response to frequency changes. Active power adjustment works by either injecting power into the grid (if the frequency is below a specified threshold) or absorb power from the grid (if the frequency is above a specified threshold), this way stabilizing the grid's frequency. As renewables are inherently a variable source of energy, the P(f) strategy offers flexibility, meaning that the ESS converters can dynamically transition from receiving power to generating power or vice versa. The P(f) - Q(v) power control strategy adds to the active power control method P(f), by including a reactive power control component Q(v). The added reactive power control component Q(v) focuses on reactive power control in regards to voltage fluctuations. By modulating reactive power it aims to maintain the voltage levels within a specific threshold. This control method can be implemented both in single - phase and three - phase distributed ESS converters without the need for communication protocols with the TSO.

### 2.1.3 Energy Arbitrage

Energy arbitrage refers to the practise of utilizing the energy price market, by purchasing, storing and selling energy based on the demand of it. Not only does this technique provide a financial benefit to the energy storage operators, it is used for grid support applications, by balancing the supply and demand on the grid. For the storage of energy, ESS are of interest. As previously mentioned, ESS are applicable for a wide range of grid support applications, however, energy arbitrage offers the largest profit opportunity for ESS [7, 10].

### 2.2 Batteries for Grid Support

Mentioned in Section 2.1 were the grid support applications, which emphasized the use of ESS. There are many different ESS for grid support. They come in different forms of energy storage such as mechanical, thermal, electrical, chemical or electrochemical [7, 11]. Emphasis is put on the electrochemical type of energy storage, particularly Li-ion, due to the potential re-usability for second-life applications.

#### 2.2.1 Electrochemical Energy Storage

Electrochemical energy storage for grid support is a fast growing and diverse sector which is crucial for grid-connected system stability, reliability and safety. Electrochemical energy storage involve conversion of electrical energy into chemical energy for storage and back into electrical energy whenever needed. There are many different types of chemistries and systems used in electrochemical batteries all with different characteristics, advantages and applications. For example, Li-ion batteries store energy through movement of lithium ions between anode and cathode during charge and discharge cycles. They are known for high energy density and long life cycle. Li-ion batteries are used in portable electronics, electric vehicles and grid support applications such as peak shaving, load leveling and renewable energy integration. Lead-Acid batteries, one of the oldest types of rechargeable batteries, store energy through chemical reactions between lead, lead dioxide and sulfuric acid. They are known for high power capacity, low cost and robustness. Other forms of electrochemical energy storage, such as flow or solidstate batteries, are getting more attention both in research and industry. Flow batteries differ from conventional batteries by storing chemical energy in external tanks and convert it to electricity in electrochemical cells which allows for energy capacity decoupling from power capacity meaning increasing size of tanks can increase energy capacity independently of power output. Such type of batteries are useful for long-duration energy storage such as renewable energy integration and grid stabilization over several hours or days. Solid-state batteries are interesting due to the fact that they replace the liquid or gel electrolytes with solid material. They promise higher energy densities, improved safety and longer lifespans. While still mostly in development phase, solid-state batteries are expected to revolutionize electric vehicle industry and portable electronics due to improved performance and safety features [7].

### 2.2.2 SLBs in Grid-Support Applications

Electric vehicle (EV) batteries typically retain about 80% of their capacity at the end of their primary vehicular use, a point defined by the US Advanced Battery Consortium (USABC) as a 20% loss in capacity or power density at an 80% depth of discharge (DOD)

[7, 12]. This residual capacity, while not suitable for vehicular propulsion, is quite adequate for stationary energy storage systems. Research suggests that the daily transportation needs of American drivers could be met with batteries that have as little as 30% of their original capacity, indicating that the USABC's 80% threshold may have more significant implications for plug-in hybrid electric vehicles.

The transition of EV batteries to their "second life" occurs either due to capacity degradation or when the vehicle's service life ends before the battery's. These second-life batteries, which offer a cost-effective alternative to new ones, are influenced by factors such as cost, environmental impact, and aging. Despite the increasing use of lithiumion batteries in EVs and their advantages over lead-acid batteries, particularly in high-capacity applications, the recycling process for lithium-ion is less mature and more complex. Recycling costs are high because materials like lithium, which make up only 2-7% of the battery's weight, are five times more expensive to recycle than to source new, and cobalt recycling may soon be unnecessary due to advances in battery technology.

The expected lifespan of EV battery packs is about 8 years. Analyzing the market's offerings, the average capacity (34.21 kWh), and the number of batteries from 2018 (165,410 units), projections indicate that around 4526.94 MWh will be available from second-life batteries by 2026. It is estimated that by 2040 around 3.4 million kilograms of lithium-ion EV battery cells could enter the waste stream [13].

For energy storage, a used Nissan Leaf battery, for example, can retain 80% of its initial energy, equating to about 15 kWh suitable for low C-rate applications for years. Projections state that by 2028, 548 GWh of battery capacity from used EV batteries will be globally available, with China accounting for approximately 240 GWh [13].