Convolutional Neural Network

Master's Thesis

Albert Berg Hansen & Simon Dahl Jepsen

Electronic Systems, ES10, 05/2024

#### **Master's Thesis**

Electronic Systems Fredrik Bajers Vej 7A 9220 Aalborg Øst

http://www.tech.aau.dk

#### Title:

A Benchmarking Tool for Evaluation of Approximate Arithmetic Circuits in Convolutional Neural Networks

#### **Project:**

Master's Thesis

#### **Project period:**

Feb 2024 to May 2024

#### **Group:**

ES 1023

## **Participants:**

Albert Berg Hansen Simon Dahl Jepsen Supervisors:

Jan Østergaard

Pages:

219

Appendices:

5

Date of Upload:

31-05-2024

## **Abstract/Summary**:

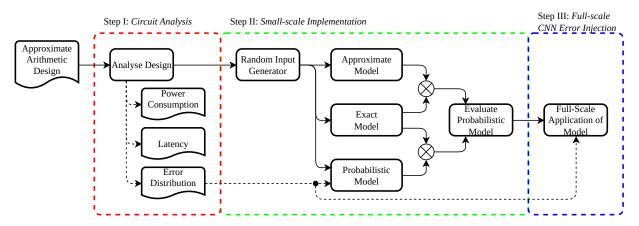

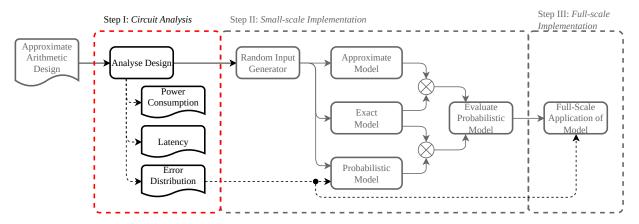

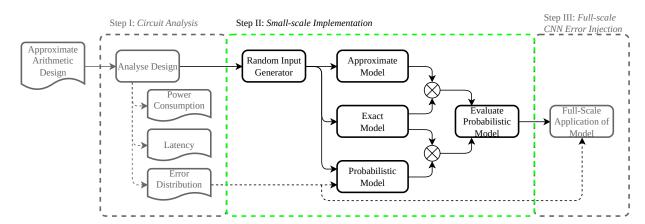

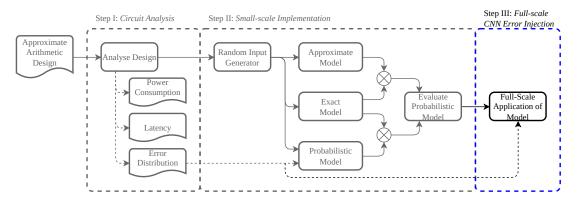

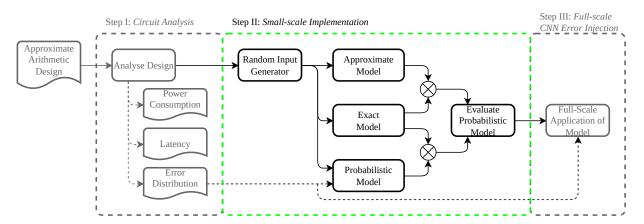

The contents of this thesis describes the development of a *benchmarking tool* capable of taking an approximate, combinatorial arithmetic circuit and analysing the power consumption, latency, error characteristics, and implications of implementation on a given CNN. The purpose of the tool is to bridge the gap between approximate computing and machine learning, leveraging the reduction in power consumption and latency, in an attempt to make machine learning more sustainable. The benchmarking tool is structured in three steps. In step I, the arithmetic circuit is synthesised and the netlist is used to count the logic gates and their type, and by extension estimate the total amount of transistors required for the circuit. The netlist is also used to find the latency of the circuit by converting the netlist to a directed acyclic graph and searching for the path that results in the longest propagation delay. In step II the circuit is applied to a small-scale custom CNN implemented in C++. The error characteristics are generalised in easily scalable custom CNN layers, and the C++ model is utilised to evaluate the "appropriateness" of the generalisation. Lastly, in step III the custom layers are used in a full-scale CNN, whereby the implications on the accuracy can be weighed against the drop in power consumption and latency. The custom layers were applied in a full-scale example CNN, where the potential of approximate hardware was highlighted: The accuracy reduced form ~ 70 % to ~ 60 %, however, with an optimistic estimate the **power consumption** dropped to 10.3 % and the latency dropped to below half.

The contents of the report are openly accessible, but publication with source reference may only occur in agreement with the author(s).

# **Preface**

This Master's Thesis was written as a part of the *Electronic Systems* Master's programme at Aalborg University (AAU). The learning objectives for this module are summarised in the following paragraphs.

**Knowledge:** Have knowledge of the highest international level of research within a selected field of relevancy with *electronic systems* and comprehension w.r.t. research ethics.

**Skills:** Be able to argue the relevancy of the chosen problem and its context. Account for the scientific basis of the problem and methods to solve it. Analyse and describe the problem of choice, applying relevant theories, methods, and experimental data.

**Competences:** Be able to communicate scientific problems orally and in writing to specialists as well as non-specialists. Be capable of handling complex and unpredictable situation, which require new solutions, professional development and/or collaboration. Be able to independely initiate and take responsibility for collaboration and profession development, and specialisation.

# **Reading Guide**

The thesis is written in chapters following a somewhat chronological order. In chapter 1 the chosen problem is described on a high-level basis, where the reader should be able to familiarise themselves with the chosen problem, and how the thesis will approach the solution. In chapter 2 the fundamental theories and methods relevant to the development of the solution are presented as a survey, and sections can be skipped if the reader is familiar with the subject; nothing is designed, implemented, or tested within this chapter. In chapter 4, 5, and 6 the solution is developed, important test results are presented, and reflections w.r.t. the solutions are described. chapter 7 seeks to discuss choices made during the development, the consequences, and possibly alternatives that might better the solution. chapter 8 summarises the solution as *a singular product* and contextualises the solution to the chosen problem. In chapter 9 topics and paths are highlighted, that would have been relevant to research or develop if more time was available. The appendices describe the most important tests performed throughout the development, however, the most important conclusions, data, and figures have been integrated into the relevant chapters.

In GitHub References a file tree can be found. The file tree refers to the Github page holding the files, scripts, data etc. used in the project. The GitHub directory tree is in an early stage and somewhat unmanageable, however, when relevant/important the path of scripts, data, etc. is explicitly stated and should be reachable from the appendix.

To improve the reading experience and provide navigation tools to the reader, references/ citations will (if possible) be clickable. Clicking on citations will move the reader to the Bibliography, clicking

on links will guide the reader to a browser, and clicking an internal reference will move the reader to the referenced item (table, figure, etc.).

This report includes a Table of Contents and a List of Figures. Every chapter, section, subsection, and figure will be referenced with a hyperlink ensuring proper overview.

Citations will follow the *Vancouver style*, and will thus be numbered (starting from 1 going up) in accordance with the order they are cited in the text. Clicking on the citation will take the reader to the Bibliography where the title, author, and other relevant information will be provided.

Due to the subject matter acronyms are frequently used and to avoid misconceptions a list of relevant acronyms (and their expanded forms) is present just after the bibliography (Acronyms).

The equations and formulas included in this report will follow the ISO 80000 standard whenever possible, however, to avoid ambiguity from figures to text the decimal separator will be "." and the thousands separator will be ",". Typesetting will also follow the ruleset described in Table 1 in order to clearly distinguish between symbols and units.

| Subject        | Typeset      | Examples                                                         |

|----------------|--------------|------------------------------------------------------------------|

| Numbers        | Ordinary     | $1, 2, 3, 10^{-24}$                                              |

| Symbols        | Math cursive | V, A, F, c, l                                                    |

| Units          | Ordinary     | volt, V, A, N, kg                                                |

| Function calls | Ordinary     | cos(x), $log(x)$ , $exp(x)$ , $arcsin(x)$                        |

| Words          | Ordinary     | $\lambda_{ m V} = rac{ m final\ voltage}{ m starting\ voltage}$ |

| Greek letters  | Cursive      | $	au, \mu, eta, \Omega$                                          |

| Indices        | Ordinary     | $N_{ m max}$ , $P_{ m effective}$ , $V_{ m in}$ ,                |

| Constants      | Ordinary     | e, c, i, j                                                       |

**Table 1:** Typesetting for equations with examples.

When appropriate, the unit of the outcome of an equation will be placed in square brackets on the lefthand side of the formula numbers. All equations will be left aligned to the same margin and be followed by a description of all included variables.

Arithmetic for bit-sequences requires additional mathematical symbols to avoid ambiguity w.r.t. the performed operations:

- ⊕ Addition with modulo 2

- Concatenation

- ← Replace lefthand value with righthand value

- ∧ Bitwise AND

- ∨ Bitwise OR

The footnotes will follow MLA style and be used for tangential information. Citations will never be presented as footnotes but will be displayed as described before.

# **Contents**

| 1 Introduction |                     |                                                                                | 1                    |

|----------------|---------------------|--------------------------------------------------------------------------------|----------------------|

| 2              | Surv                | vey                                                                            | 5                    |

|                | 2.1                 | Neural Networks                                                                | 5                    |

|                |                     | 2.1.1 Perceptrons                                                              | 6                    |

|                |                     | 2.1.2 Multilayer Perceptrons                                                   | 9                    |

|                |                     | 2.1.3 Training Perceptrons                                                     | 10                   |

|                |                     | 2.1.4 State-of-the-Art Neural Networks                                         | 12                   |

|                | 2.2                 | Digital Design                                                                 | 16                   |

|                |                     | 2.2.1 Number representation                                                    | 17                   |

|                |                     | 2.2.2 Arithmetic in Computer Systems                                           | 19                   |

|                |                     | 2.2.3 The Multiply-Accumulate Unit (MAC)                                       | 24                   |

|                |                     | 2.2.4 State-of-the-Art Arithmetic Units                                        | 25                   |

|                | 2.3                 | Approximate Computing                                                          | 33                   |

|                |                     | 2.3.1 Approximate Software                                                     | 33                   |

|                |                     | 2.3.2 Approximate Hardware                                                     | 34                   |

|                | 2.4                 | Summary of the Survey                                                          | 38                   |

| 3              | <b>A Be</b> 3.1 3.2 | Penchmarking Tool for Approximate Arithmetics  Functional Overview of the Tool | 40<br>41<br>42<br>43 |

| 4              | Sten                | I: Circuit Analysis                                                            | 44                   |

|                | 4.1                 | Gates, Transistors, and Delay                                                  | 46                   |

|                | 4.2                 | RTL Synthesis: Gatecount and Critical Path Delay                               | 47                   |

|                |                     | 4.2.1 Synthesis Flow                                                           | 48                   |

|                |                     | 4.2.2 Counting the Gates                                                       | 50                   |

|                |                     | 4.2.3 Critical Path                                                            | 51                   |

|                | 4.3                 | Error Simulation                                                               | 53                   |

|                | 4.4                 | Circuit Comparison and Summary                                                 | 54                   |

| 5              | Sten                | o II: Small-Scale Approximate Neural Network                                   | 57                   |

|                | 5.1                 | Exact Model - Reference System and Application                                 | 58                   |

|                |                     | 5.1.1 Preliminary Phase                                                        | 58                   |

|                |                     | 5.1.2 Design Phase                                                             | 60                   |

|                |                     | 5.1.3 Implementation Phase                                                     | 62                   |

|                | 5.2                 | Approximate Model - Approximate Forwardpass in a Convolutional Neural Network  | 64                   |

|                |                     | 5.2.1 Convolutional Layers                                                     | 67                   |

Chapter 0 CONTENTS

|    |        | 5.2.2 Fixed-Point Precision Scaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 68  |

|----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | 5.3    | Probabilistic Model - Modelling Errors in Forward Propagation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 69  |

|    |        | 5.3.1 Modelling Errors of Approximate MAC-operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70  |

|    |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 72  |

|    | 5.4    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 75  |

|    |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 82  |

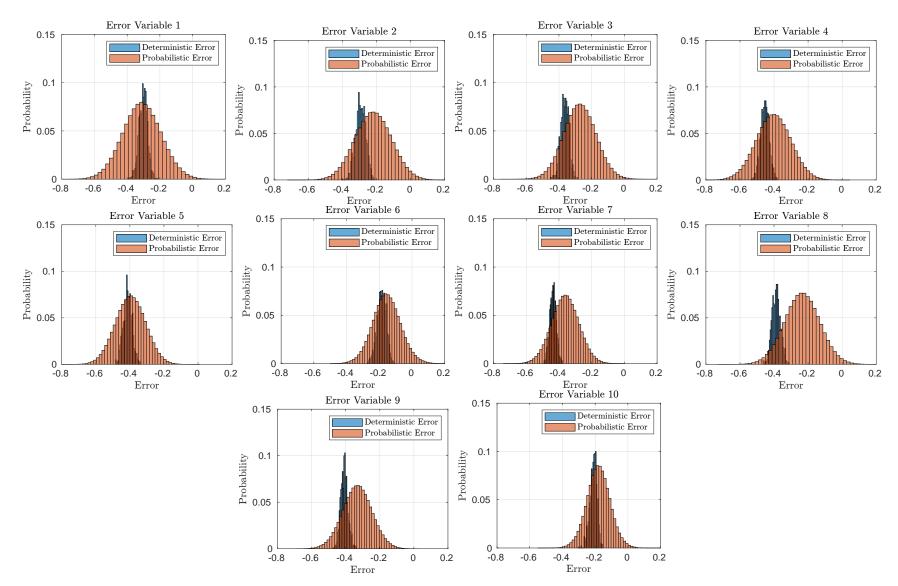

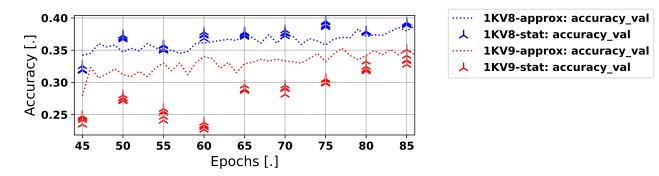

|    | 5.5    | Investigation of Congruency Between Probabilistic and Deterministic Modelling .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 82  |

|    | 5.6    | Summary, Reflection, and Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 88  |

| 6  | Step   | III: Full-Scale CNN Error Injection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 89  |

|    | 6.1    | Interacting with the Benchmarking Tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 90  |

|    |        | 6.1.1 Performing Step I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 90  |

|    |        | 6.1.2 Performing Step II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 90  |

|    |        | 6.1.3 Performing Step III                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 91  |

|    | 6.2    | Applying the Custom Layers to a Full-scale CNN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 91  |

| 7  | Disc   | cussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 94  |

|    | 7.1    | Step I - Circuit Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 95  |

|    | 7.2    | Step II - Small-scale approximate neural network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 96  |

|    | 7.3    | Step III - Full-scale CNN Error Injection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 97  |

| 8  | Con    | clusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 99  |

| 9  | Furt   | ther Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 103 |

| Bi | bliogi | raphy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 104 |

| Ac | ronyı  | 5.3.1       Modelling Errors of Approximate MAC-operations       70         5.3.2       Adding Error to the CNN       72         Training the CNN with Approximate Arithmetic       75         5.4.1       Considerations/Reflections when Training the Approximate Model       82         Investigation of Congruency Between Probabilistic and Deterministic Modelling       82         Summary, Reflection, and Considerations       88         III: Full-Scale CNN Error Injection       89         Interacting with the Benchmarking Tool       90         6.1.1       Performing Step I       90         6.1.2       Performing Step II       90         6.1.3       Performing Step III       91         Applying the Custom Layers to a Full-scale CNN       91         Inssion       94         Step I - Circuit Analysis       95         Step II - Small-scale approximate neural network       96         Step III - Full-scale CNN Error Injection       97         Islusion       99         ner Work       103         aphy       104         ns       113         xA Github References       115         Defining small CNN for benchmarking       116         Selection of Approximate Circuits for Comparing Metrics< |     |

| Аp | pend   | lix A Github References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 115 |

| Аp | p. B   | Defining small CNN for benchmarking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 116 |

| Аp | p. C   | Selection of Approximate Circuits for Comparing Metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 138 |

| Аp | p. D   | Training an Approximate Arithemetic Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 173 |

| Аp | p.E    | Testing the Probabilistic Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 187 |

# **List of Figures**

| 1.1  | Distribution of foci from papers                                                          | 3  |

|------|-------------------------------------------------------------------------------------------|----|

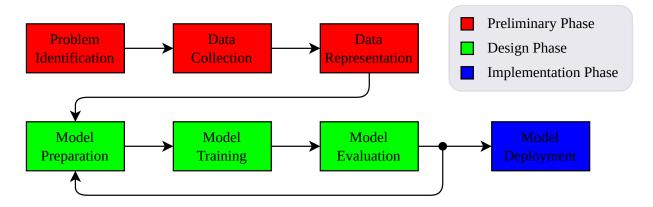

| 2.1  | Neural networks from <i>problem identification</i> to <i>model deployment.</i>            | 6  |

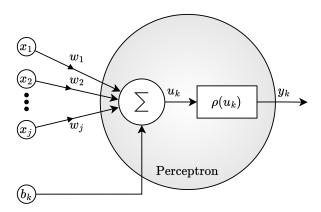

| 2.2  | A Perceptron                                                                              | 6  |

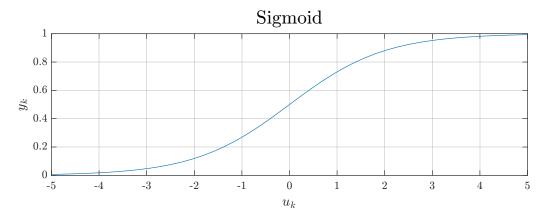

| 2.3  | Sigmoid Function                                                                          | 8  |

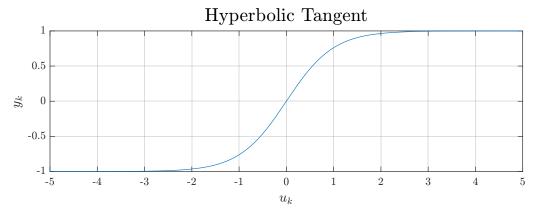

| 2.4  | Hyperbolic Tangent Function                                                               | 8  |

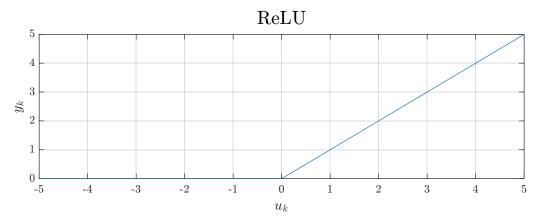

| 2.5  | ReLU Function                                                                             | 9  |

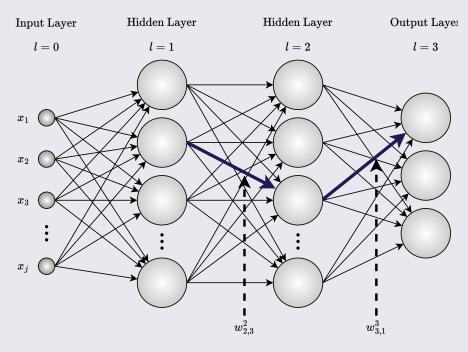

| 2.6  | Two-Layer Fully Connected Neural Network                                                  | 10 |

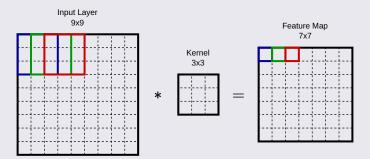

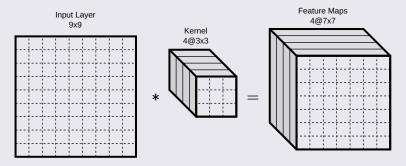

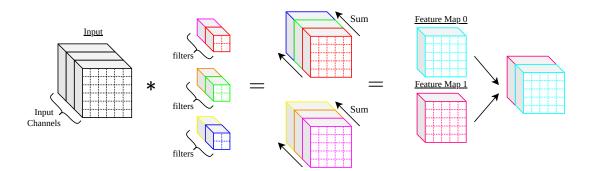

| 2.7  | Illustration of a two-dimensional convolution layer, using a single kernel                | 13 |

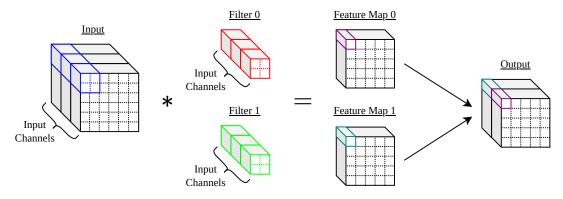

| 2.8  | Illustration of an example convolutional layer, using four kernels resulting in four FMs. | 13 |

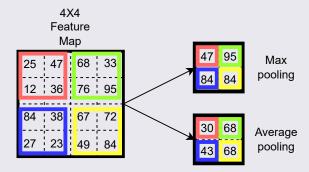

| 2.9  | Illustration of both max- and average-pooling based on an FM with arbitrary values        | 14 |

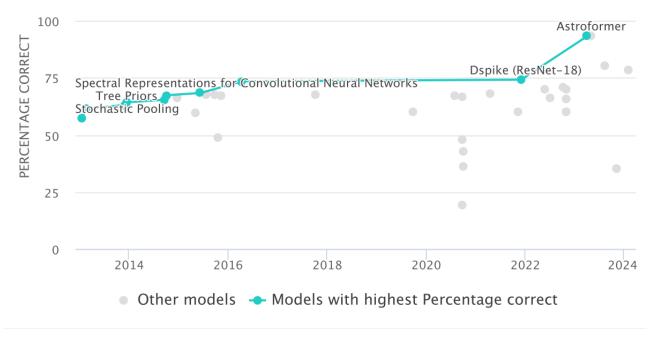

| 2.10 | Overview of best-performing networks in terms of accuracy, performing image classific-    |    |

|      | ation on CIFAR-100 without using extra data (image taken from paperwithcode.com).         | 15 |

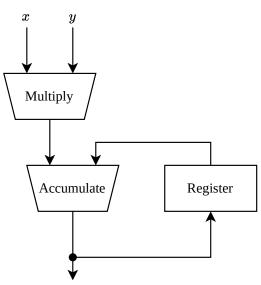

|      | MAC unit                                                                                  | 16 |

| 2.12 | Intervals of representable values using 3 integer bits, no fractional bits, and signed/   |    |

|      | unsigned                                                                                  | 17 |

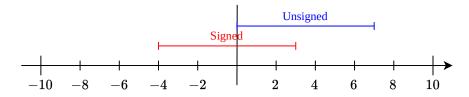

|      | IEEE 754 binary32 number representation (single-precision float)                          | 19 |

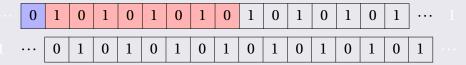

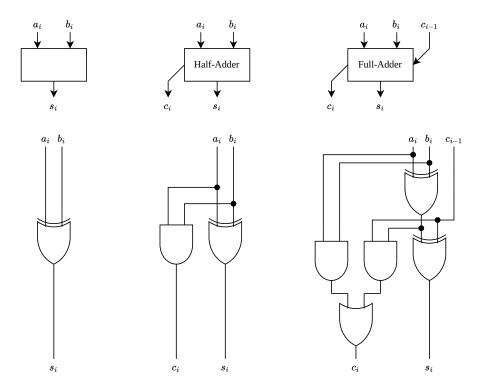

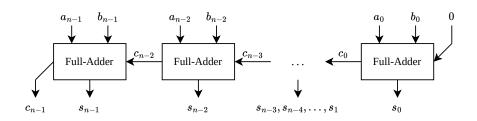

|      | 2-bit adders                                                                              | 20 |

|      | Adder consisting of a series of full-adders                                               | 20 |

|      | Long-multiplication of $32 \cdot 132$ in decimal                                          | 21 |

|      | Long-multiplication of $9 \cdot 7$ in binary                                              | 21 |

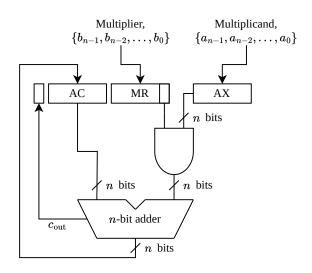

|      | Sequential multiplier                                                                     | 22 |

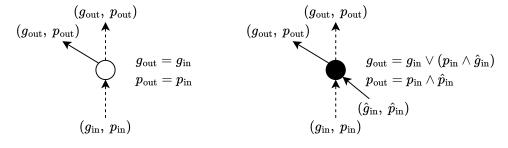

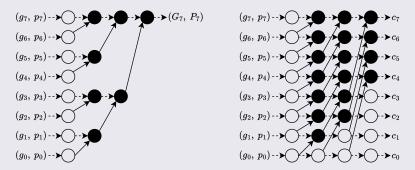

|      | Brent-Kung Adder nodes                                                                    | 26 |

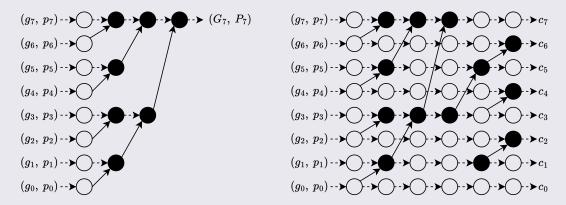

|      | Brent-Kung adder carry tree                                                               | 27 |

|      | Kogge-Stone adder carry tree.                                                             | 28 |

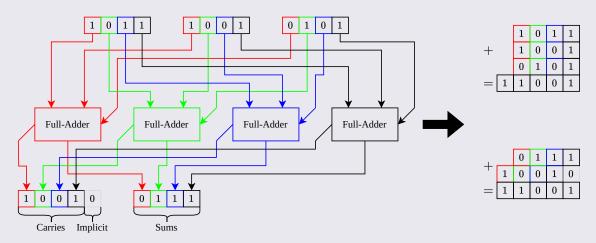

|      | Example of a 3:2 pseudo-adder consisting of 4 full-adders                                 | 29 |

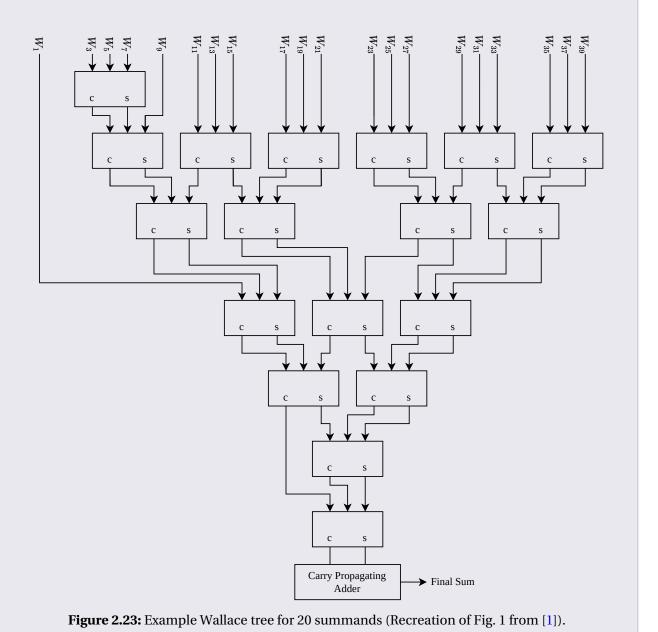

|      | Example Wallace tree for 20 summands (Recreation of Fig. 1 from [1])                      | 30 |

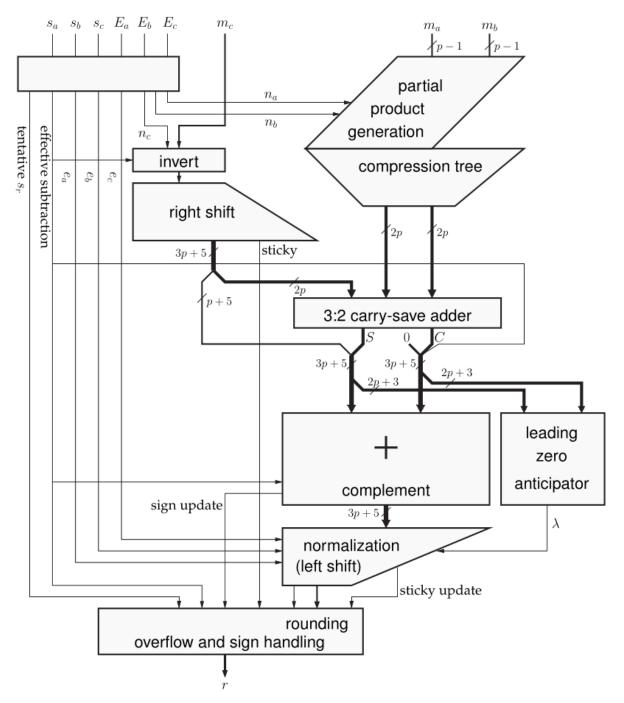

| 2.24 | The classical single-path FMA architecture from the IBM RS/6000 [2]                       | 32 |

| 3.1  | Functional diagram of the <i>benchmarking tool</i>                                        | 41 |

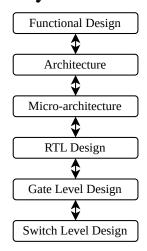

| 4.2  | Different levels of abstraction in digital design, inspired by Fig 1.2 from [3]           | 47 |

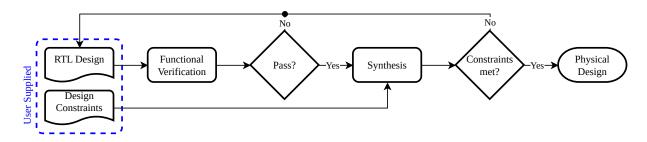

| 4.3  | Generic simulation and synthesis flow                                                     | 47 |

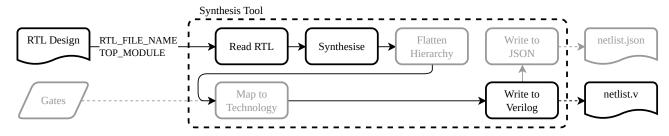

| 4.4  | Synthesis flowchart                                                                       | 48 |

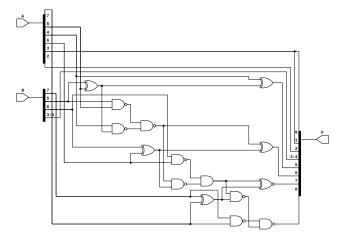

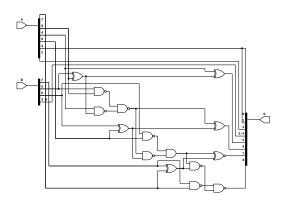

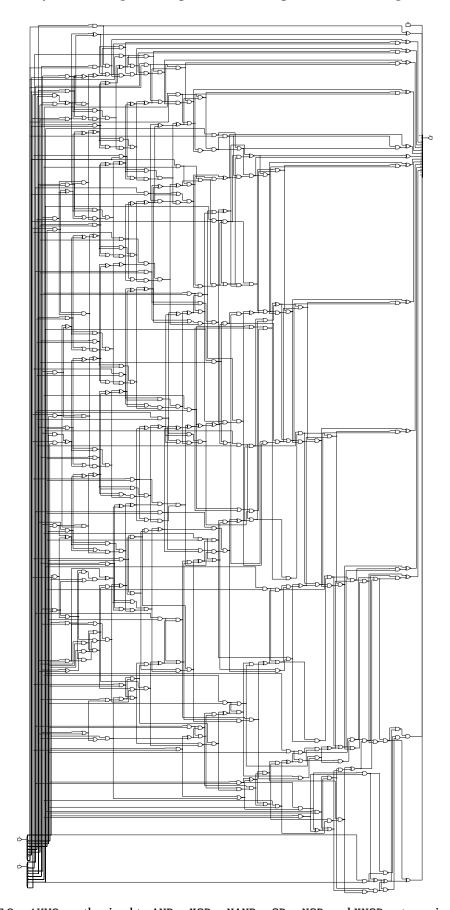

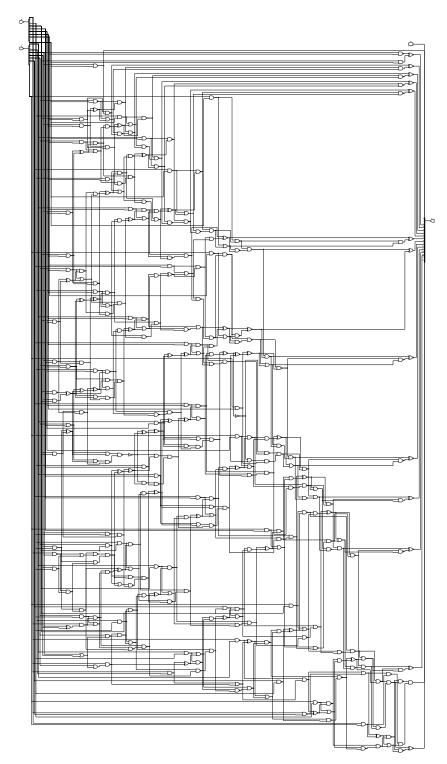

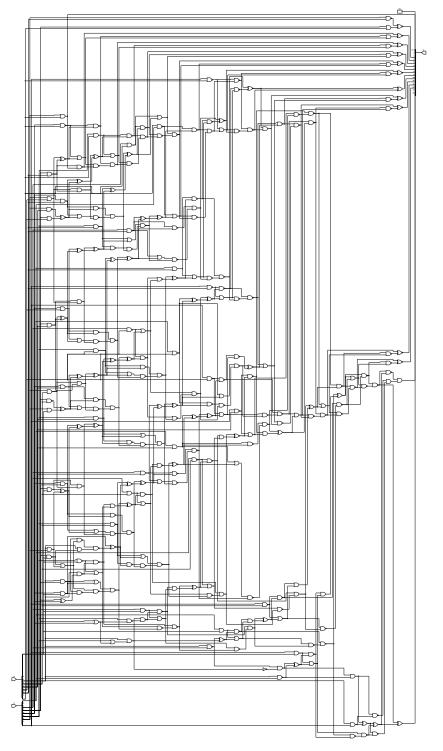

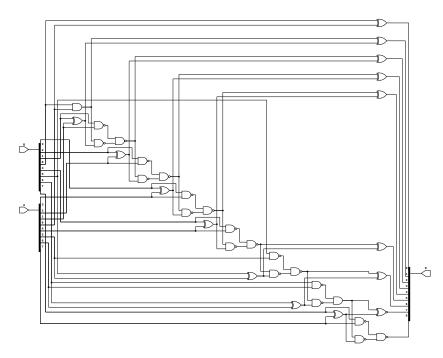

| 4.5  | add8se_8VQ from EvoApproxLib [4] synthesised to AND, XOR, NAND, OR, NOR and               |    |

|      | XNOR gates using netlistsvg                                                               | 49 |

| 4.6  | add8s_8VQ from EvoApproxLib [4] synthesised to AND and NOT gates and visualised using     |    |

|      | netlistsvg                                                                                | 50 |

| 4.7  | add8s_8VQ from EvoApproxLib [4] synthesised to OR and NOT gates and visualised using      |    |

|      | netlistsvg                                                                                | 50 |

Chapter 0 LIST OF FIGURES

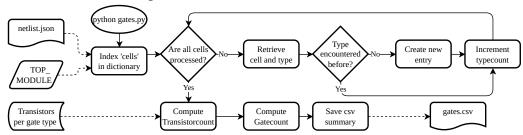

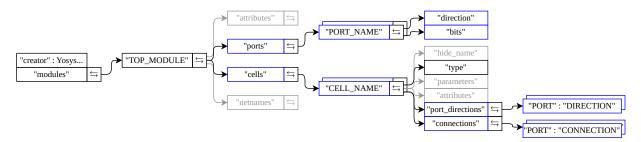

| 4.8        | netlist.json data-structure for counting gates                                                    | 50  |

|------------|---------------------------------------------------------------------------------------------------|-----|

| 4.9        | Gatecount flowchart                                                                               | 50  |

| 4.10       | netlist.json data-structure for the critical path                                                 | 51  |

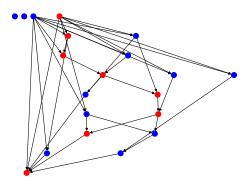

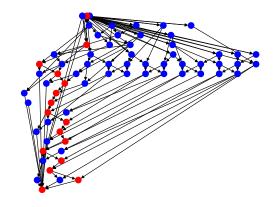

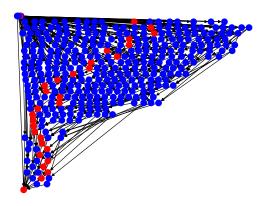

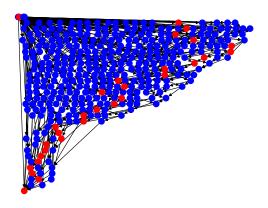

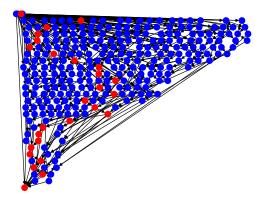

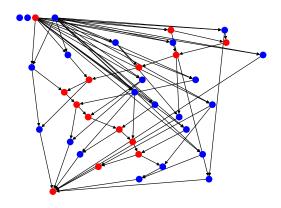

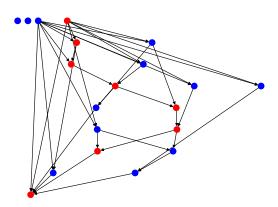

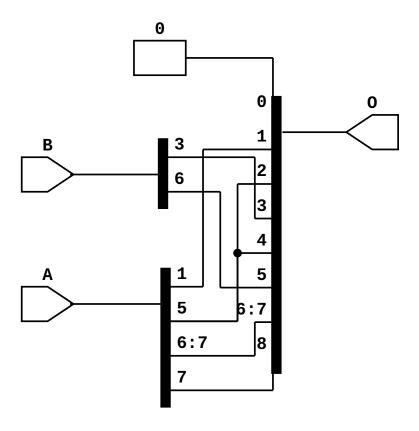

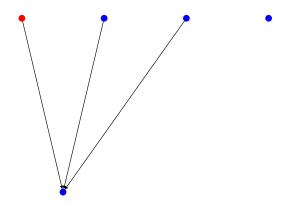

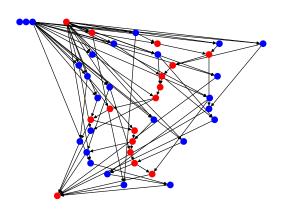

| 4.11       | Example translation of a <i>combinatorial logic circuit</i> into a DAG                            | 52  |

| 4.13       | Visualisation of the DAG representation of Figure 4.12                                            | 52  |

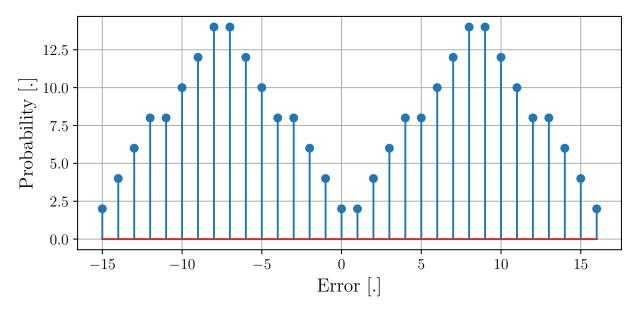

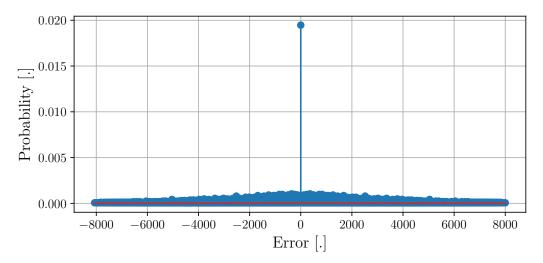

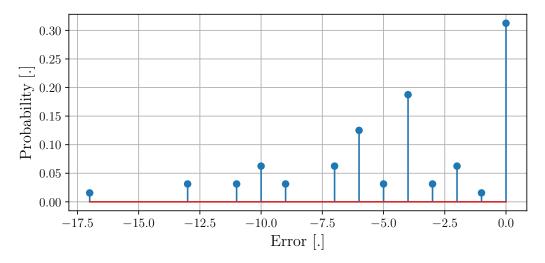

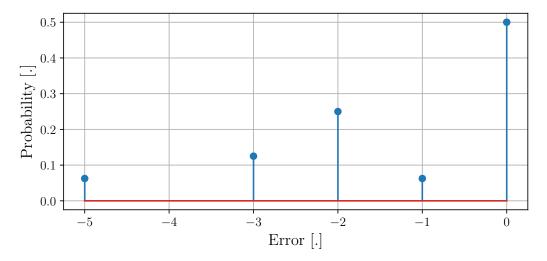

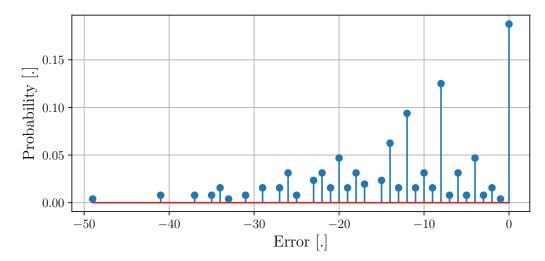

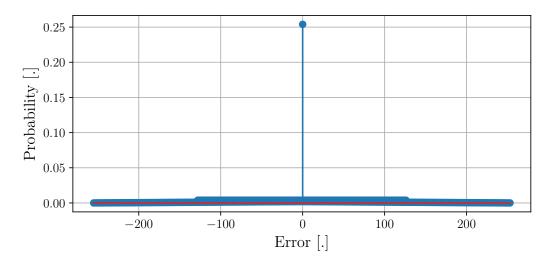

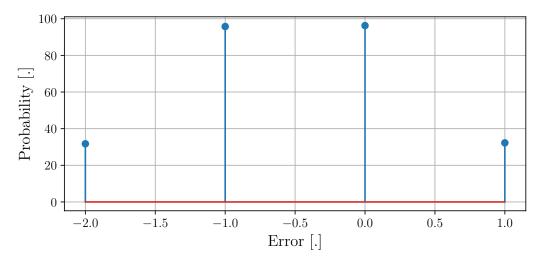

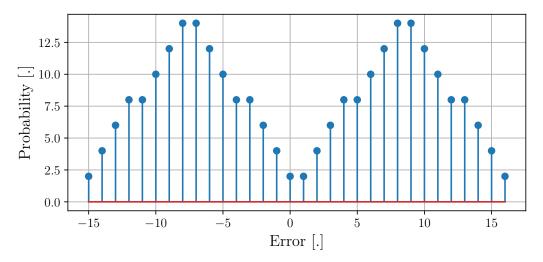

| 4.14       | PMF of the error distribution of the approximate circuit in Figure 4.5                            | 54  |

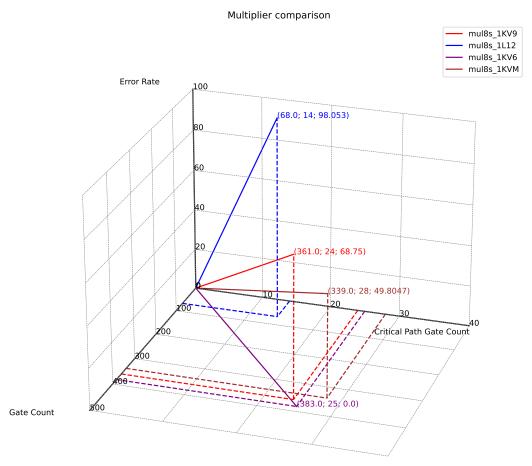

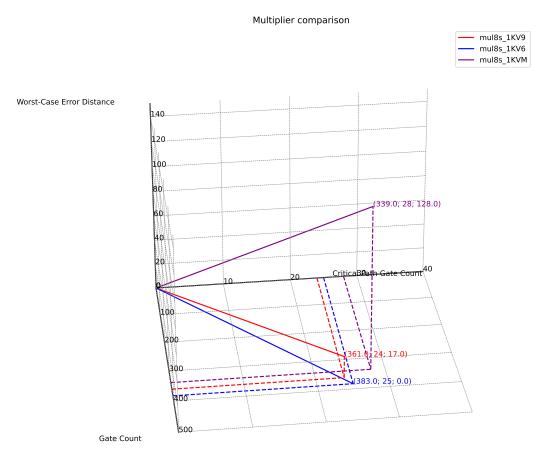

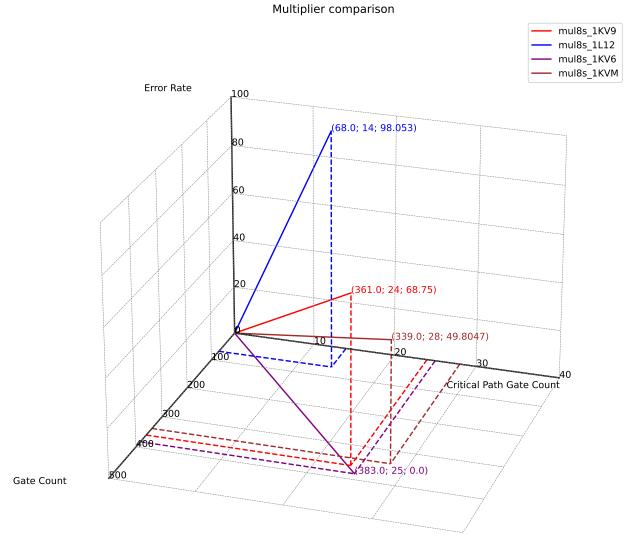

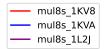

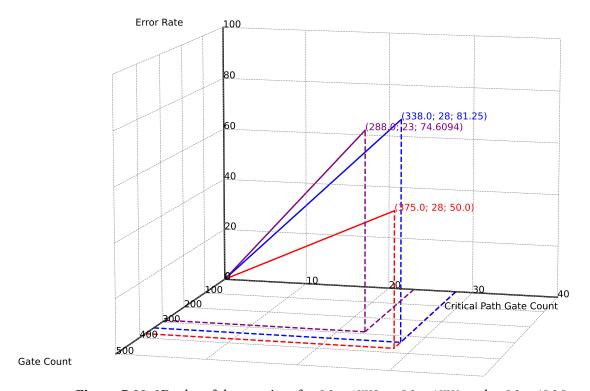

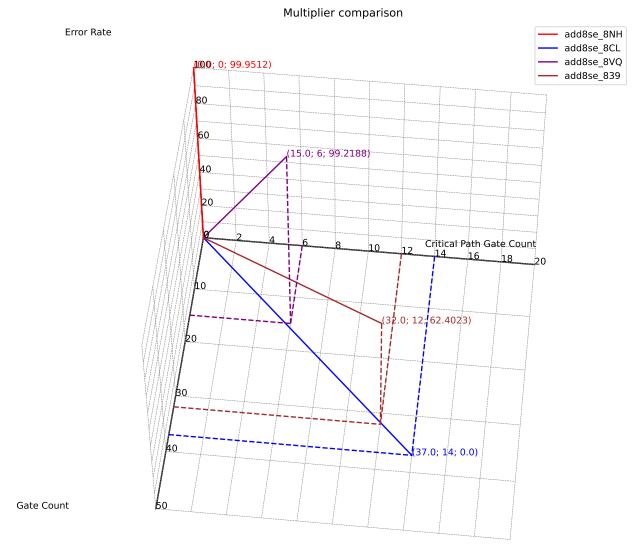

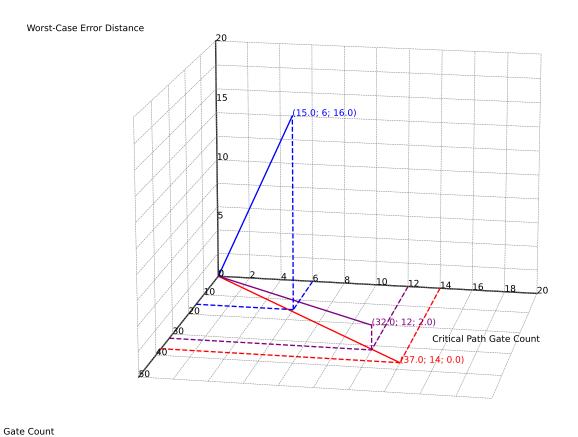

| 4.15       | 3D-plot of the metrics of mul8s_1KV9, mul8s_1KVM, mul8s_1L12, and mul8s_1KV6                      | 55  |

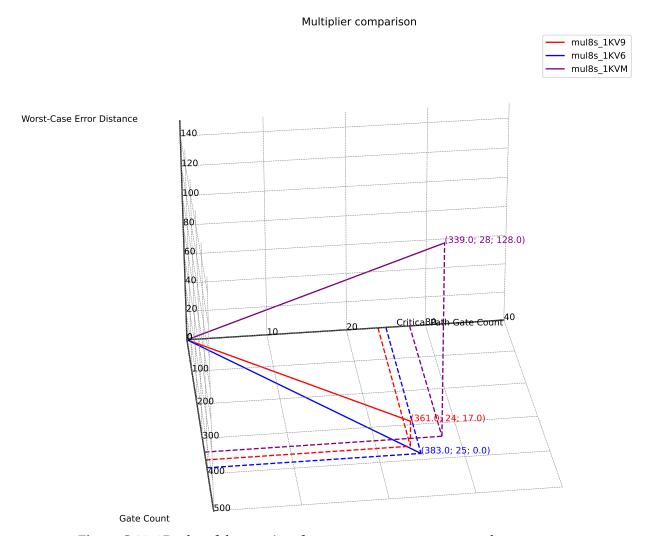

| 4.16       | 3D-plot of the metrics of mul8s_1KV9, mul8s_1KVM, and mul8s_1KV6                                  | 55  |

|            |                                                                                                   |     |

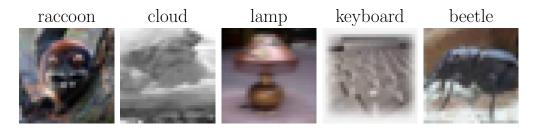

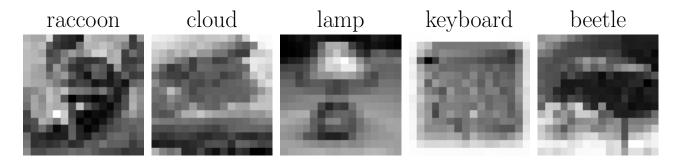

| 5.2        | 5 example images from CIFAR-100 represented as $32 \times 32$ colour images                       | 59  |

| 5.3        | 5 example images from CIFAR-100 represented as $32 \times 32$ grayscale images                    | 59  |

| 5.5        | 5 example images from CIFAR-100 represented as $16 \times 16$ grayscale images after being        |     |

|            | resized using LANCZOS3                                                                            | 60  |

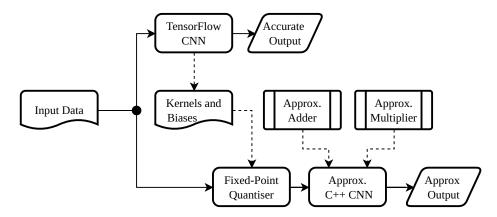

| 5.10       | Reference and Approximate CNN Relationship                                                        | 64  |

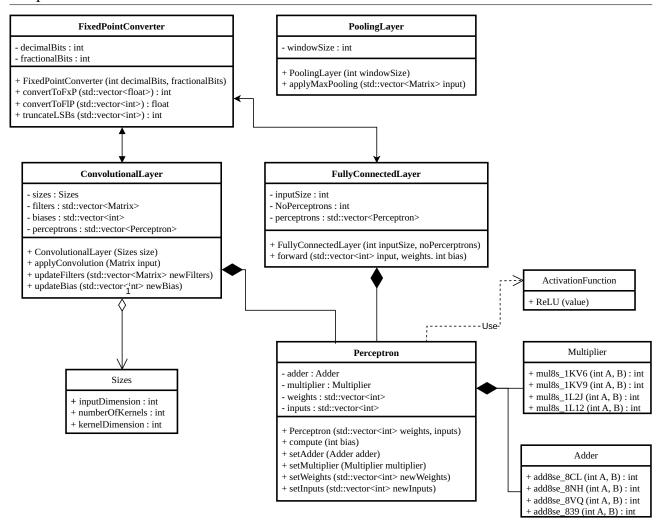

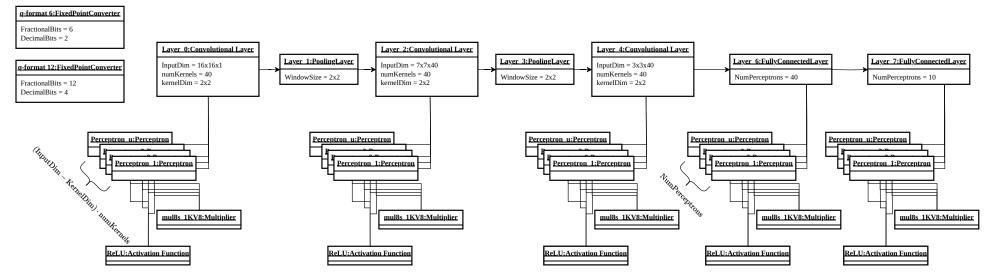

| 5.11       | Class diagram of the implementation of the reference CNN in C++                                   | 65  |

| 5.12       | Object diagram of the CNN model presented in Table 5.3                                            | 66  |

| 5.13       | Implementation of convolution in the <i>approximate model</i>                                     | 67  |

| 5.14       | Alternative convolution method                                                                    | 68  |

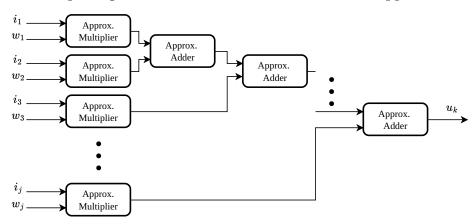

| 5.15       | Signal flow diagram of a perceptron with $j$ inputs and weights using approximate arith-          |     |

|            | metic circuits                                                                                    | 69  |

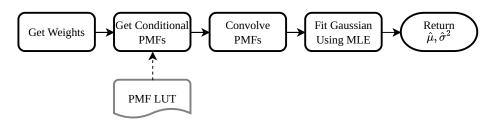

| 5.16       | Conceptual flow diagram illustrating the methods utilised for obtaining a probabilistic           |     |

|            | model for each perceptron in the CNN                                                              | 72  |

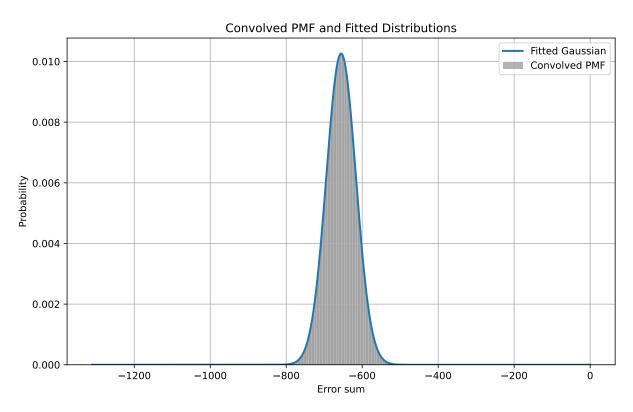

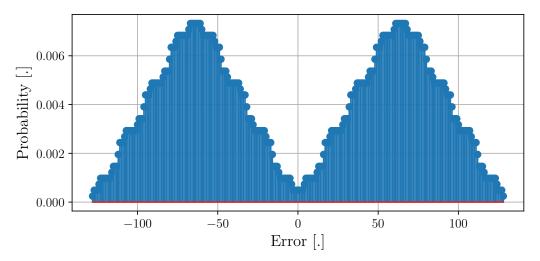

| 5.17       | The accumulated PMF plotted along the fitted Gaussian distribution                                | 73  |

|            | Convolution of a 3-dimensional input and two filters                                              | 74  |

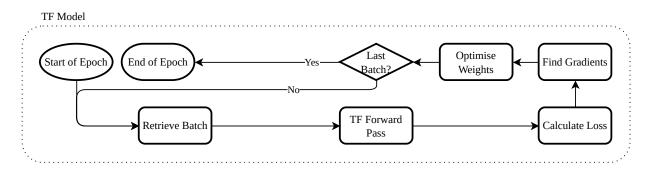

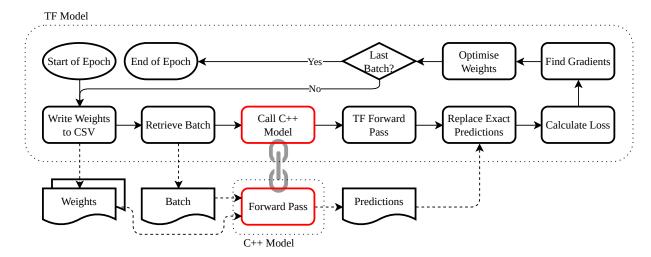

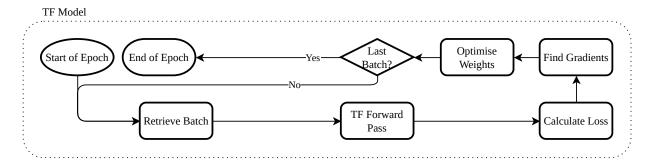

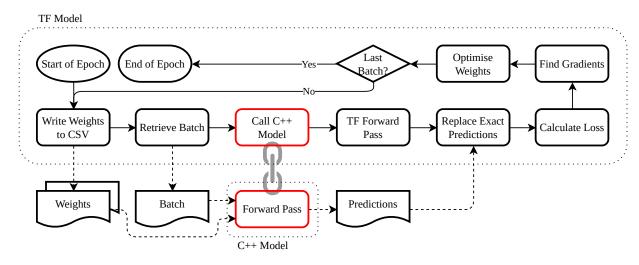

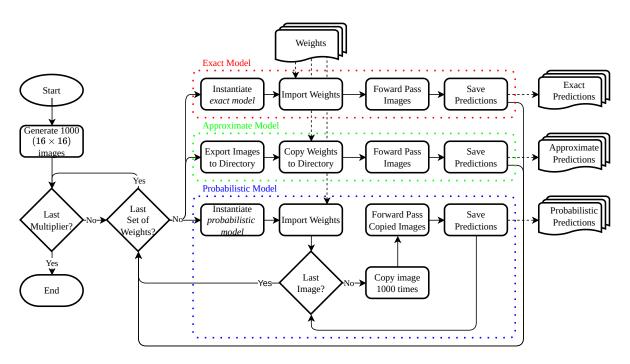

|            | Flowchart of an <i>approximate epoch</i> of training the model                                    | 77  |

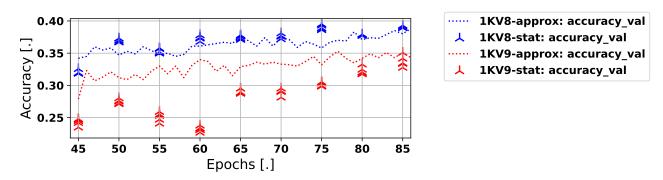

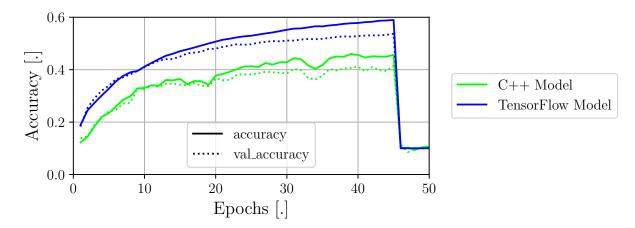

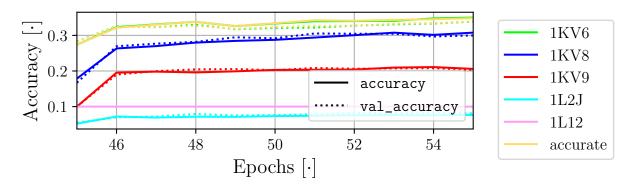

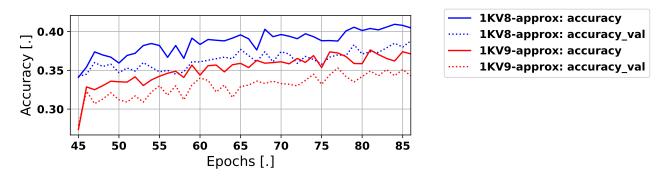

|            | Results of the accuracy evaluation on the <i>test</i> data set for the mul8s_1KV8 and mul8s_1KV9. | 83  |

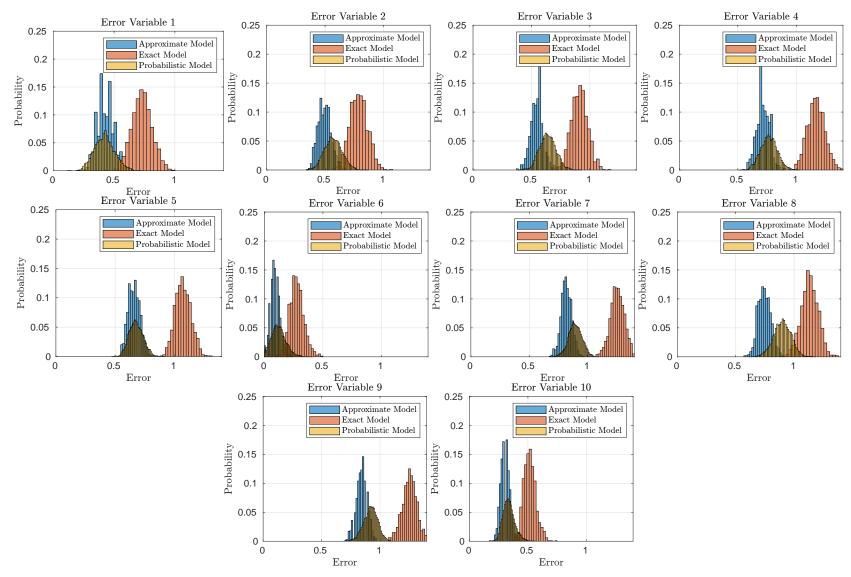

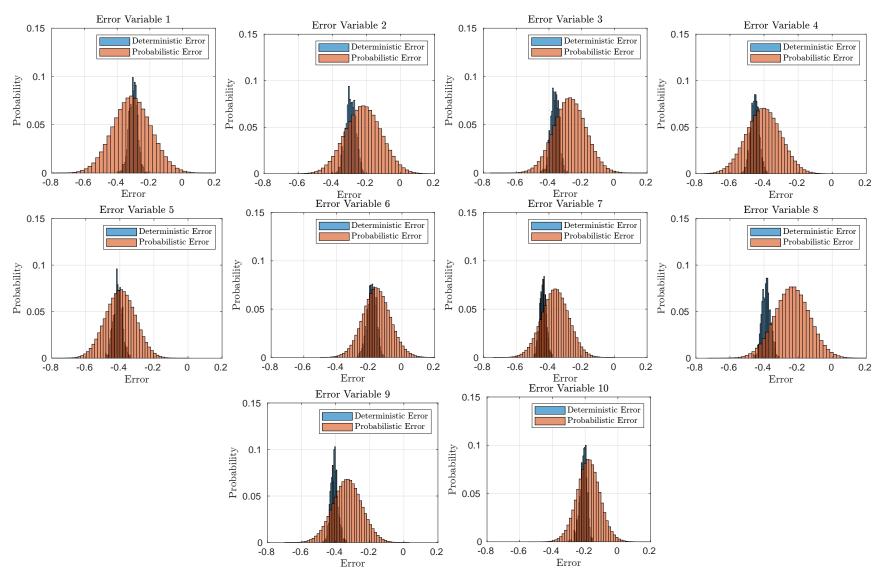

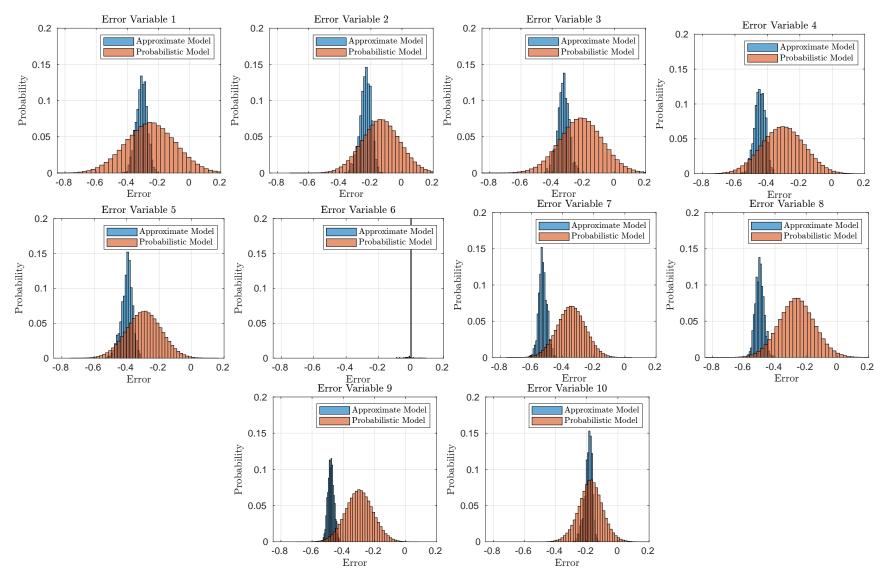

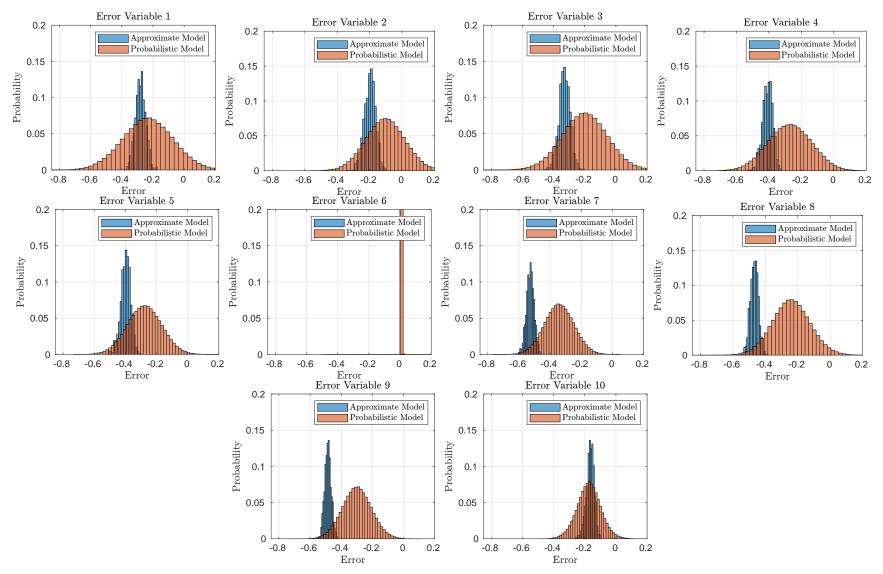

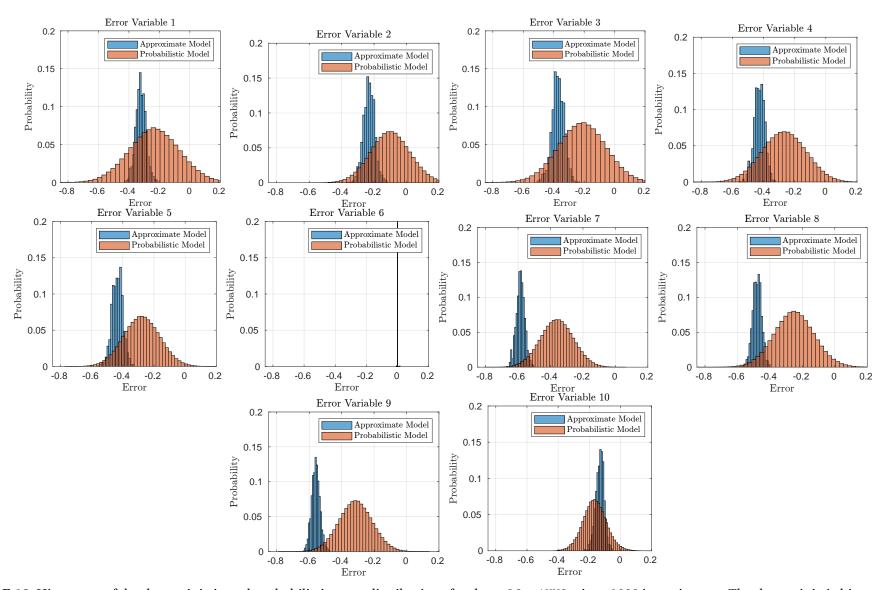

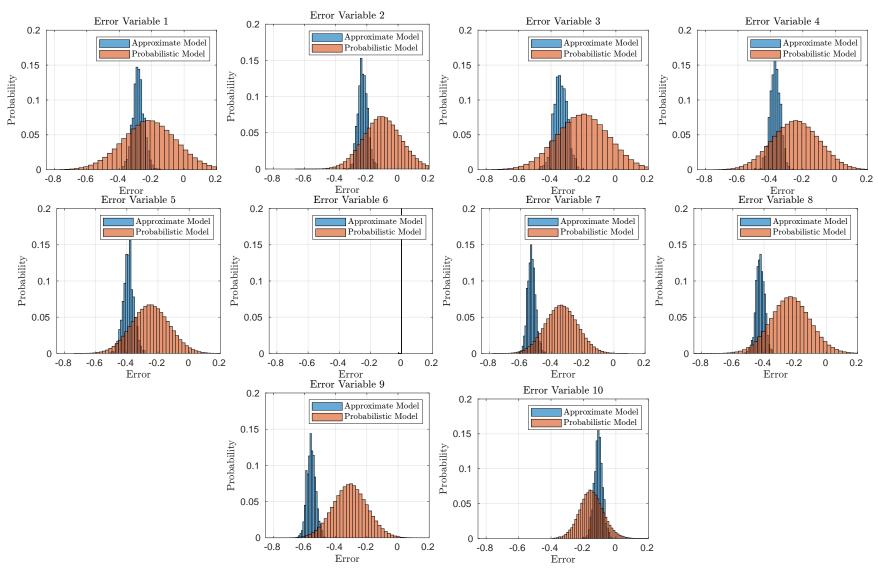

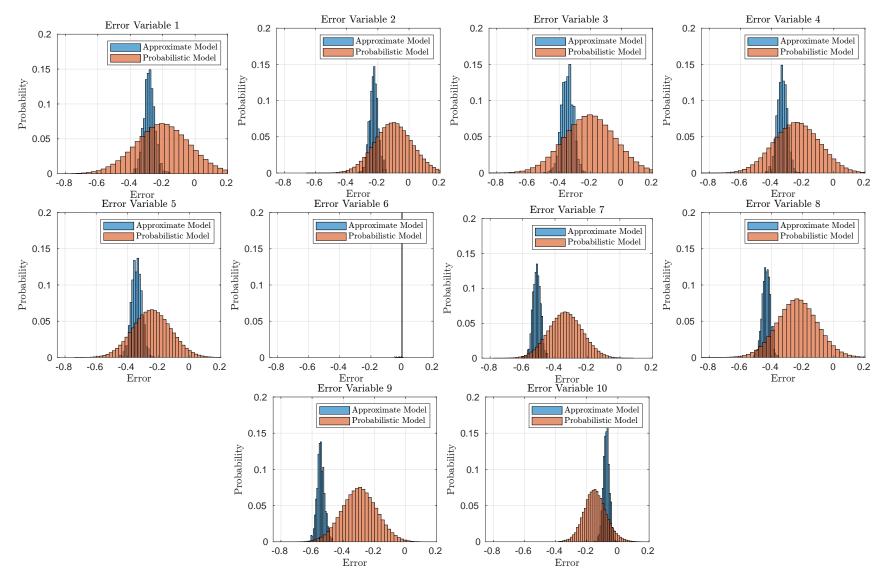

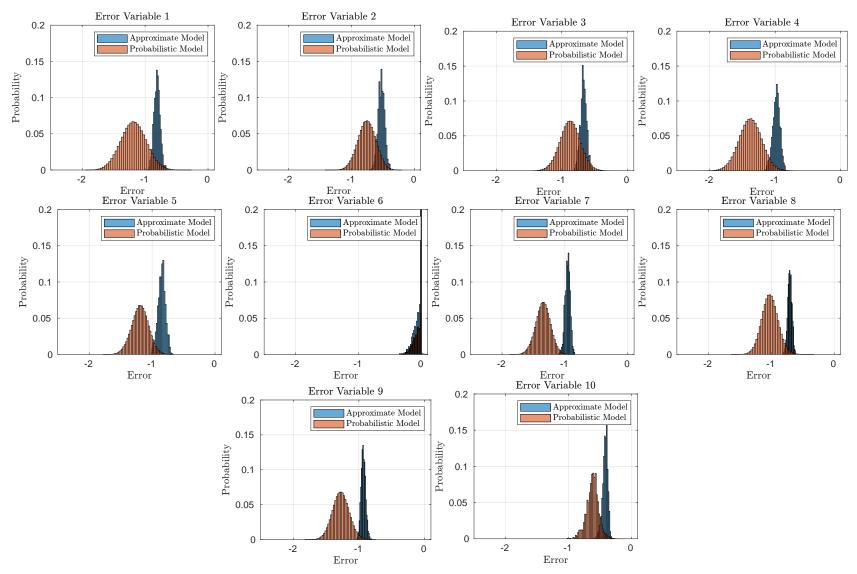

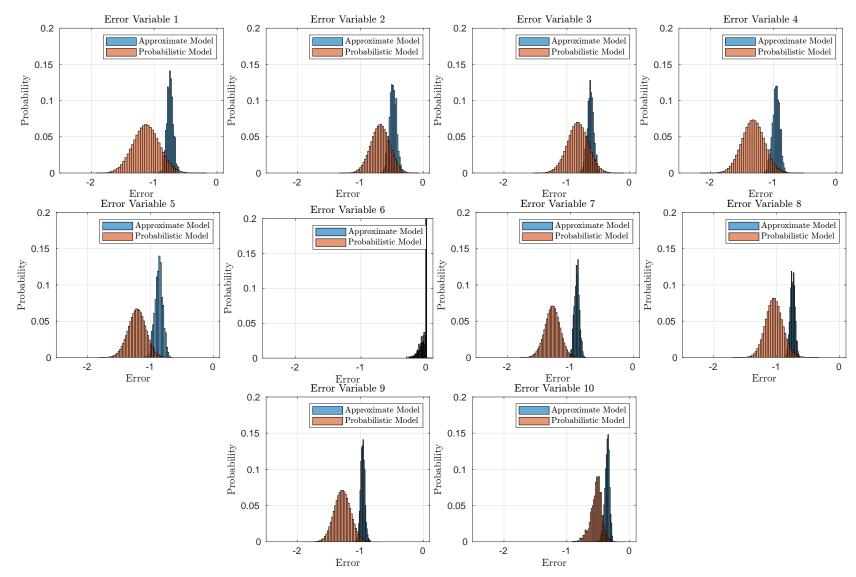

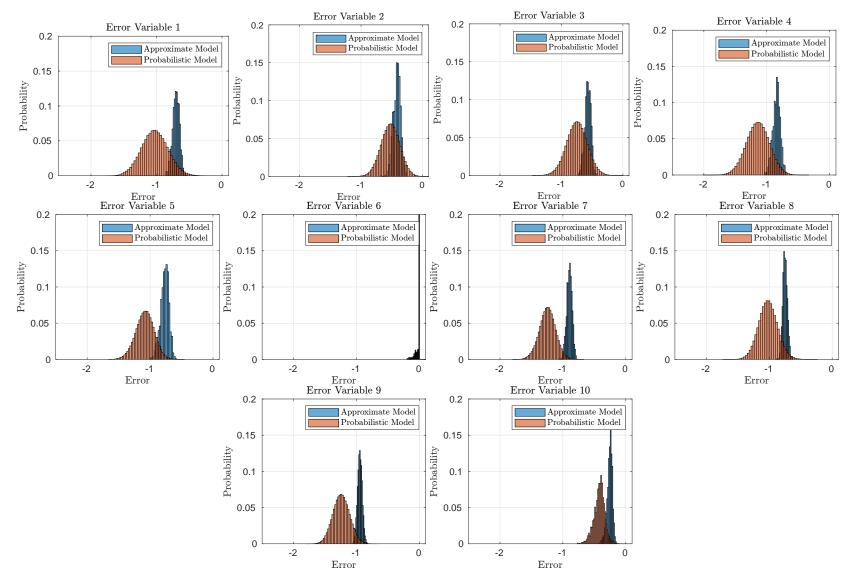

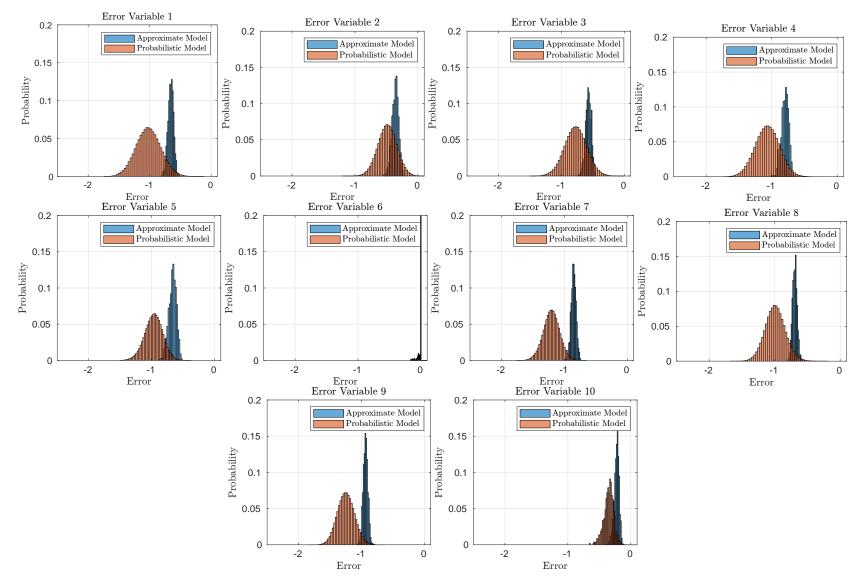

|            | Histogram of the deterministic and probabilistic error distributions, given 1000 input            |     |

|            | images                                                                                            | 85  |

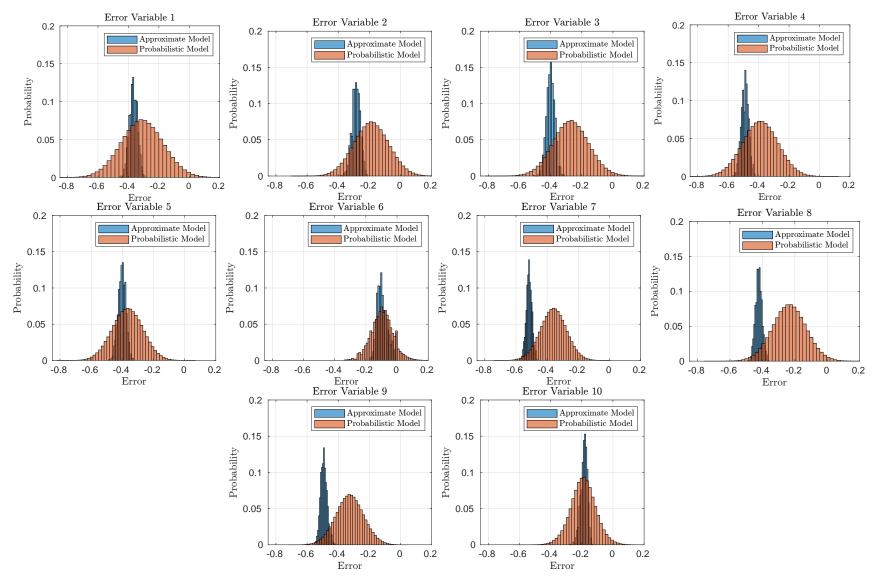

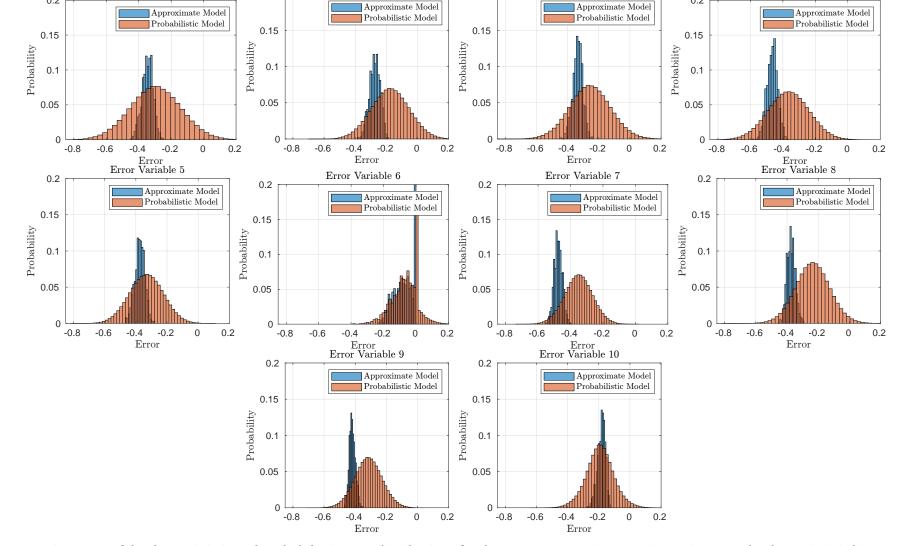

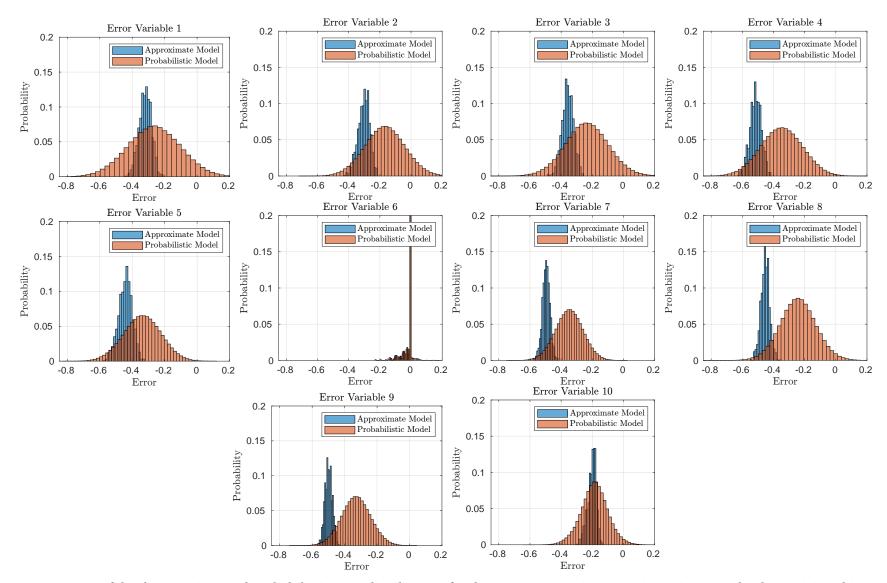

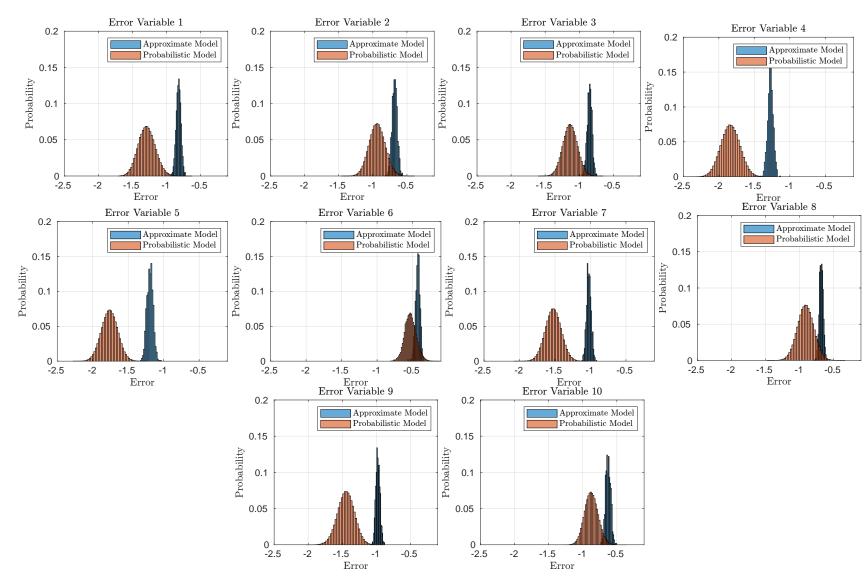

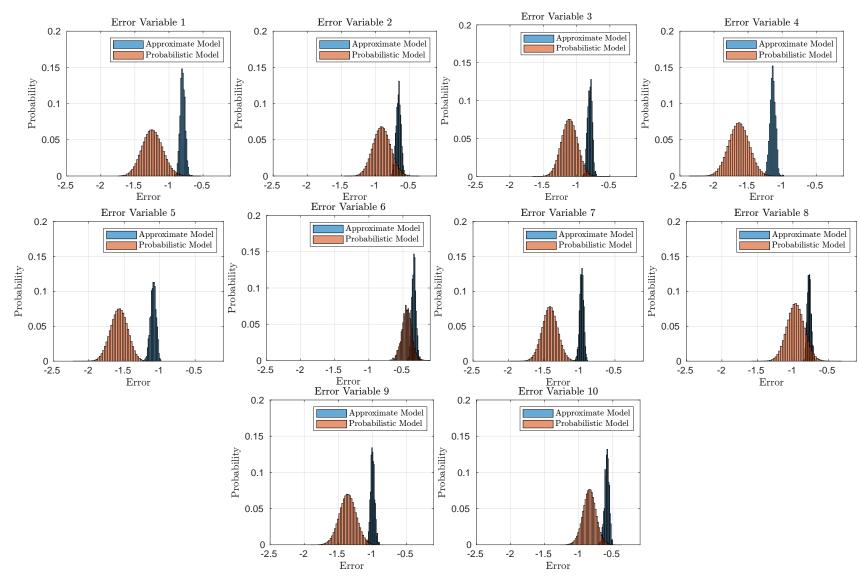

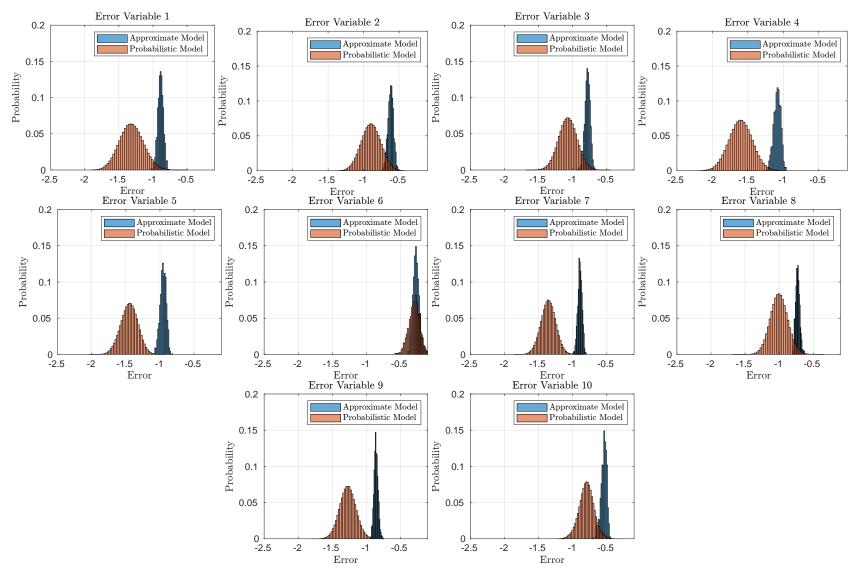

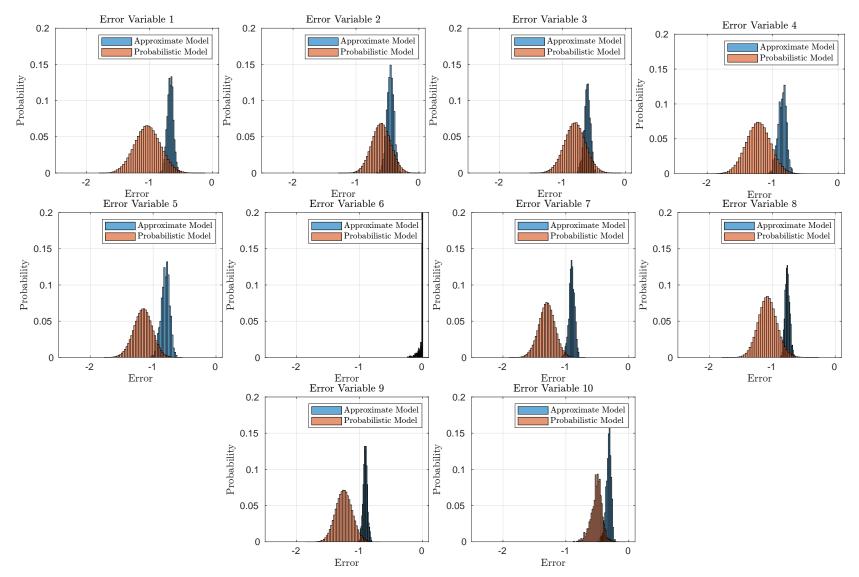

| 5.28       | Histogram of the deterministic and probabilistic error distributions for the mul8s_1KV9,          |     |

|            | given 1000 input images                                                                           | 86  |

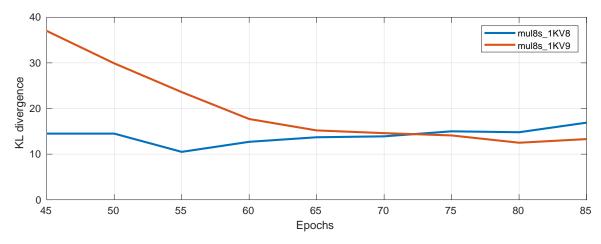

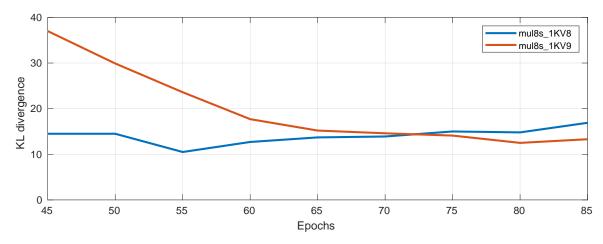

| 5.29       | Plot of the evolution of the KL-divergence, for progressing epochs                                | 87  |

|            |                                                                                                   |     |

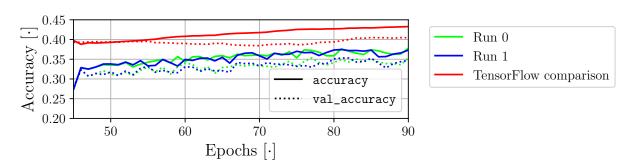

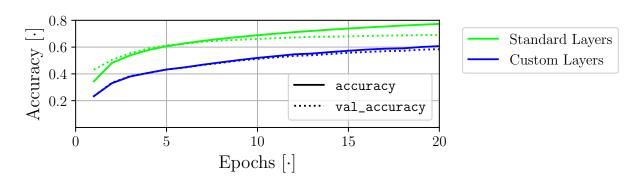

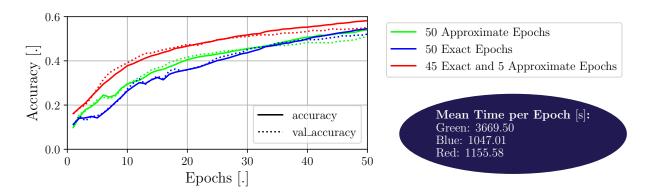

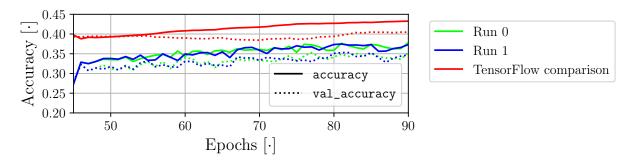

| 6.2        | Full-scale CIFAR-10 CNN trained with and without noise                                            | 92  |

| B.1        | 5 example images from CIFAR-100 represented as 32 × 32 colour images                              | 119 |

| B.2        |                                                                                                   | 119 |

| B.3        |                                                                                                   | 121 |

| B.5        | 5 example images from CIFAR-100 represented as 16 × 16 grayscale images                           | 122 |

|            |                                                                                                   | 122 |

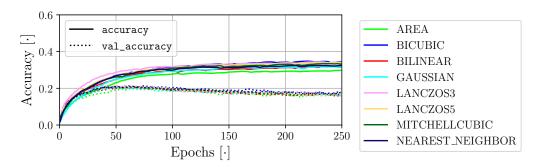

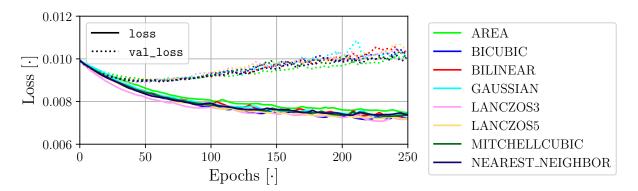

| B.4        | The accuracy as a function of epoch training the same model on differently resized                | 100 |

| D.C        |                                                                                                   | 122 |

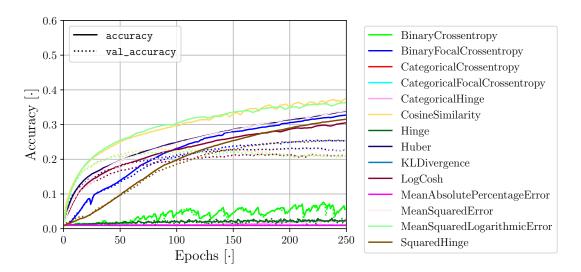

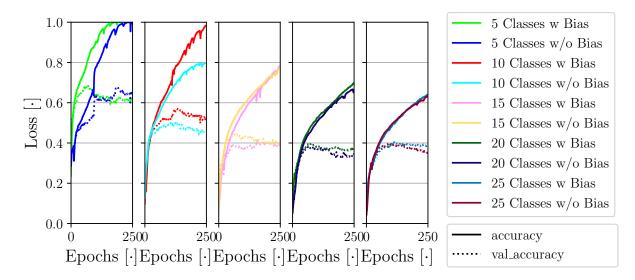

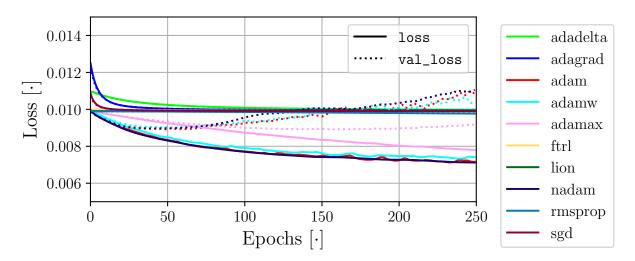

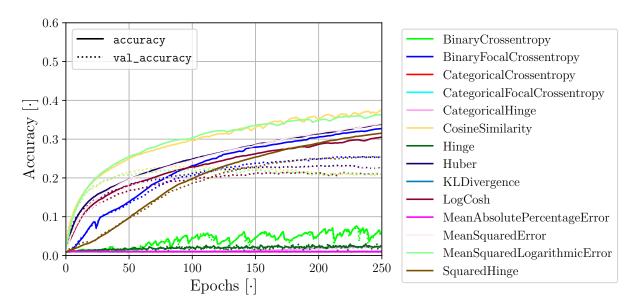

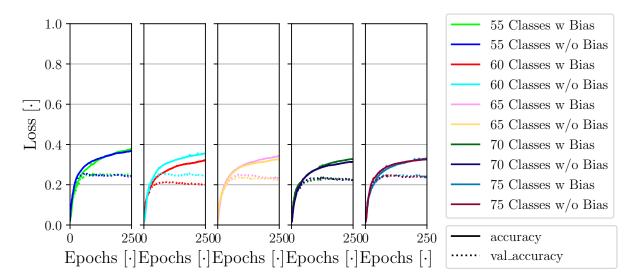

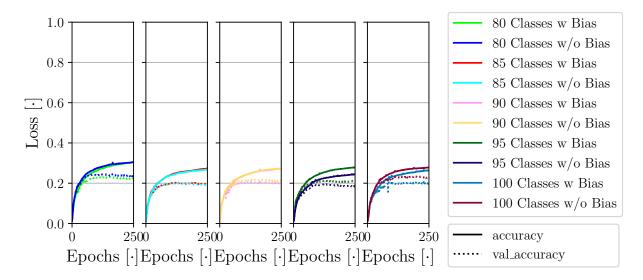

| B.6        | The loss as a function of epochs, training the same model on the same dataset using               | 104 |

| D 7        |                                                                                                   | 124 |

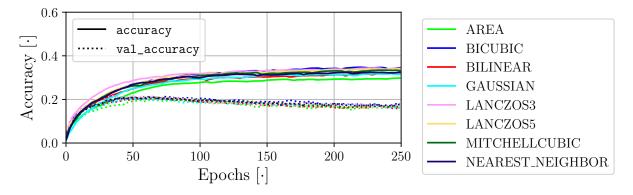

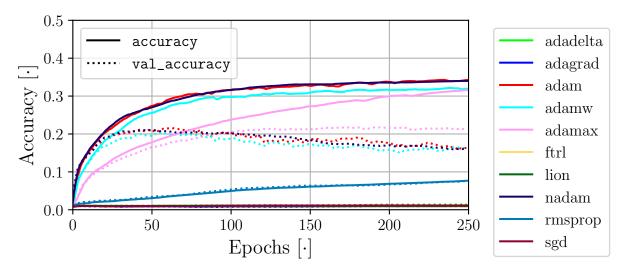

| B.7        | The accuracy as a function of epoch, training the same model on the same dataset using            | 104 |

| <b>D</b> 0 | 1 0                                                                                               | 124 |

| B.8        | The accuracy as a function of epochs, training the same model on the same dataset using           |     |

| <b>.</b> - |                                                                                                   | 125 |

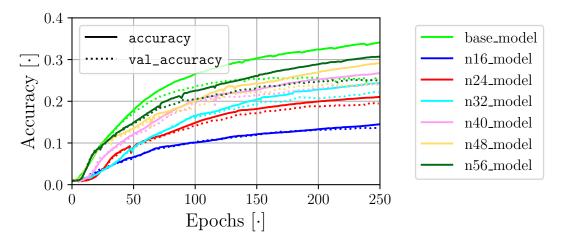

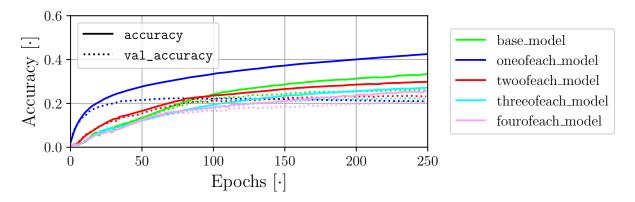

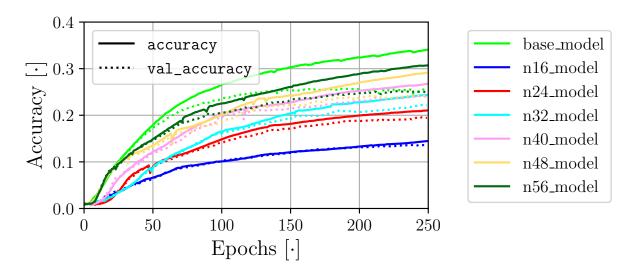

| B.9        | Accuracy as a function of epochs, training models of different depth on the same dataset.         | 128 |

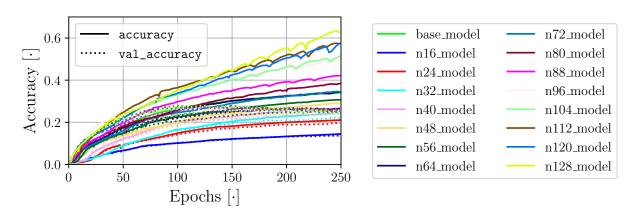

| B.10       | The accuracy as a function of epochs, training modified versions of the base model using          | _   |

|            |                                                                                                   | 128 |

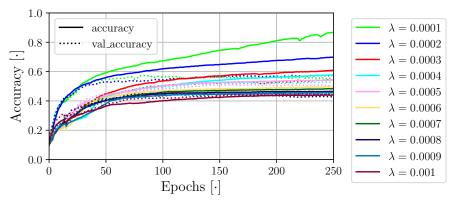

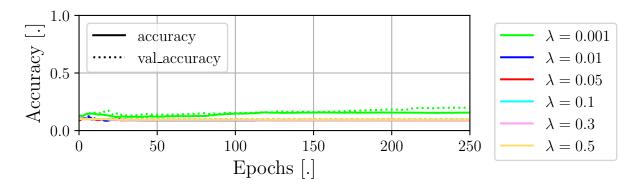

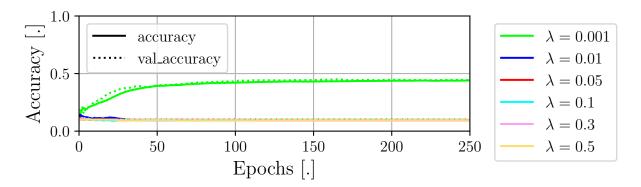

|            | 0                                                                                                 | 133 |

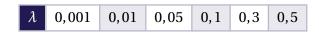

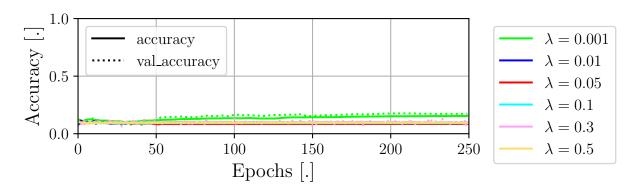

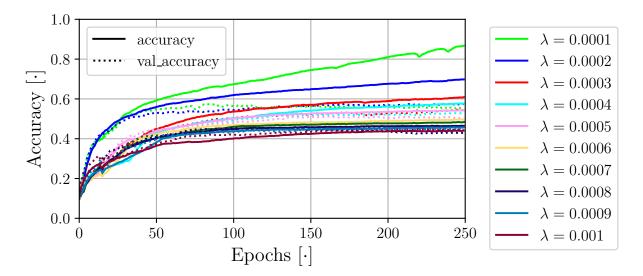

| B.17       | L2 regularisation with different $\lambda$ -values                                                | 133 |

Chapter 0 LIST OF FIGURES

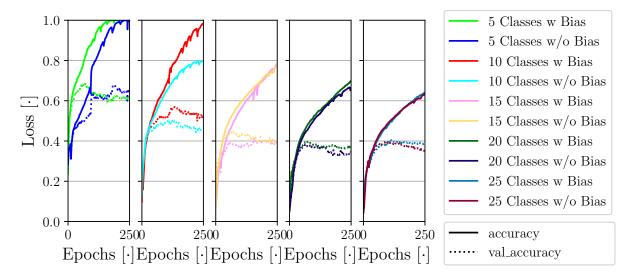

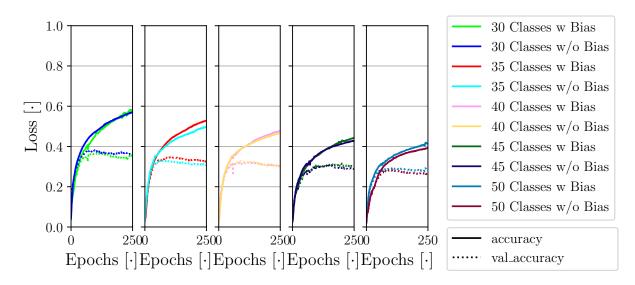

|      | 0                                                                                           | 133<br>134 |

|------|---------------------------------------------------------------------------------------------|------------|

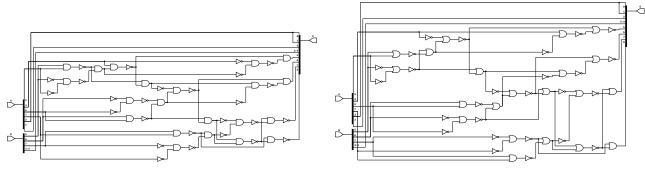

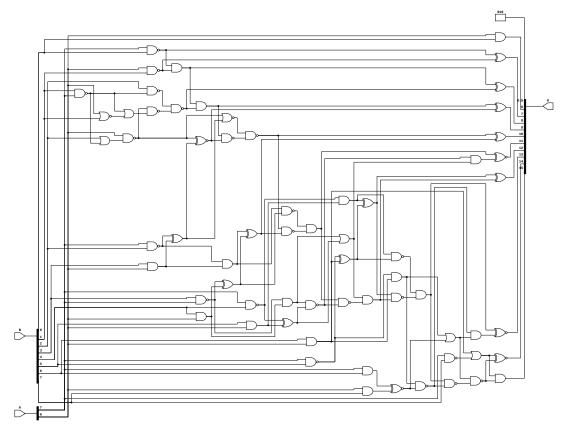

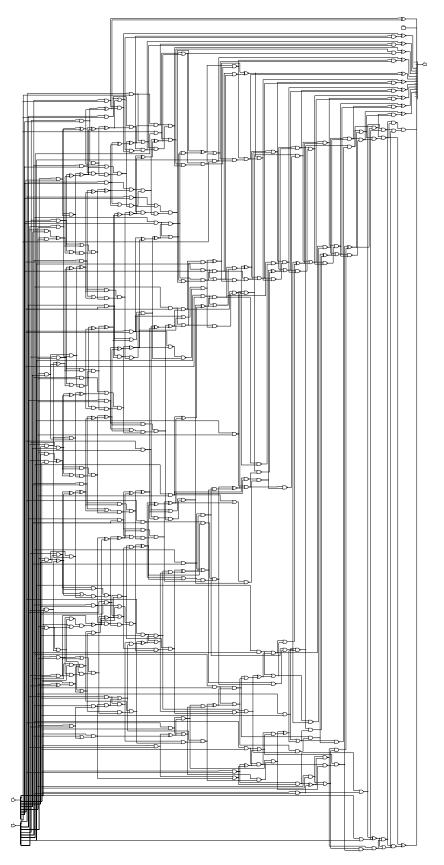

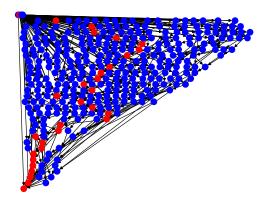

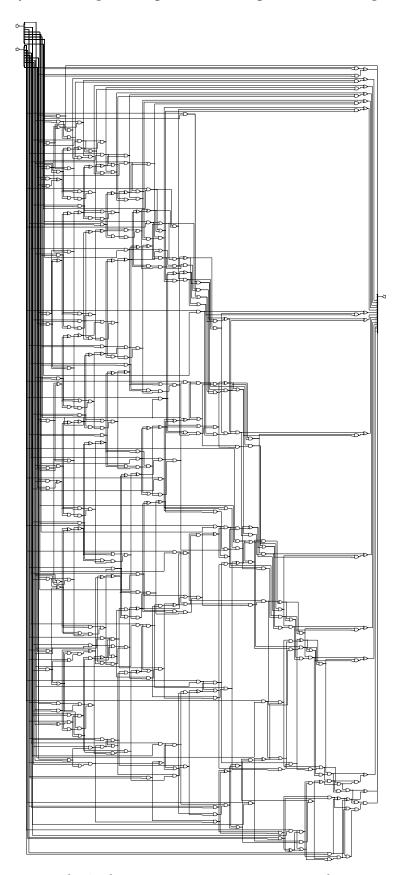

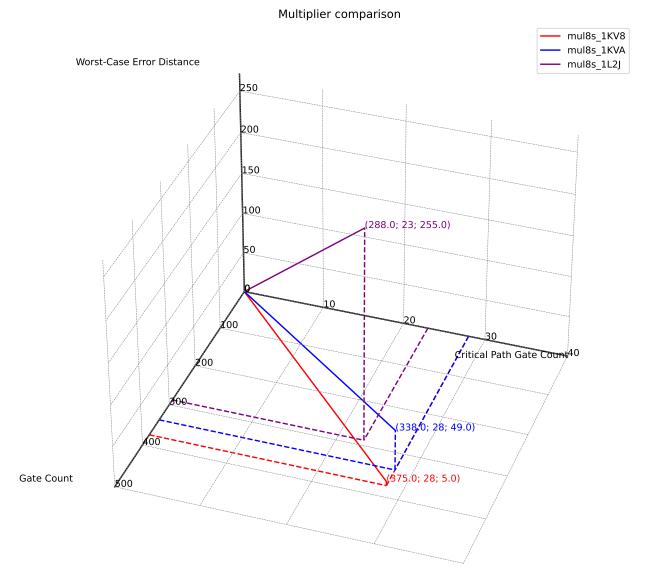

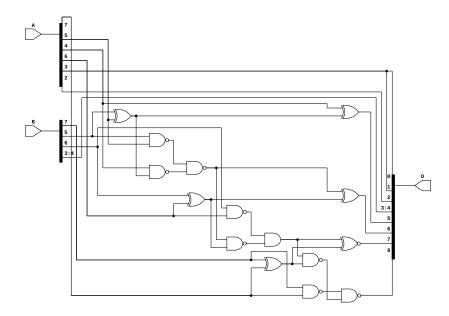

|      | mul8s_1L12 synthesised to AND, XOR, NAND, OR, NOR and XNOR gates using netlists v           | _          |

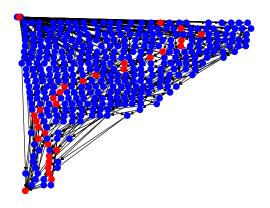

| C.2  | Visualisation of the DAG representation of Figure C.1                                       |            |

| C.3  |                                                                                             | 142        |

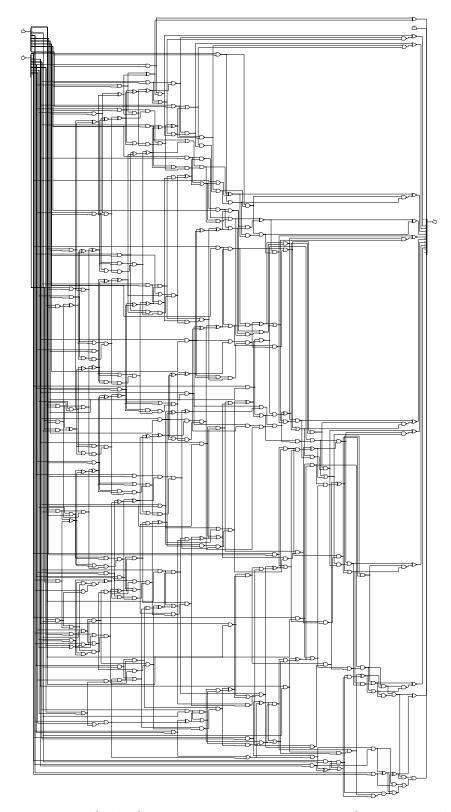

| C.4  | mul8s_1KV9 synthesised to AND, XOR, NAND, OR, NOR and XNOR gates using netlistsvg           | _          |

| C.5  | Visualisation of the DAG representation of Figure C.4                                       | 144        |

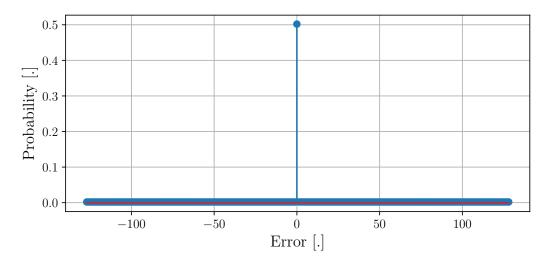

| C.6  | PMF of the error distribution of the approximate circuit in Figure C.4. The distribution is |            |

|      |                                                                                             | 144        |

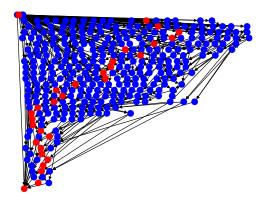

| C.7  | mul8s_1KV8 synthesised to AND, XOR, NAND, OR, NOR and XNOR gates using netlistsvg           | _          |

| C.8  |                                                                                             | 147        |

| C.9  | PMF of the error distribution of the approximate circuit in Figure C.7. The distribution is |            |

|      | plotted where each bar represents a discrete error distance                                 | 147        |

|      | mul8s_1KVM synthesised to AND, XOR, NAND, OR, NOR and XNOR gates using netlistsv            |            |

|      | 1 0                                                                                         | 150        |

| C.12 | PMF of the error distribution of the approximate circuit in Figure C.10. The distribution   |            |

|      | 1                                                                                           | 150        |

| C.13 | mul8s_1KVA synthesised to AND, XOR, NAND, OR, NOR and XNOR gates using netlistsv            | g.152      |

| C.14 | Visualisation of the DAG representation of Figure C.13                                      | 153        |

| C.15 | PMF of the error distribution of the approximate circuit in Figure C.13. The distribution   |            |

|      | is plotted where each bar represents a discrete error distance                              | 153        |

| C.16 | mul8s_1L2J synthesised to AND, XOR, NAND, OR, NOR and XNOR gates using netlistsv            | g.155      |

|      | Visualisation of the DAG representation of Figure C.16                                      | 156        |

| C.18 | PMF of the error distribution of the approximate circuit in Figure C.16. The distribution   |            |

|      | is plotted where each bar represents a discrete error distance                              | 156        |

| C.19 | mul8s_1KV6 synthesised to AND, XOR, NAND, OR, NOR and XNOR gates using netlistsv            | g.158      |

| C.20 | Visualisation of the DAG representation of Figure C.19                                      | 159        |

| C.21 | 3D-plot of the metrics of mul8s_1KV9, mul8s_1KVM, mul8s_1L12, and mul8s_1KV6                | 160        |

| C.22 | 3D-plot of the metrics of mul8s_1KV9, mul8s_1KVM, and mul8s_1KV6                            | 161        |

| C.23 | 3D-plot of the metrics of mul8s_1KV8, mul8s_1KVA and mul8s_1L2J                             | 162        |

| C.24 | 3D-plot of the metrics of mul8s_1KV8, mul8s_1KVA and mul8s_1L2J                             | 163        |

| C.25 | add8se_839 synthesised to AND, XOR, NAND, OR, NOR and XNOR gates using netlistsv            | g.164      |

| C.26 | Visualisation of the DAG representation of Figure C.25                                      | 164        |

| C.27 | PMF of the error distribution of the approximate circuit in Figure C.25. The distribution   |            |

|      | is plotted where each bar represents a discrete error distance                              | 165        |

| C.28 | add8se_8VQ synthesised to AND, XOR, NAND, OR, NOR and XNOR gates using netlistsv            | g.166      |

| C.29 | Visualisation of the DAG representation of Figure C.28                                      | 166        |

| C.30 | PMF of the error distribution of the approximate circuit in Figure C.28. The distribution   |            |

|      | is plotted where each bar represents a discrete error distance                              | 167        |

| C.31 | add8se_8NH synthesised to AND, XOR, NAND, OR, NOR and XNOR gates using netlistsv            | g.168      |

|      | Visualisation of the DAG representation of Figure C.31                                      | _          |

| C.33 | PMF of the error distribution of the approximate circuit in Figure C.31. The distribution   |            |

|      | is plotted where each bar represents a discrete error distance                              | 169        |

| C.34 | add8se_8CL synthesised to AND, XOR, NAND, OR, NOR and XNOR gates using netlistsv            | g.170      |

|      | •                                                                                           | 170        |

|      |                                                                                             | 171        |

|      | •                                                                                           | 172        |

| ъ.   |                                                                                             | 1          |

|      | Flowchart of an <i>exact epoch</i> of training the model                                    |            |

| D.2  | Flowchart of an <i>approximate epoch</i> of training the model                              | 174        |

Chapter 0 LIST OF FIGURES

| D.3  | Accuracy of C++ network with quantisation noise, 20 bits for precision                                                       | 176  |

|------|------------------------------------------------------------------------------------------------------------------------------|------|

| D.4  | Accuracy of C++ network with quantisation noise, 8 bits for precision                                                        | 177  |

| D.5  | Accuracy of C++ network with an approximate multiplier, mul8s_1KV9                                                           | 178  |

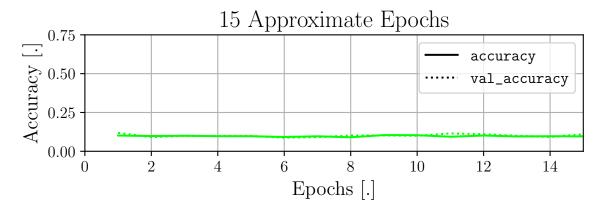

| D.6  | mul8s_1KV9 trained using approximate epochs                                                                                  | 179  |

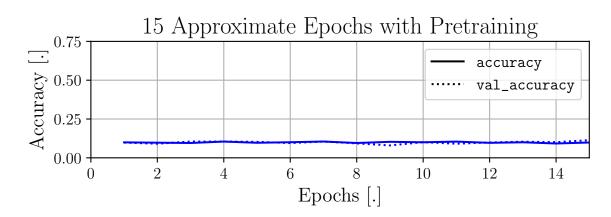

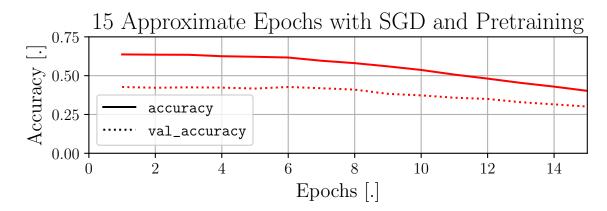

| D.7  | mul8s_1KV9 trained using approximate epochs on a pre-trained set of weights                                                  | 179  |

| D.8  | mul8s_1KV9 trained using approximate epochs on a pre-trained set of weights with                                             |      |

|      | SGD                                                                                                                          | 180  |

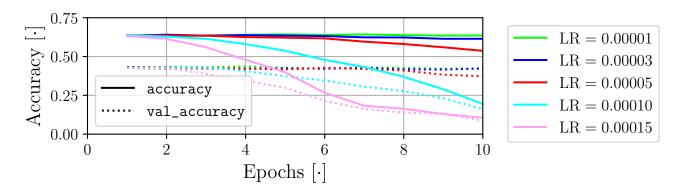

|      | Finetuning with different SGD learning rates                                                                                 | 180  |

|      | Preliminary test with only 2 filters in the second layer                                                                     | 181  |

| D.11 | SGD finetuning with 6 bits for precision                                                                                     | 182  |

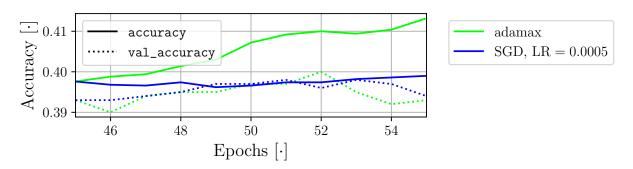

| D.12 | Adamax finetuning with 5 bits for precision on various multipliers                                                           | 183  |

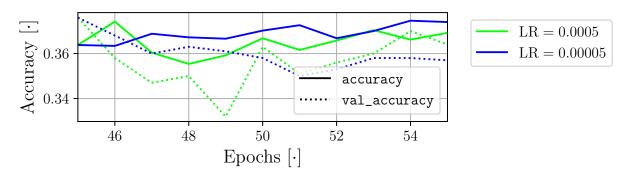

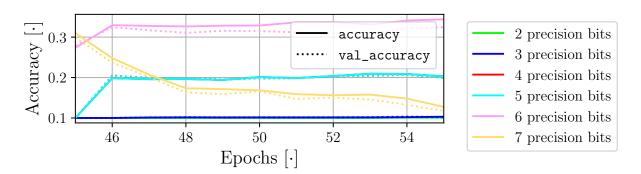

| D.13 | Adamax finetuning with varying number of precision bits on mul8s_1KV9                                                        | 183  |

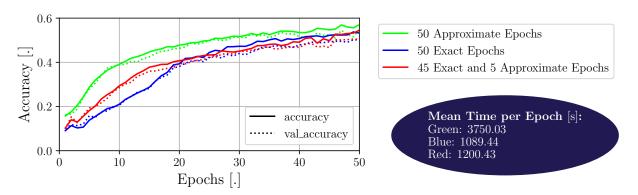

| D.14 | Finetuning with 45 <i>approximate epochs</i> with mul8s_1KV9 using 6 bits for precision                                      | 184  |

| E.2  | Testing the probabilistic model flow                                                                                         | 190  |

| E.3  | The train and test accuracy for the approximate model using both the mul8s_1KV8and                                           |      |

|      | mul8s_1KV9                                                                                                                   | 190  |

| E.4  | Results of the accuracy evaluation on the $\textit{test}$ data set for the $\texttt{mul8s\_1KV8}$ and $\texttt{mul8s\_1KV9}$ | .191 |

| E.24 | Plot of the evolution of the KL-divergence, for progressing epochs.                                                          | 219  |

# Introduction

AI (Artificial Intelligence) has become an inherent part of modern society. Everybody interacts daily with systems that, to some extent, rely on the benefits of AI, e.g. recommendation algorithms on entertainment platforms and social media, image recognition in automated vehicles, and speech recognition in virtual assistants [5]. The concept of AI is present in the consciousness of non-experts, partially due to the portrayal in popular culture within the last century. The often antagonistic role of self-conscious AI-systems in science fiction has resulted in an extensive discussion within the public domain, about ethics and ramifications of AI. However, AI or more specifically ML (Machine Learning) algorithms have often proven very beneficial in data analysis, for clustering, classification, and segmentation of data sets [6][7]. AI and ML have seamlessly integrated into modern everyday life, despite the immense ethical implications of "granting" machines an extent of human intelligence. The cause is that the current confines of ML are manifested in more application-specific implementations, which have consistently proven a societal value.

ML is a general term for statistical algorithms that can make inferences about the distribution of datasets and is generally divided into three domains namely reinforcement- unsupervised-, supervised-learning [6][7][8]. Common for all approaches is the **learning** attribute, which is a description of the model's ability to adapt to an environment and thereby *learn* over time. Russell and Norvig [9] introduced the concept of **intelligent agents** as systems that *perceive* its environment and induce hypotheses about the external circumstances. By falsifying the hypotheses the intelligent agents can induce new hypotheses by exploiting previous metrics. This iteration scheme is known as **training** [8][9][10]. The three approaches differ in the manner in which they learn and train.

The *reinforcement learning* paradigm is based on the principle of carrot and stick, meaning a decision-making agent is performing a sequence of actions, where desired actions are rewarded and less attractive alternatives are punished [6][9][10]. Through trial and error, the model should iteratively approach the optimal program for the task, thereby maximising the accumulated reward [11].

The *unsupervised learning* paradigm is based on the principle of learning without confirmation of achievement; a common saying is that the models "learn without a teacher" [9][10]. Essentially the goal is to find patterns and regularities in unlabelled data, to make inferences about underlying distributions. One approach to unsupervised learning is known as **clustering**, which builds on the principle of density estimation in statistics [9][11][12]. The aim is to cluster or group the data based solely on dispersing the features within the set. The clustering can be performed without any assumptions of underlying distribution (i.e. non-parametric) or oppositely with *a priori* knowledge of the underlying distribution (i.e. parametric), which guides the clustering process based on assumptions about the data's distributional form. Procedures such as anomaly detection or feature space reduction can also be approached as unsupervised learning [10].

The *supervised learning* paradigm seeks a mapping from input to output variables. In other words, the aim is to find a function that matches given input features to an output label [10][13]. In simple terms, a supervised learning algorithm has two separate phases. First, a training phase where a set of annotated data is used to derive the aforementioned input/output mapping. Last, is an inference phase where the mapping is used to make predictions about unlabelled data [8][13]. Supervised learning applications can generally be divided into two branches; **classification** and **regression**. Classification tasks are to determine the label or class of an input feature, where some examples are e-mail spam detection or image classification. Regression differs from classification in that the inferences made in regression are concerned with predicting continuous outcomes, such as a numerical value or a range. In contrast, classification focuses on predicting discrete class labels or categories.

A multitude of statistical algorithms and models have been developed within the three approaches, however, ANN (Artificial Neural Networks) or simply NN (Neural Networks) have been at the pinnacle of machine learning algorithms for the past decades since the introduction of layerwise deep network training in 2006 [14], which allows for the development of advanced high-performance models [11][15][16]. NNs are inspired by the processing abilities of the human nervous system and are both more versatile and complex than traditional statistical approaches [7][9][17]. Traditional algorithms rely on a sparse amount of intelligent agents to induce hypotheses about the data, why the algorithms usually are application specific [7]. The versatility of NNs comes from the scalability of intelligent agents used in the network. The NNs can scale to model large datasets with complex input/output relationships, and a great amount of features in the dataset [18].

The current frontiers within almost every field in science and technology rely on gathering and generating large quantities of data. The paradigm of **big data**-analysis is a recurrent issue for researchers and developers in the entire academic landscape; from healthcare and finance to biology and robotics [16][18]. The growing demand for data analysis has endowed research in computer engineering and statistics with a powerful tool, resulting in a variety of network architectures.

Associated with the progress of data analysis and machine learning is *the price to pay*. Financially and environmentally the burden of the seemingly ever-increasing size of the data models bears a toll; renting/purchasing the necessary hardware, electricity, compute time, and the environmental ramifications of producing the hardware and electricity [19]. Research from OpenAI uncovered a doubling of compute used to train new state-of-the-art models of around 3,4 months between 2012 and 2018 [20]. In a paper from 2019 regarding *energy and policy considerations for deep learning* it is estimated that training a big *transformer* with neural architecture search produces around five times the amount of CO<sub>2</sub> emissions than the lifetime of a car inclusive fuel.

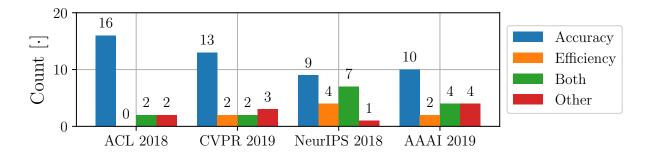

Research and development of these data models are skewed toward increasing the accuracy of the final product rather than developing efficient implementations (see Figure 1.1). The outcome of the research is not to be understated, however, a balance must be found to ensure the sustainability of deep learning. Meeting these demands with traditional computing approaches that prioritise accuracy at all costs becomes increasingly challenging due to the infeasibility of Moore's Law and the breakdown of Dennard scaling [21]. Increasing computational load is therefore unsustainable in terms of energy consumption, processing time, and resource utilisation [22][23].

**Figure 1.1:** Distribution of foci from papers. A sample size of ~ 80 papers from four conferences is divided into four categories based on the main contribution claimed by the authors. Data w.r.t ACL, CVPR, and NeurIPS taken from [24] and w.r.t AAAI from [25].

The field of AC (Approximate Computing) has gained immense interest in recent years as an approach to comprehending the vast expansion of energy consumption and inference latency. The approach of AC is to reassess arithmetic problems in applications where the introduction/increase of error can be traded off for a disproportionate reduction in energy, resource, or time consumption. This, of course, excludes tasks that require the highest precision, e.g. tasks like diagnosing patients and control systems with human lives on the line. However, fault-tolerant applications like image-and speech-processing, data analysis, sensor data processing, and ML models could potentially benefit from utilising AC techniques. Based on the findings of *Understanding and mitigating noise in trained deep neural networks* by Semenova, Larger, and Brunner NNs are effective at avoiding the accumulation of noise and that the *signal-to-noise ratio* does not worsen when adding more layers [26], which indicates that introducing some error might not affect the accuracy of the models too much.

One of the techniques from *approximate computing* addresses arithmetic operations, whereby a decrease in area and/or latency can be exchanged for a drop in the accuracy of the operations. Methods exist wherewith circuits for addition and multiplication can be modified to automate this tradeoff, like CGP (Cartesian Genetic Programming) . However, the *ad hoc* approach is still relevant; say you have a multiplier design that is slightly too big for the implementation and you have to remove a couple of gates. It is difficult to know how the *removal* of gates will affect the circuit, i.e. how much *error* will be introduced. Furthermore, how will the "small" change affect the higher functionalities of a system? The ad hoc approach to developing an approximate ASIC (application-specific integrated circuit), leaves developers with an unsystematic and ungovernable catalogue of options.

Leon et. al. [27] propose future points of investigation in the field of AC, where broad benchmarks are a critical point in making energy-efficient approximate systems a permanent staple in the development of *on the edge devices*. A foundation for fair comparison of AC approaches is desired for developers to determine the appropriate approximate arithmetic units for a given CNN. The "fair comparison" lies in developing general statistical evaluation methods that are inferable with the outcome of the CNN at hand. The statistical evaluation should ideally produce metrics related to the application's performance.

It is desired to present a reproducible methodology for comparing a subset of approximation techniques applied to the netlist design of the hardware of a *CNN preliminary*: A *benchmarking tool* for AC techniques in the CNN application capable of using any AC design. This solution differs from the efforts in generalising approximate designs and rather embracing the ad hoc engineering approach previously described. Such a benchmarking tool would provide developers with an option to evaluate approximate circuit designs before implementation.

Frameworks for simulation of approximate computing techniques applied to CNNs already exist like: TypeCNN, AxDNN, and ProxSim [28][29][30]. However, these frameworks are aimed at the development of the CNNs and the demographic is the *machine learning developer* rather than the *circuit developer*. Furthermore, these three proposals are limited in the sense that the scalability and generalisation of the CNN models are of minor consideration. These methods contribute greatly to the methodology of designing cross-layer end-to-end simulations prior to hardware implementation but lack the *interpretation* of the actual outcome of a CNN model. In other words, how are the approximations affecting the perceptual and recognisable features of the CNN?

The purpose of this project is to achieve a method of **scaling** and **generalising** the cross-layer end-to-end approximate CNN simulations, to accommodate and interpret the raison d'être of CNN models prior to hardware implementation of the approximate circuits. This benchmarking system is summed up in the following problem statement:

"How can a benchmarking tool provide an ASIC developer with relevant metrics to evaluate an *approximate* arithmetic circuit as an integral part of a large scale system, i.e. a *neural network*, prior to implementation?"

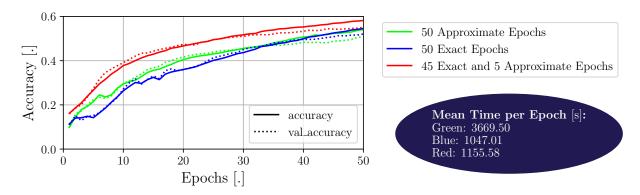

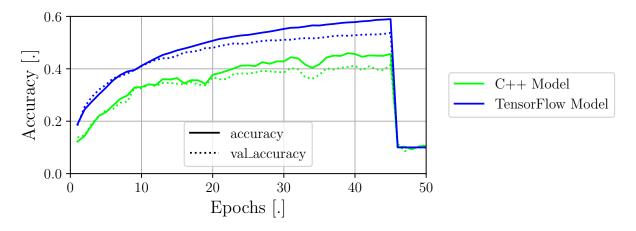

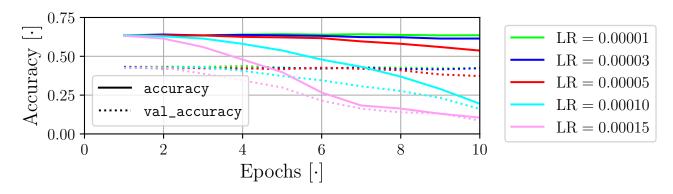

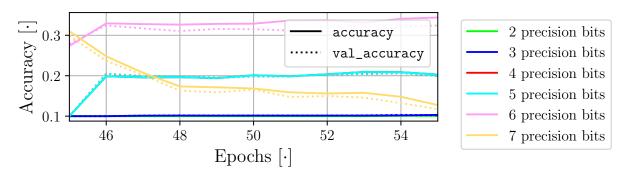

# Survey 2