# Synchronization Stability of Inverter Based Resources during Faults on Low Voltage Grids

Kaustubh Bhatnagar

Energy Technology, PED4-1042, 2022-01

Master's Project Semester

Synchronization Stability of Inverter Based Resources during Faults on Low Voltage Grids

> Kaustubh Bhatnagar Energy Technology, PED4-942, 2022-01

> > Master's Project

Copyright © Aalborg University 2022

5

Energy Technology Aalborg University http://www.aau.dk

## AALBORG UNIVERSITY

STUDENT REPORT

## Title:

Synchronization Stability of Inverter Based Resources during Faults on Low Voltage Grids

**Theme:** Scientific Theme

**Project Period:** Fall Semester 2022

**Project Group:** PED4-1042

**Participant(s):** Kaustubh Bhatnagar

**Supervisor(s):** Florin Iov Subham Sahoo

Page Numbers: 74

**Date of Completion:** May 30, 2022

## Abstract:

The transition from conventional power system to power electronics dominated power system. Concern regarding the availability and stability of the future power system is emerged. The system will be more prone to short-circuit faults as it will highly dominated by inverter based resources. To address this issue, fault ride through capability is required to avoid voltage and frequency instability. However, loss of synchronization is observed during severe symmetrical faults and second harmonic oscillations for asymmetrical faults. In order to avert the loss of synchronization current injection angle with respect to line impedance characteristics is carried out in this project. To that end, modified positive and negative sequence injection method is proposed to attenuate second harmonic oscillations and avoid over voltage in non faulty phase during asymmetrical faults.

The content of this report is freely available, but publication (with reference) may only be pursued due to agreement with the author.

<sup>10</sup> By accepting the request from the fellow student who uploads the study group's project report in Digital Exam System, you confirm that all group members have participated in the project work, and thereby all members are collectively liable for the contents of the report. Furthermore, all group members confirm that the report does not include plagiarism.

# Summary

- The increasing energy consumption globally an increased electrical production to 15 meet these requirements. In past decades, due to foreseen exhaustion of fossil based energies has brought worldwide attention towards sustainable energy production. The desire to reduce the carbon footprint has made us more inclined towards penetration of renewable energy resources like wind turbine, photovoltaic

- and energy storage systems into the power-system. The transition from the conven-20 tional power-system to power electronics dominated power-system has imposed many challenging issues to the distribution power grid and utility. The generation from renewable energy resources is always time-varying and fluctuating, especially with a high penetration of renewables under the mixed energy infrastructure. This

- will affect the network stability and more prone to disturbances. The transmission 25 system operators have issued stringent interconnection codes for the grid integration of renewable energy resources. Therefore, concerns regarding the resiliency and stability of the system have been raised especially being vulnerable to extreme weather conditions. In the world around 50% of the network is composed

- of low-voltage system. Thus making low-voltage network more prone to short cir-30 cuit faults due severe weather/climate conditions. The stability of the system due to such conditions has raised questions in the past. However, the stability of the system due to severe short-circuit faults is a growing concern with increasing integration of renewable energy resources. The grid-requirement needs to be fulfilled

- to avoid voltage instability of the system. On the other hand, due to severe faults 35 both voltage and frequency instability occurs leading to unintended disconnection of system from the network. The unintended disconnection of system from the network due to short-circuit faults has lead to concern over synchronization stability under such conditions. The objective is to provide voltage support without losing synchronizm from the network. 40

- During short-circuit faults as per grid-code requirements reactive current injection is required to provide voltage support. However, due to severe symmetrical faults the loss of synchronizm is most likely to occur as it is highly dependent on line impedance characteristics. Accurate current-transfer limits needs to be de-

rived depending upon line impedance characteristics and current injection angle. 45

50

55

On the other hand, the asymmetrical faults leads to the generation of second harmonic oscillations. The conventional method cannot avoid loss of synchronizm or attenuate second harmonic oscillations. However, conventional method during asymmetrical faults also introduces over voltage to non-faulty phase. In order to solve this problem modified flexible positive and negative sequence injection is proposed by considering dc link dynamics to provide flexible current sequence injection. This method attenuates second harmonic oscillations and avoids over voltage to non-faulty phase. The proposed method consider DC link dynamics, avoid use of complex phase locked loops for sequence extraction and less computational burden making it suitable for low-voltage grid integrated system. Time domain analysis is carried out considering different scenarios. The derived controllers are implemented in hardware-in-the-loop to provide a real-time implementation of the considered scenarios. This project considers the worst case scenario possible, where the conventional method fails and aims to provide a feasible solution.

# **Preface**

The following project is the work carried in 4<sup>th</sup> semester on the masters program of Power Electronics and Drives at the Department of Energy, Aalborg Universitet. This project aims to study the synchronisation stability of inverter based resources in low voltage grids during faults. The theme of the project is to avoid using

<sup>65</sup> complex controllers or methodologies. Complex controllers introduce additional delay into the system and not feasible for low-voltage grid integrated system. The solution required for such systems should be less complex, cheap and low computational burden. However mathematical algorithms can be utilised as they won't introduce additional delay and easy to implement. The control strategies imple-70 mented in this project will be only dedicated for low-voltage grid integrated sys-

70

tem. The prerequisites for reading this project is basic understanding of classical control theory and integration of grid side converter to the grid. Apart from that, efforts have been made to familiarize the reader with the structure. To further

<sup>75</sup> clarify conclusion are provided at the end of every chapter.

This project is highly dependent on different software package applications. MATLAB has been used extensively for numerical calculations, coding and plotting figures. PLECS was used for discrete implementation of controllers and for off-line studies. MATLAB SISO tool was utilised for tuning of all the controller parameters with classical tuning methods during this project. The appendices are attache at the

with classical tuning methods during this end of report describing basic theory.

Aalborg University, May 30, 2022

Kaustubh Bhatnagar <kbhatn20@student.aau.dk>

# Contents

| 85  | Su | ımma        | ary                                                                   |    |  |  |  |

|-----|----|-------------|-----------------------------------------------------------------------|----|--|--|--|

|     | Pr | Preface vii |                                                                       |    |  |  |  |

|     | 1  | Intro       | oduction                                                              | 1  |  |  |  |

|     |    | 1.1         | Background and Motivation                                             | 1  |  |  |  |

|     |    | 1.2         | Power System Faults and Instability Phenomena                         | 5  |  |  |  |

| 90  |    | 1.3         | Grid Requirements                                                     | 8  |  |  |  |

|     |    | 1.4         | State of the Art                                                      | 10 |  |  |  |

|     |    | 1.5         | Problem Formulation                                                   | 13 |  |  |  |

|     |    | 1.6         | Project Objectives                                                    | 14 |  |  |  |

|     |    | 1.7         | Methodology                                                           | 15 |  |  |  |

| 95  |    | 1.8         | Scope and Limitations                                                 | 16 |  |  |  |

|     |    | 1.9         | Content of Report                                                     | 16 |  |  |  |

|     | 2  | Syst        | tem Characterization                                                  | 17 |  |  |  |

|     |    | 2.1         | System Description                                                    | 17 |  |  |  |

|     |    |             | 2.1.1 Phase Locked Loop                                               | 18 |  |  |  |

| 100 |    |             |                                                                       | 19 |  |  |  |

|     |    |             | 2.1.3 Direct-Voltage Controller                                       | 20 |  |  |  |

|     |    |             | 2.1.4 Reactive-Power Controller                                       | 21 |  |  |  |

|     |    | 2.2         | LV Grid for Case Study                                                | 22 |  |  |  |

|     |    | 2.3         | 0 1                                                                   | 23 |  |  |  |

| 105 |    | 2.4         | 0                                                                     | 26 |  |  |  |

|     |    |             | 2.4.1 Asymmetrical Faults                                             | 26 |  |  |  |

|     |    |             | 2.4.2 Symmetrical Faults                                              | 27 |  |  |  |

|     |    | 2.5         | J 8 J                                                                 | 28 |  |  |  |

|     |    | 2.6         | Active and Reactive Current Transfer-limits during Symmetrical Faults | 30 |  |  |  |

| 110 |    |             | 0                                                                     | 30 |  |  |  |

|     |    |             | 0                                                                     | 31 |  |  |  |

|     |    |             | 2.6.3 Derivation of Current Transfer Limits                           | 32 |  |  |  |

|    | 2.7                      | Summary                                                                                                                                                           |                                                                                                                                                                         |         |         | • • •     | . 39                                         |     |

|----|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|-----------|----------------------------------------------|-----|

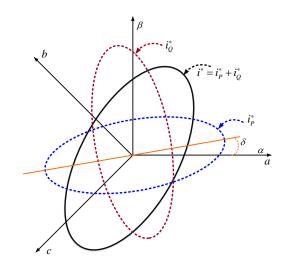

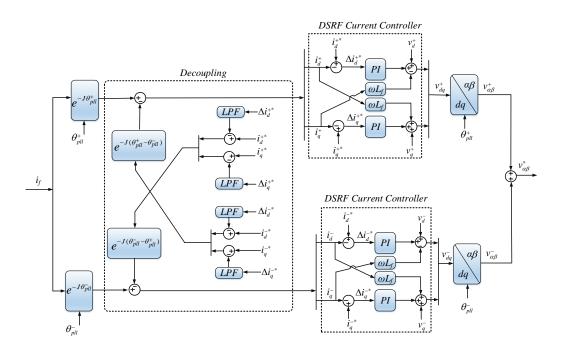

| 3  | Flex<br>3.1<br>3.2       | <ul> <li>3.0.1 Instantanee</li> <li>3.0.2 Symmetric</li> <li>3.0.3 FPNSC</li> <li>3.0.4 Sequence F</li> <li>3.0.5 Converter C</li> <li>DDSRF Current C</li> </ul> | <b>Negative Sequence Control for A</b> ous Power Theory         -Sequence based Instantaneous P         -Server Struction         Current Limitation         Controller | ?ower   | · · · · | · · · · · | . 41<br>. 43<br>. 43<br>. 44<br>. 46<br>. 49 | 115 |

| 4  |                          | em Implementatio                                                                                                                                                  |                                                                                                                                                                         |         |         |           | 51                                           |     |

|    | 4.1<br>4.2               | Model Verification                                                                                                                                                | llation Model                                                                                                                                                           |         |         | • • •     | . 52                                         | 125 |

|    | 4.2                      | 4.2.2 Case-01<br>4.2.3 Case-02                                                                                                                                    |                                                                                                                                                                         | · · · · | · · ·   | •••       | . 53<br>. 55                                 | 120 |

|    | 4.3                      | 2                                                                                                                                                                 |                                                                                                                                                                         | • • • • |         | •••       |                                              |     |

| 5  | Expe<br>5.1<br>5.2       | 5.1.1 Base Case-<br>5.1.2 Base Case-                                                                                                                              | ıp                                                                                                                                                                      | · · · · | · · ·   | •••       | . 58<br>. 59                                 | 130 |

| 6  | <b>Con</b><br>6.1<br>6.2 | Future Work and 2<br>6.2.1 DC-link dy<br>6.2.2 Wide comp                                                                                                          | e Work<br>Research Prospective                                                                                                                                          | <br>ts  | · · · · | ••••      | . 62<br>. 62<br>. 62                         | 135 |

| Bi | bliog                    | raphy                                                                                                                                                             |                                                                                                                                                                         |         |         |           | 63                                           | 140 |

| Α  | Арр                      | endix                                                                                                                                                             |                                                                                                                                                                         |         |         |           | 73                                           |     |

x

## Chapter 1

# Introduction

## 1.1 Background and Motivation

- <sup>145</sup> The increasing electrical energy consumption globally imposes an increased electrical production to meet the requirements. However, foreseen exhaustion of conventional fossil-fuel based energies (e.g-coal, oil and natural gas), has brought considerable worldwide attention towards sustainable energy production [1]. Additionally, fossil-fuel based generation causes emission of pollutant gases, which pollute

- the natural environment and causes global warming. Thus, fossil-fuel based energy generation is considered an unsustainable in long-term strategic plans. To that end, the desire to reduce the CO<sub>2</sub> emissions has made us more inclined towards penetration of renewable energy sources (RES), such as Wind Turbine Systems (WTs), Photovoltaic Systems (PVs) and Energy Storage Systems (ESSs) into the power sys-

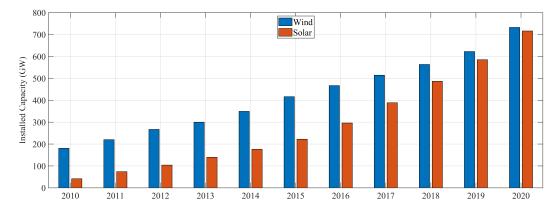

- tem [2]. Especially, the worldwide installed capacity of PVs and WTs are increased upto a great extent in past decade as depicted in Fig.1.1.

**Figure 1.1:** Global accumulative capacity of Wind and Solar in Giga Watt (GW) from 2010-2020 based on the data available from International Renewable Energy Agency (IRENA) [3]

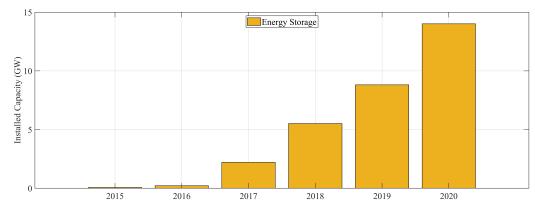

Figure 1.2: Global accumulative capacity of Energy Storage in GW from 2015-2020 based on the data available from International Energy Agency (IEA). [4]

On the other hand, ESSs like batteries have starting emerging in past few years and will be scaled upto 148 GW as per IEA as depicted in Fig.1.2 and they can provide more flexibility to the power system and market demands [4]. The global installed capacity of PVs is 720 GW, WTs is 740 GW and ESSs is 14 GW till the year <sup>160</sup> 2020.

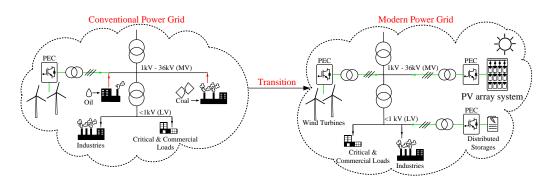

Figure 1.3: Renewable Energy Source (RES) interfaced in conventional and modern power grid

However, the conventional power grid is mostly dominated by fossil-fuel based generation and less RES at Low-Voltage (LV) and Medium-Voltage (MV) level [5]. The goal of achieving 100% renewable grid with variable renewable energy (VRE) systems are interfaced to the grid as in Fig.1.3. In order to comply these VRE systems to the grid. The transmission system operator (TSO) provide technical regulations to comply with the grid like National Grid ESO for Great Britain [6], TenneT for Germany [7] etc. Similarly, in Denmark Energinet the Danish national TSO has technical regulations for interconnection of RES to the grid defining minimum technical and functional requirements for different RES. The technical regulations 170 are divided into different categories based on the rated power at the Point of Connection (POC). The category for PVs and WTs are similar but Technical regulations

(TRs) vary as in [8].

Table 1.1: Category of plants based on the rated power at the point of connection

| Category | PVs and WTs / ESSs                                                        |

|----------|---------------------------------------------------------------------------|

| A2/A     | above 11 kW including 50 kW / up to 125 kW                                |

| В        | above 50 kW including 1.5 MW /including 125 kW up to 3 MW                 |

| С        | above 1.5 MW including 25 MW / 3 MW up to 25 MW                           |

| D        | above 25 MW or connected to over 100 kV / including 25 MW or above 100 kV |

While for ESSs both TRs and category of plants vary as in [8]. In this project,

only TRs for RES will be followed. Further, there can be multiple small WTs depending upon their configuration like Type-1 and Type-2 which consists of gear box with induction generator [9], Type-3 with Double fed Induction Generator (DFIG) having partial scale of PEC [9] and Type-4 with synchronous generator having full scale PEC [10] will be considered. While, for PVs and ESSs there is as

such no type.

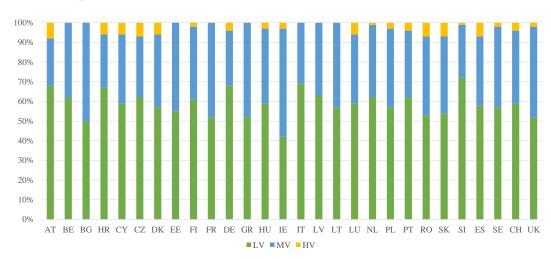

Figure 1.4: Share of distribution lines in Europe based on the data available from Euelectric (AT (Austria), BE (Belgium), BG (Bulgaria), HR (Croatia), CY (Cyprus), CZ (Czech Republic), DK (Denmark), EE (Estonia), FI (Finland), FR (France), DE (Germany), GR (Greece), HU (Hungary), IE (Ireland), IT (Italy), LV (Latvia), LT (Lithuania), LU (Luxembourg), MT (Malta), NL (Netherlands), NO (Norway), PL (Poland), PT (Portugal), RO (Romania), SK (Slovakia), SI (Slovenia), ES (Spain), SE (Sweden), CH (Switzerland) and UK (United Kingdom) [11]

In Europe, 60% power network is composed of LV lines (< 1kv), while rest 37% of MV lines (between 1kv and 36kv) and 3% of High voltage (HV) lines (> 36kv) as in Fig.1.4. In conclusion, the low-voltage lines are more widely distributed as compared to others and more prone to grid faults. However TSO's around the world does not show the requirement of Low-Voltage Ride Through (LVRT), in

order to support the power-system during grid faults. This can be a concern as recent instances have been recorded at DSO (Distribution System-Operator) level. Which represents the need of LVRT to avoid system instability. Power outages is also one of the main concern at DSO level to large number of customers as end users. The energy tangle in China is one of the example, where two dozen's of 190 China's 31 administrative units had rolling blackouts in the year 2004[12]. One of the main reason concluded for such frequent and unintended power outages was due to increase in **demand and shortage of generation** as they were highly dependent of fossil-fuel generation especially coal. A similar scenario was observed at the end of year 2000, where a massive blackout in the north-east of the US 195 and Canada happened due to similar reason as in China [13]. As we are moving towards power-electronics dominated grid (PEDG) both supply and demand stability with respect to power-converter control stability needs to be considered to avoid such situations [14].

Fault in power-system also leads to major blackout in Italy. The Italian blackout in the year 2003 on September 28<sup>th</sup> at 3:01 a.m., a fault on Swiss power-system due to overloading of two Swiss internal lines (interconnection lines heavily loaded by large power import) close to the border of Italy [15]. The coordination between the operators of Swiss and Italy were not sufficient enough to mitigate the overload. As a consequence, cascading outages on the interconnection lines to Italy. 205 This further resulted in loss of synchronism and loss of large import of power. Eventually, a large frequency decline in Italy, automatic load shedding procedure was not able to shed enough load to maintain the generation and load demand leading to blackout. A similar scenario occurred on 14<sup>th</sup> of August in the year 2003 in North America [16]. This blackout was the biggest that North America has ever 210 faced nearly affecting around 50 million people and 61,800 Megawatts (MWs) of load in states of Ohio, Michigan, Pennsylvania, New York and provinces of Canada (Ontario) [17]. Major blackouts reported up till now initiated by a single event or multiple faults gradually leading to cascading outages and eventually collapse of power system. Above instances discussed mainly occur due to faults on MV and 215 HV lines. Further, the impact of faults on LV lines causing system instability will be discussed.

In Europe, there are small islands which form their own regional power-system through variable RES penetration as they are far from synchronous generation units. There are various projects being carried out like for energy storage solutions 220 in Canary Islands, Ventotene, Faroe Islands, La Reunion, Tilos and Kythnos [18]. ESSs offer more flexibility and stability to the grid together with other PVs and WTs like Cyprus, Malta and Kythnos on LV network reducing the disturbances from the WTs and PVs , especially the disturbances in PVs [18]. These solutions on LV network like roof-top PVs, small WTs are paid for operating during ancillary 225 services [19]. In conclusion, the LV network needs to support the grid during faults

especially in standalone system as in Europe Islands. The next section will discus about power system faults and how instability phenomena occurs due to faults.

#### 1.2 **Power System Faults and Instability Phenomena**

Faults in power system are mainly weather-related [20]. The weather factors that 230 causes Short-Circuit (SC) faults are lightning strikes, heavy rain, strong winds or gales, accumulation of snow, fire and floods adjacent to electrical equipment (underneath overhead lines). Vandalism and human error are also the causes of SC faults, in certain cases there could be breach of minimum clearances between the trees and overhead lines. These are few of the factors that contribute to faults in 235 power system. However, equipment failure like transformers, machines, reactors, cables etc. may also cause faults.

Figure 1.5: Types of line faults with their distribution percentage and severity level[21]

The SC fault can be divided into balanced faults (symmetrical faults) and unbalanced faults (unsymmetrical faults) as in Fig.1.5. In symmetrical faults, three-phase  $(3-\phi)$  fault or  $3-\phi$  to ground fault. The severity of these faults is high but the chances 240 for occurrence of these faults is less then 5%. These faults occur mostly due to human error [20]. On the other hand, unsymmetrical faults can be single-phase  $(1-\phi)$ fault, double-phase  $(2-\phi)$  fault and phase-phase fault also called as Line-Ground (LG) fault due to physical contact like lightning [22], Double Line-Ground (DLG) fault due to storm [22] and Line-Line (LL) fault due to close contact of lines [22]. The severity of LG fault is lowest but the occurrence of this fault is the highest.

245

While, for LL and DLG fault the severity is medium. The LL fault is quite often to occur but less then LG fault. Further, the voltage sag/dip can be divided into seven distinct types depending on the type of fault and the connection (star or delta). At LV/MV/HV it depends on voltage at Point of Connection (POC) and the winding 250 connection of transformers.

Figure 1.6: Type-A (Sag-A) during symmetrical- Figure 1.7: Type-B (Sag-B) during unsymmetrical-faults. faults.

Type-A sag occurs due to three-phase  $(3-\phi)$  fault or  $3-\phi$  to ground fault. Where all the three phase ( $v_a$ ,  $v_b$  and  $v_c$ ) dips as in Fig.1.6. Type-B sag occurs due to LG fault for star connected load as in 1.7.

Figure 1.8: Type-C (Sag-C) during Figure 1.9: Type-D (Sag-D) during unsymmetrical-faults with phase jump. unsymmetrical-faults with phase jump.

Type-C sag occurs, due to LG fault for delta connected load and LL fault for 255 star connected load with phase jump as in Fig.1.8. Type-D sag occurs, due to LL fault for delta connected load.

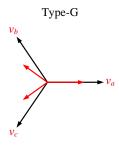

Type-E and F sag occurs due to LLG fault for star and delta connected load. While type-G sag also occurs for LLG fault but depends on the winding configuration of transformer.1.2 summarises the disused sags for different star and delta 260 connected load.

Figure 1.10:Type-E(Sag-E)duringFigure 1.11:Type-F(Sag-F)duringunsymmetrical-faults.unsymmetrical-faults with phase jump.

Figure 1.12: Type-G (Sag-G) during unsymmetrical-faults with phase jump.

Transformer winding configuration will cause a change in the type of sag from one voltage level to another. Balanced sags always remains the same neglecting the winding configuration. It only varies for unbalanced sags but can be summarised depending on type of transformer configuration. When both star points are grounded the sag on the secondary side is equivalent to primary side. Transformers remove the zero sequence voltage that means voltage of the secondary side is equivalent to voltage on primary side minus the zero sequence component. Usually for zero sequence component elimination, the transformer winding are usually star-star connected with one or both star points not grounded and the delta-delta transformer. While for the rest depending upon winding configurations the line and phase voltages vary. Table1.3 represents the the type of voltage dip on primary side w.r.t to secondary side for type 1, 2 and 3 transformers.

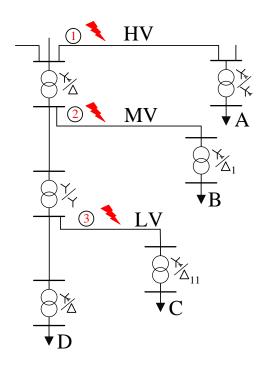

A grid-fault either on the HV or MV further propagates the fault to the LV. In order to describe this instability phenomena a simple distribution network is taken into account as in Fig.1.13 with loads A, B, C and D. The idea is to represent the instability phenomena irrespective of the transformer winding configuration. Where, the  $\Delta_1$  gives -30° phase-jump and  $\Delta_{11}$  gives +30° phase-jump to all the three phases. To that end, faults at HV, MV and LV will be discussed and how the

| Fault Type | Star-connected Load | Delta-connected Load |

|------------|---------------------|----------------------|

| LLL        | Туре А              | Туре А               |

| LLLG       | Type A              | Type A               |

| LLG        | Type E              | Type F               |

| LL         | Type C              | Type D               |

| LG         | Туре В              | Type C               |

Table 1.2: Three-Phase balanced and unbalanced sags

Table 1.3: Co relation between the secondary-side voltage dip w.r.t to primary-side

| Transformer Type | Type A | Type B | Type C | Type D | Type E | Type F | Type G |

|------------------|--------|--------|--------|--------|--------|--------|--------|

| Type 1 (YGyg)    | А      | В      | С      | D      | Е      | F      | G      |

| Type 2 (Yy,Dd)   | А      | D      | С      | D      | G      | F      | G      |

| Type 3 (Yd,Dy)   | А      | С      | D      | С      | F      | G      | F      |

customers at A, B, C and D will experience the sag/dip. As represented in Fig.1.13 280 if we have a fault at position 1 (HV) will cause a deep sag for the substations connected to the faulted lines. Further, then this sag will propagate to the customers at A, B, C and D. The customers C and D will be out of power as there will be nothing to keep up the voltage. Next the fault at position 2 (MV) the customer B will experience a deep sag. It will not cause a much voltage drop for customer 285 A as the impedance between the HV and MV is large enough to limit the voltage drop for the customer A. While, customer C and D will also experience voltage dip. Finally, fault at position 3 (LV) will cause a power outage for customers C and D, while customer B will experience a small voltage dip but customer A won't be affected at all. In conclusion, customers C and D will be the most affected as there 290 will be nothing to keep up the voltage. This represents the need of certain functionalities from IBR at LV to support the grid during faults and also help during the grid voltage recovery. To counter this problem and to avoid system instability. Therefore a need to comply with certain grid requirements is required to avoid such scenarios. 295

#### 1.3 **Grid Requirements**

In order, to comply with the grid requirements during faults. There are certain requirements or minimum functionalities that a RES should provide during such conditions. For LV the Energinet does not provide any requirements to support during grid faults. As discussed above section the LV side requires the need to 300 support the grid during faults. The worst scenario was taken into account by

## 1.3. Grid Requirements

Figure 1.13: Distribution network with fault positions and load positions

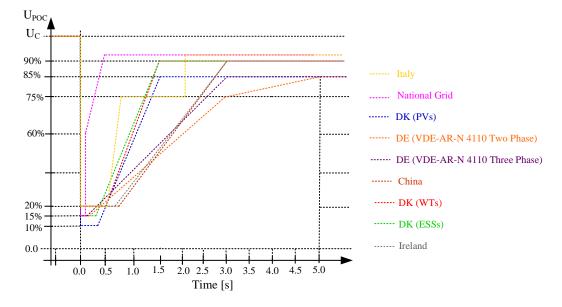

taking different FRT requirements as represented in Fig.1.15 for MV. Where,  $U_c$  is normal operating voltage (line-line voltage) and  $U_{POC}$  is normal operating voltage at the POC.

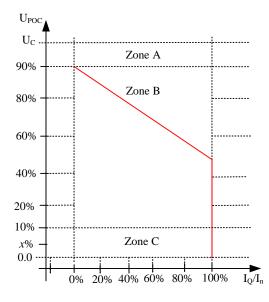

- <sup>305</sup> Where, Fig.1.15 represents the worst case scenario with the voltage dip upto 10%, considering the worst case scenario would be x% that is severe faults. Zone A means the RES should remain connected to the grid and maintain normal production. Zone B is where the RES should remain connected to the grid and provide maximum voltage support with an injection of controlled reactive current. Finally,

- <sup>310</sup> in Zone C disconnection of unit is allowed. It should be noted that the requirement implies to all the three-phases during fault. Individual unit is responsible for reactive current injection even at farm level. The reactive current ( $I_Q$ ) injection with tolerance of +10% and -10% as in Fig.1.16. Full reactive current injection should be done below 0.5 *pu* voltage drop. This condition is also applicable during normal

- <sup>315</sup> operating conditions or even after disconnection of fault. It should be done in a controlled manner to avoid over-voltage and be within inverter limitation. It is worth mentioning that full priority will be given to reactive power injection during faults especially below 0.5*pu* voltage drop.

Figure 1.14: Fault Ride Through (FRT) requirements for China [23], DK PVs [5], DK WTs [5], DK ESSs [5], DE [24], National Grid (UK) [25], Ireland [26] and Italy [27]

## **1.4** State of the Art

Voltage dips experienced due to short-circuit grid faults have a impact over the 320 industries especially adjustable speed drives, which trips off to avoid damage to power electronics components [28]. Classical methods like dynamic voltage restorer, static synchronous compensator were introduced to retain the grid voltage. Analysis of time domain and phasor sequence networks were introduced during voltage dips [29]. The grid current shoots up during such scenarios causing insta-325 bility. Earlier, to encounter this series LC circuits were introduced to limit the fault current [30]. Further, analysis of Voltage source converter (VSC) is carried out to analyse the impact of faults in conventional *dq*-reference frame [31]. The proposed methodology in [31] represents the elimination of  $2\omega$  oscillation from the power controller but as such LVRT studies were not carried out. DC-link voltage stability 330 during faults was one of the main encountered issues in inverter drives [32]. To eliminate the influence of  $2\omega$  oscillation and avoid overshoot of DC-link during LVRT conditions from the reference power  $(P^*)$  [33].

Analysis for injection of power during grid-faults utilising second-order generalised integrator (SOGI) as a band-pass filter (BPF) to extract the negative and positive sequence voltage. This is done to eliminate the power oscillations but introduces **highly distorted grid current** [34] and **poor power-quality** [35]. Studies for Type-3 WTs and wind farms were carried by following grid-compliance for LVRT condition [36–38],[39] and controlled reactive current injection [40] dur-

## 1.4. State of the Art

Figure 1.15: Low Voltage Ride Through (LVRT) requirements for the RES at LV grid.

- <sup>340</sup> ing faults. The injection of active current during faults needs to be limited to avoid loss of synchronism (LOS) of generation units [41]. Further, current injection method were proposed for avoiding the risk of over current during faults by providing correct reference currents from outer loops [42],[43]. The instability of PLL with the reference current generation in addressed through large signal model for

- PLL. However, this method considers the interaction of converter to the utility grid under weak grid conditions [44]. However, the above methods **neglected the DClink dynamics**. In order to reduce the  $2\omega$  oscillations during asymmetrical faults sequence extractor was utilised to generate the current references [45, 46] and a sample-hold method with sequence extractor for generating voltage reference val-

- <sup>350</sup> ues for each phase [47]. Low-pass filter (LPF) and Band pass filter (BPF) were also utilised, while sequence extraction but the phase-delay introduced by filters were neglected [48]. The aforementioned methods did not discus the phenomena of LOS as the they only consider reactive power injection during voltage dips.

To mitigate the LOS by avoiding power balance at the POC frequency based active current injection method is introduced depending upon the voltage dip [49]. PLL freezing during such events was on of the possibility to avoid LOS of generating unit [50–52]. **Equal Area Theorem (EAC)** is utilised for PLL in later phase to provide additional damping by taking the conditions before and after fault [53]. This would reduce the 2*ω* oscillations from PLL during asymmetrical faults. Ad-

ditional filtering units like Low-pass notch filter can be utilised to mitigate  $2\omega$  oscillations but increases the complexity of PLL and introduces phase delay [54]. The major disadvantage of EAC is that it neglects the damping of PLL, which can

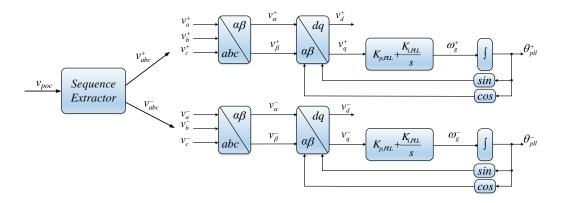

**Figure 1.16:** Reactive current  $(I_O)$  and nominal current  $(I_N)$  injection during voltage dips.

be achieved by carrying small-signal stability of PLL to achieve stability [55]. A lot of attention is brought towards PLL to avoid LOS during short-term voltage stability. However, few methods were proposed by considering different variations 365 in PLL for transient stability like adaptive damping [56], interaction with outerloop [57] and phase portrait analysis [58]. It should be noted that the focus of this project on short-term voltage stability not long-term voltage stability [59]. Methods carried out for transient stability can be utilised for the synchronisation stability as well. Active power reference generation based on PLL frequency error [60] and 370 actual output power [61] to avoid LOS and improve stability after fault is clear. Advance PLL and FLL (frequency-locked loop) like DSOGI (Double Second Order Generalised Integrator) [62] and DROGI-FLL (Dual Reduced-Order Generalised Integator-Frequency Locked Loop) [63, 64] were introduced for sequence extraction and frequency stability. Further, to extract positive and negative sequence of 375 feedback-current DDSRF (Decoupled Double Synchronous Reference Frame) controller were used extensively to inject positive sequence current [62]. Stability of PLL to avoid LOS and provide voltage stability by maximum reactive power injection is one of the concern. This also introduces  $2\omega$  oscillations in the injected active and reactive power during faults. The outer-loop controllers dynamics have 380 been neglected, which have a high impact of the power injected. The term synchronisation and transient stability were mixed up quite often for short-term voltage stability events. The next section discusses the formulation of the problem.

## 1.5. Problem Formulation

| Ref.     | Year | Proposal / Drawbacks                                                                |

|----------|------|-------------------------------------------------------------------------------------|

| [31]     | 2005 | Mitigation of negative sequence current / FRT requirements not followed             |

| [34]     | 2007 | Instantaneous active reactive control / Distorted grid current.                     |

| [41]     | 2009 | Active current injection limitation during voltage drop / DC-link neglected.        |

| [42]     | 2011 | Reference current generation to avoid over current / DC-link neglected.             |

| [44]     | 2012 | PLL based frequency stability / FRT requirements not followed.                      |

| [47]     | 2013 | Generation of voltage references by sample-hold method / DC-link neglected.         |

| [49]     | 2014 | Frequency based active current injection / Converter current-limitations neglected. |

| [50]     | 2014 | K-factor impact on system / line-impedance characteristics neglected.               |

| [53]     | 2014 | Large-signal stability analysing of PLL (EAC) / FRT requirements not followed.      |

| [65]     | 2015 | PLL stability considering impedance interaction / ([44]).                           |

| [54]     | 2015 | Low-pass notch PLL for mitigation of $2\omega$ oscillations / Complex PLL.          |

| [55]     | 2016 | PLL bandwidth variation to achieve stability / FRT requirements not followed.       |

| [56]     | 2018 | Adaptive PLL damping method / DC-link neglected.                                    |

| [57, 66] | 2018 | Interaction of active power loop with ROCOF / DC-link neglected.                    |

| [58]     | 2018 | Phase portraits for PLL analysis / line-impedance characteristics neglected.        |

| [67]     | 2018 | Current vector alignment with line impedance to avoid LOS / DC-link neglected.      |

| [60]     | 2018 | Active power references based on PLL frequency error / STATCOM is included.         |

| [51, 52] | 2018 | PLL freezing with phase compensation / Complex PLL system.                          |

| [68]     | 2019 | Power-synchronization control for stability / DC-link neglected.                    |

| [61]     | 2019 | Active power reference based on output power / DC-link neglected.                   |

| [62]     | 2020 | Current reference generation based on DSOGI-PLL / Complex-PLL.                      |

| [63]     | 2020 | DROGI-FLL for sequence extraction / Complex PLL methodology followed.               |

| [64]     | 2020 | Amalgamation of DROGI-FLL with PLL-freezing for frequency stability / [63].         |

| [69]     | 2022 | Dual-sequence model to avoid LOS / Complex PLL methodology followed.                |

| [70]     | 2022 | Automatic voltage regulation with PLL / DC-link dynamics neglected.                 |

| [71]     | 2022 | Large-signal stability analysis by Lyapunov method / Only PLL is considered.        |

## **1.5 Problem Formulation**

As discussed in last section, different methods were introduced to **avert the LOS** and **mitigate the**  $2\omega$  **oscillations** during fault events. Most of the research ideas have been introduced on PLL to remain synchronised and provide voltage and frequency stability by injecting high reactive current for a single unit. Moving towards advance PLLs or FLLs always provide more stability but are **complex**,

high computational burden such systems are not suitable for LV systems, which requires cheap and less complex solution. Moreover, outer-loop controller dynamics are neglected especially DC-link controller dynamics. It has a huge impact over

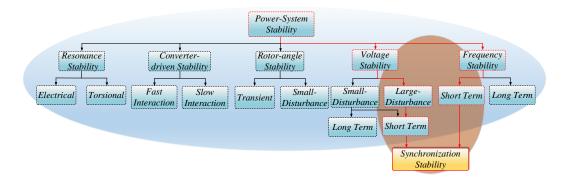

the active-current injection to maintain power-balance between the sending and receiving end. This brings us to one of the main issue that is misconception between the terms synchronization and transient stability. There is as if no definition neither 395 for synchronization stability or transient stability. As per power-engineering task force, the classification of power-system stability can divided into five categories as represented in Fig.1.17 highlighted in blue oval. While, the red oval represents the terms considered for synchronisation stability of a single-unit. The focus of the project is only on **voltage-stability** and **frequency-stability**, where grid-faults 400 are considered as short events (150 ms) this brings us to short-term voltage and frequency stability. Further, considered as synchronisation stability.

Figure 1.17: Classification of power-system stability [59] (blue oval) and synchronization stability (red oval).

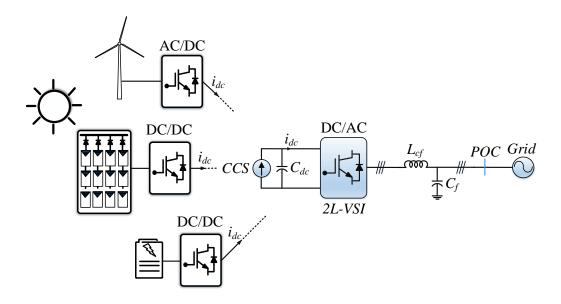

However, when the voltage drop is very low at point of connection (POC) drop or rise in frequency can be observed depending upon active and reactive current injection during faults. While, for asymmetrical-faults the situation is quite worst 405 as it leads to generation of  $2\omega$  oscillations. An overview of the considered system is represented as in Fig.1.18. This bring us to the objectives of this project discussed in next section.

#### 1.6 **Project Objectives**

The grid-following converters are at the risk of frequency instability under severe 410 faults. Eventually, leading to loss of synchronisation of the unit from the grid. Losing a generating unit under such scenarios will also impact the frequency and voltage stability of the low-voltage grid. From recent studies synchronisation unit (PLL) has been identified as one of the aspects for loss of synchronization. To avert the loss of synchronization few methods like PLL freezing, advance frequency-415 locked loops have been implemented but have high computational burden and complex. While, PLL freezing method is tend to have a frequency drop during re-synchronization. This projects aims to study the impact of asymmetrical faults

Figure 1.18: Generic overview of Grid-following (GFL) inverter with current controlled source (CCS).

initially by taking in account the impact of line impedance for a low-voltage network. Generation of second-harmonic oscillations during such events is also one 420 issues having impact over the power quality. Eventually, those second harmonic oscillations will also disturb other generating units. However, there are as such no appropriate methods defined to mitigate or damp these oscillations. An attempt will be made to damp these oscillations under such events. This project will focus on two main questions:

```

425

```

- How to avert the LOS during severe grid-faults ?

- How to damp the generation of  $2\omega$  oscillations during asymmetrical faults ?

The considered objectives will initially be analysed considering basic-control loops and modifications will be made by introducing additional control strategies without neglecting basic control loops as per requirement.

430

#### 1.7 Methodology

The following methodology will be followed to reach the project objectives:

• Initially, as depicted in 1.18 considering only the grid-side converter (DC/AC) will be considered.

450

- The grid-side converter will be modeled in PLECS (Piecewise Linear Electri- <sup>435</sup> cal Circuit Simulation).

- The control strategy will be implemented initially in s-domain (continuous domain) and then moved to z-domain (discrete domain).

- Once it is implemented fully in z-domain, results will be verified on the lab setup. 440

## **1.8** Scope and Limitations

The scope and limitations of this project are as follows:

- All dynamics corresponding to energy conversion are neglected in this project. This includes maximum power-point tracking for PVs and WTs and state of charge for ESSs. Only AC-side dynamics are considered to the grid. This can 445 be assumed only grid-side converter control dynamics will be considered.

- The external network for a grid-connected converter is assumed to be Thevenin equivalent.

- Influence of power-system protection schemes associated with circuit breakers or any protection schemes is neglected.

- Grid impedance variation is neglected during this work.

- There is as such no requirement of transformers on LV network.

## 1.9 Content of Report

The report is divided into six chapters mainly. *Chapter-1* mainly discuses the motivation to carry out the project by considering real-life examples following with <sup>455</sup> occurrence of power-system faults and propagation of faults. Grid-code requirements are addressed for LV networks. Finally, an overview of recent methodologies followed is discussed in state of the art. *Chapter-2* discuses the system characterization and the problem identification during faults from conventional method point of view. The current transfer limits for symmetrical faults are discussed considering different scenarios. *Chapter3* introduces solution for asymmetrical faults to provide flexible control during unbalanced grid conditions. *Chapter-4* and *Chapter-5* discus the solution for the studies carried out for off-line studies and experimental work. Finally, *Chapter-6* discusses the conclusion from the studies carried out reflecting the advantages of the solution proposed for asymmetrical faults and 465

## Chapter 2

# **System Characterization**

This chapter gives a brief overview of the control structure for the grid-following 470 converter. The system description provides the small-signal analysis for the inner and outer loops. Then the description of low-voltage grid considered during studies is discussed. This brings us to the FRT implementation by conventional method for symmetrical and unsymmetrical faults. Finally, an in depth problem identification for symmetrical and unsymmetrical faults is carried out.

## 475 2.1 System Description

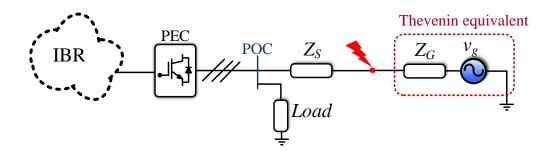

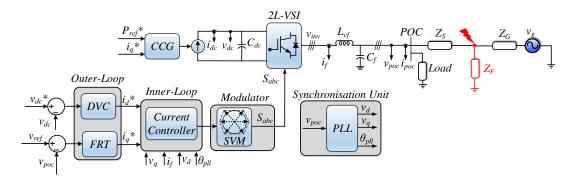

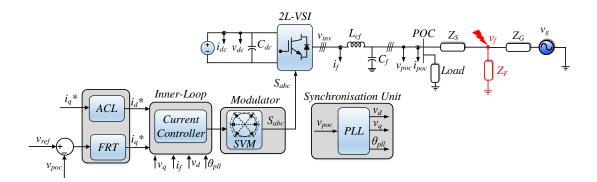

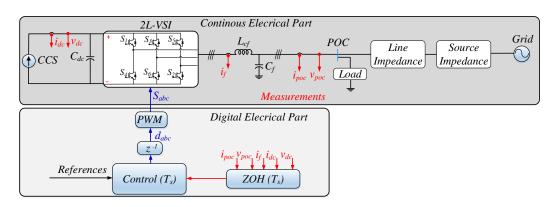

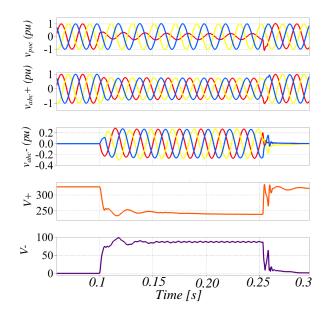

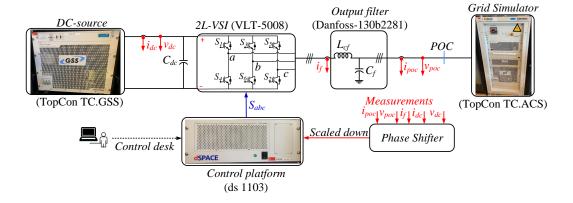

Figure 2.1: Schematic of grid-following converter with current controlled source (CCS) [72]

The general structure of grid-following converter is represented as in Fig.2.1 with synchronous reference frame control, also know as *dq* control. It consists of a synchronisation unit also called as phase-locked loop (PLL), which extracts the phase angle of grid voltages. The outer loop controllers mainly consists of Direct voltage controller (DVC) also called as dc-link voltage controller, which controls

480

the voltage across the dc-link capacitor ( $C_{dc}$ ). While, the Reactive power controller (RPC) controls the injection of reactive power into the grid. Usually, the reactive power reference is set to zero, if the manual control is not allowed. Finally, the inner-loop consists of current controller, which can control both the converter current  $(i_f)$  or the grid current  $(i_{poc})$  depending upon the type of control. However, 485 converter current control is utilised due to protection requirements for converter side and compensating the reactive power generated by filter. Here, space vector modulation (SVM) is utilised as the modulation technique, which provides the switching pulses to the inverter together forming a closed-loop control. As we know, the *dq* frame control is normally associated with the proportional-integral 490 (PI) controllers as they satisfy the behaviour of regulating dc variables. Next, subsection discusses the small-signal stability analysis for the desired controllers.

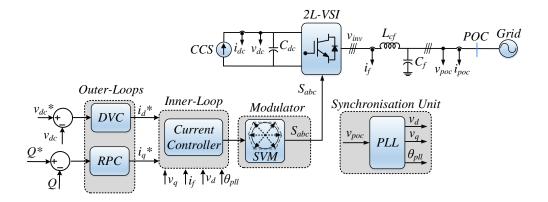

#### 2.1.1 Phase Locked Loop

Figure 2.2: Structure of SRF-PLL used to estimate the phase angle of the POC (Point of Connection)

The basic structure of PLL consists of three main parts, i.e., a phase detector (PD), low-pass filter (LPF) and voltage controlled oscillator (VCO) as represented 495 in Fig.2.2. In order to inject the desired active and reactive power into the grid. The three phase grid voltage  $(v_a, v_b, v_c)$  from the voltage at point of connection  $(v_{poc})$ are transferred into two phase voltage  $(v_{\alpha}, v_{\beta})$  by Clarke transformation. The Park transformation is applied to obtain the two phase voltage  $(v_d, v_q)$  in synchronous reference frame. The PI controller is adopted as a low-pass filter, where the  $v_q$  is 500 selected as the input. Then the q - axis component is regulated to zero, so the grid voltage can be aligned to d - axis. Finally, the dq - axis coupling can also be achieved. Once the grid frequency  $(\omega_g)$  is obtained the integrator is implemented to get the phase angle  $(\theta_{pll})$  and reverted back to the Park transformation. The closed-loop transfer function can be written as is equ.2.1: 505

### 2.1. System Description

$$G_{2nd}(s) = \frac{2\zeta\omega_N s + \omega_N^2}{s^2 + 2\zeta\omega_N s + \omega_N^2}$$

(2.1)

where,  $\zeta$  is the damping factor and  $\omega_N$  is the natural oscillation frequency. The gains of PI controller can be calculate as in [73]:

$$K_p = \frac{9.2}{T_{set}} \tag{2.2}$$

$$T_i = \frac{T_{set}\zeta^2}{4.3} \tag{2.3}$$

The damping factor is chosen as 0.707, since it provides overshoot less then 5% in step response. The settling time  $(T_{set})$  is chosen as 100ms [73]. Finally, the  $K_P$ and  $T_i$  can be calculated as in equ.2.2 and equ.2.3.

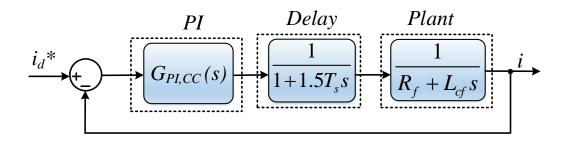

#### **Current Controller (CC)** 2.1.2

In order to control the current injected into the grid. The converter current or grid current can be controlled with a negative feedback loop. Here, the converter current is controlled in synchronous reference frame as PI controller [74]. As we know the response time of inner-current loop is much faster then the outer-loops. The disturbance due to grid-voltage (feed-forward) are neglected. The relation between the converter current and voltage can be defined as in equ.2.4.

$$G_{i_f(s)} = \frac{i_f(s)}{v_{inv}(s)} = \frac{s^2 + w_{LC}^2}{L_{cf}s(s^2 + w_r^2)}$$

(2.4)

where,

$$w_r = \sqrt{\frac{L_{cf} + L_{gf}}{L_{gf}L_{cf}C_f}}$$

(2.5)

and

$$w_{LC} = \frac{1}{\sqrt{L_{gf}C_f}} \tag{2.6}$$

Since, the grid side filter  $(L_{gf})$  is not present. So, the  $\omega_r$  (resonance angular 520 frequency) and  $\omega_{LC}$  (resonant angular frequency) of the filter can't be calculated. This would avoid the complexity of the third order plant as in equ.2.4. The plant function will be considered equivalent to an inductor. For the worst case scenario resistance of the filter cab be neglected, but a proper step-response can't be achieved. To fulfil this requirement resistance is taken as 0.1pu of the  $L_{cf}$ . A trans-525 port delay is induced by the PWM technique, by making a sample delay caused

510

515

530

due to digital implementation. Symmetrical PWM is utilised here that means single sample within a switching period. In total we have a delay of  $1.5T_s$  with a delay of one switching period in symmetrical PWM. The open-loop transfer function can be represented as in equ.2.7.

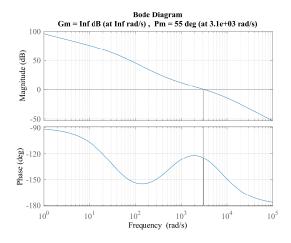

$$G_{OL}(s) = \frac{K_{p,cc}s + K_{i,cc}}{s} \frac{1}{1 + 1.5T_s s} \frac{1}{R_f + L_{cf} s}$$

(2.7)

It is worth mentioning that the d axis and q axis have the same dynamics. The tuning of d axis is only considered here. The small-signal control block is represented as in Fig.2.3.

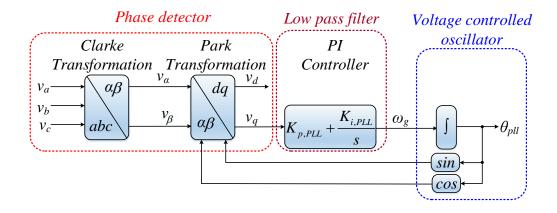

Figure 2.3: Small-signal control block diagram for the current-controller [75]

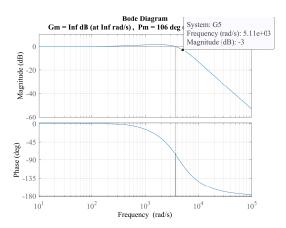

Finally, in order to calculate the  $K_{p,CC}$  (proportional gain of CC) and  $K_{i,CC}$  (integral gain of CC). Either modulus optimum can be utilised by zero-pole cancellation or Matlab toolbox, Sisotool. The relative stability is considered with gain margin larger than 6dB and phase margin greater than 45 degree in open-loop [76]. Finally, the bandwidth of the CC should be between 500 to 1000 Hz for the considered switching frequency in closed-loop. The bode-plot for open-loop appendix update needed .

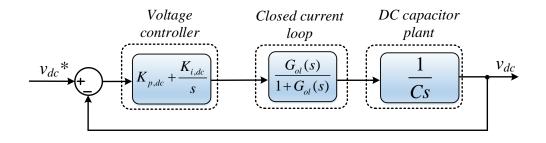

## 2.1.3 Direct-Voltage Controller

The outer voltage loop also called as DC link voltage controller or Direct voltage controller. The DC link is not constant and needs to be regulated properly to achieve a proper power balance between both the converters. The minimum dc link voltage should be greater then the three-phase line to line peak voltage on AC <sup>545</sup> side. The dc link is not constant and time varying. In order to regulate a constant dc voltage across the DC link capacitor ( $C_{dc}$ ), voltage controller needs to be employed. The rule of thumb is that the bandwidth of dc link voltage controller should be 10 times slower then the current controller to achieve a decoupled control [77].

In order to establish the relationship between the dc and ac side instantaneous <sup>550</sup> power is considered. Usually, converter losses are neglected during the design

### 2.1. System Description

of controller. The overall block diagram is represented as in Fig.2.4. The voltage controller consists of the PI controller with  $K_{p,dc}$  (proportional controller) and  $K_{i,dc}$  (integral controller). Then the closed-loop transfer function of current controller is considered, it can also be taken as equivalent to 1 as the inner-current loop are faster then outer loops. Finally, the DC capacitor plant transfer function is considered as 1/(Cs). The open-loop transfer function is represented as in equ.2.8.

$$G_{OL_{dc}}(s) = \frac{K_{p,dc}s + K_{i,dc}}{s} \frac{G_{ol(s)}}{1 + G_{ol}(s)} \frac{1}{Cs}$$

(2.8)

Figure 2.4: Small-signal control block diagram for the DC-link voltage controller [78]

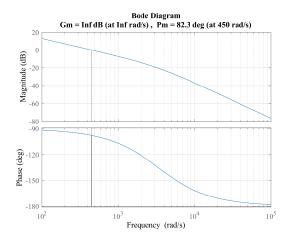

The tuning of PI controller is implemented using symmetrical optimum [79]. This method can give a initial point following the relative stability giving the required gain margin and phase margin. The open-loop and closed-loop bode plot with step response is discussed in Append.A.

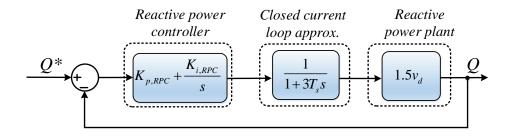

## 2.1.4 Reactive-Power Controller

Figure 2.5: Small-signal control block diagram for the Reactive power controller [80]

The reactive-power controller (RPC) is for providing the manual reactive power as per requirement. However, it can also be utilised as a part of Q-V droop control. In this project it is neglected. The block diagram for RPC is represented as in

555

Fig.2.5. The closed-loop transfer function of current controller is approximated or it can also be taken as equivalent to 1 as the outer-loops are slower than the inner current loop. On the other hand, the plant transfer function can be derived as in equ.2.9.

$$Q = \frac{3}{2}(v_q i_d - v_d i_q) = -1.5v_d i_q$$

(2.9)

The plant transfer function can be roughly estimated as  $1.5v_d$ . It should be noted that the bandwidth of RPC should be lower then DC-link voltage controller to achieve a decoupled control between the DVC and the RPC. The open and closed loop response with bode-plot is discussed in Append.A.

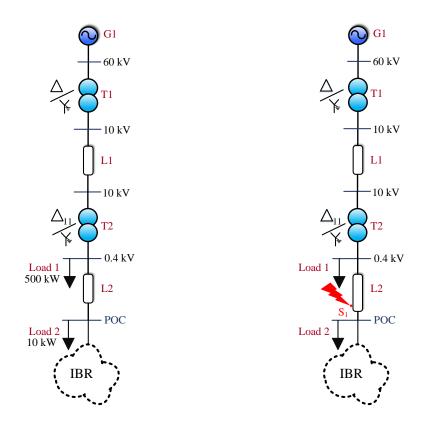

## 2.2 LV Grid for Case Study

This section discuses the details of LV distribution grid used for further studies. As schematic diagram of one of the feeder connected to MV network is considered as represented in Fig.2.6.

The schematic consists of HV grid (G1) with nominal voltage of 60 kV. The short circuit ratio (SCR) is set to 30 with X/R of 10. The source impedance param-580 eters were neglected and considered as default. A step-down transformer (T1) is connected with delta-Y configuration. The nominal power of T1 is 25 MVA with resistance and leakage inductance equivalent to 0.0041104 pu and 0.102918 pu. The magnetisation resistance and inductance were taken as default. L1 is a 12 kV MV cable of 10 km length with zero (*Ro*) and positive (*R*1) sequence resistance of 0.508 585  $\Omega/km$  and 0.0841  $\Omega/km$ . The zero (Xo) and positive (X1) sequence reactance is taken as 0.31  $\Omega/km$  and 0.068  $\Omega/km$ . A step-down transformer (T2) is connected having delta11-Y configuration with nominal power of 630 kVA. The winding resistance and leakage inductance were taken as 0.009 pu and 0.0471487 pu. Two loads of 500 kW (Load 1) and 10 kW (Load 2) were connected at 0.4 kV bus and POC 590 as represented in Fig.2.6. Line (L2) is a LV between the T2 and POC of 3 km with positive sequence resistance (0.3208  $\Omega/km$ ), reactance (0.075398  $\Omega/km$ ) and capacitance  $(0.56 \ microF/km)$ . It should be noted that the LV line is an underground cable, which are highly resistive with pi-section line. Finally, an IBR is connected at the POC. This concludes the overall parameters of the considered system. 595

The fault is considered a **km** away from the POC at  $S_1$  on LV cable as represented in Fig.2.7. The simplified schematic is represented as in Fig.2.8. The external grid is considered as Thevenin equivalent grid ( $v_g$ ). The line impedance is taken as ( $Z_s$ ), while source impedance ( $Z_G$ ) is taken as default. The next section discuses the fault ride through implementation. It should be noted that to vary the voltage dip fault-impedance will be varied.

575

570

**Figure 2.6:** System considered for fault scenario **Figure 2.7:** Point of fault ( $S_1$ ) for the considered considering line (L1, L2) and grid (G1) impedance system from the POC. in Thisted, Denmark [81, 82]

In order to comply with the grid requirements as discussed in Ch.1. To remain

## 2.3 Fault Ride through Implementation

605

610

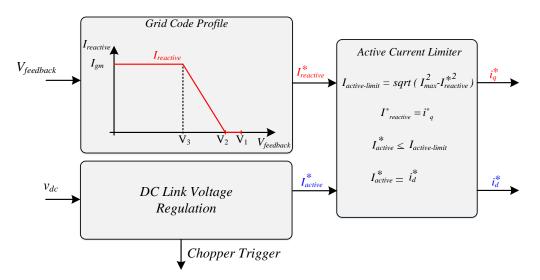

connected and support the grid during faults. The conventional method is represented as in Fig.2.9. Where  $I_{gm}$  is the maximum is the maximum reactive current as per grid code requirements. As per the requirement 1 pu reactive current needs to be injected during 0.5 pu voltage drop. During such scenarios reactive current is given priority over active current to support the voltage. The conventional method to generate active and reactive current references are represented as in Fig.2.9. The reactive current references is dependent on voltage drop. The active current drops down to zero or low depending upon capability of converter limits. The excessive power flowing to the DC side is usually dissipated by the chopper resistance. As in Fig.2.9, the reactive current reference  $(i_q^*)$  is dependent upon voltage drop as per grid profile. If the converter current is controlled that adds an additional reactive

**Figure 2.8:** Simplified system considering the line impedance ( $Z_S$ ) from the point of fault ( $S_1$ ).

power or pre-fault current. Consideration of additional pre-fault current is omitted from the method. The DC link voltage regulation is neglected in recent work during symmetrical faults. This will be taken under consideration during problem identification in next section. The remaining active current capacity ( $I_{active-limit}$ ) is generally calculated based on the maximum current capacity ( $I_{max}$ ) of the converter under normal conditions.

Figure 2.9: Conventional method for current reference generation during fault

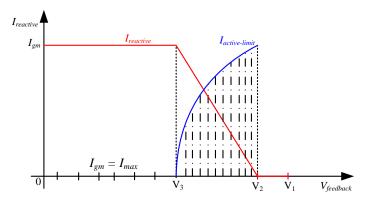

The current reference generation as per the grid code are represented as in Fig.2.10. The maximum reactive current ( $I_{gm}$ ) is equivalent to  $I_{max}$  at  $V_3$  that means maximum reactive current injection by the converter. However, a grid-side converter can go up to 1.2 pu, an additional 0.2 pu can be considered for safety margin. The remaining 0.2 pu can be utilised as the remaining active current injection  $^{625}$  during faults. The shaded areas in Fig.2.10 represents that active current injection can vary depending upon the grid code requirements.

**Figure 2.10:** Current references with conventional method ( $I_{gm}=I_{max}$ )

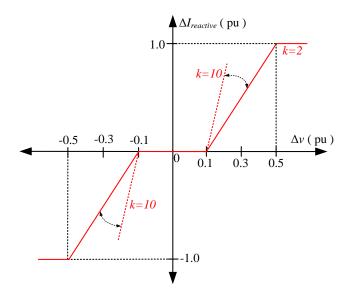

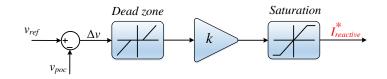

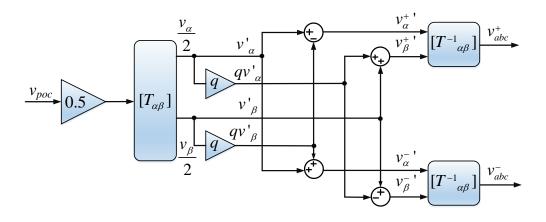

During a positive sequence voltage drop or voltage drop at  $v_{poc}$ , the RES are required to stay connected to the grid. To fulfill this requirement positive-sequence reactive current needs to be injected to provide voltage stability. This implies dur-630 ing both symmetrical and asymmetrical faults. As per Energinet, the reactive current ( $\Delta I_{reactive}$ ) injection depending upon voltage drop ( $\Delta v$ ) can be represented as in Fig.2.11. Where, k is the factor dependent upon grid code requirements. Here, k equivalent to 2 is considered with the objective of full reactive current injection during 0.5 pu voltage drop. However, k can be varied but should be less then 635 equal to 2. The grid codes are only prepared for positive sequence voltage drop for symmetrical faults but during asymmetrical faults negative sequence voltage also arises. There as such no separate requirements for negative sequence reactive current injection for asymmetrical faults because it has adverse effects like power oscillations, non-faulty phase rises over nominal value leading to Over-Voltage 640 Ride Through (OVRT) [83].

To fulfill the strict grid code requirements as in 2.11. The Conventional Method (CM) as represented in Fig.2.12 following the reactive current injection. Where, dead zone is applied to avoid any voltage support for 0.1 *pu* voltage drop or rise [8]. <sup>645</sup> While, the saturation block is applied to avoid entering into overexcited operation. In conclusion, the  $I_{reactive}^*$  can be depicted as in equ.2.10. This is also called as Fault-Ride Through (FRT) block as it provides voltage stability. Next section discuses about the problem identification during asymmetrical and symmetrical grid faults as per CM.

$$\Delta I_{reactive}^* = k.(\Delta v - 0.1) \tag{2.10}$$

Figure 2.11: Reactive current injection during faults as per [8]

Figure 2.12: Reactive current injection as per Fig.2.11

## 2.4 Problem Identification during FRT

This section discusses about the identification of problem by CM during asymmetrical and symmetrical grid faults. It also gives a short overview of how CM is implemented following grid code requirements.

#### 2.4.1 Asymmetrical Faults

The CM employing complying with grid-code requirements is represented as in  $_{655}$  Fig.2.13. The converter-current reference generator (CCG) block is responsible for varying  $i_{dc}$  during faults.

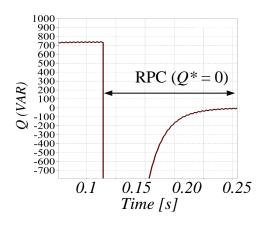

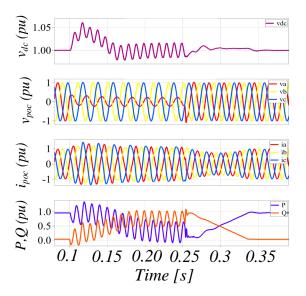

The CM method injects only positive sequence current during asymmetrical faults thus boosting the voltage for all the phases including non-faulty phase. This would create a voltage boost for the non-faulty phases at the point of fault [83]. 660 However, zero sequence current and voltage will be attenuated due to dYN transformers present in the system as they provide grounding for the grid side [84].

#### 2.4. Problem Identification during FRT

Figure 2.13: Aggregated model for asymmetrical faults

Detailed analysis of asymmetrical fault by CM method is discussed in Chapter4 as Case-02. The next sub-section discusses the loss of synchronisation during symmetrical faults.

665

670

### 2.4.2 Symmetrical Faults

During symmetrical faults the voltage dip across all the phases is same. This eliminates the necessity of sequence extraction methodology. Loss of Synchronizm (LOS) has been reported in recent studies [84]. This may vary from the type of system and the line impedance parameters taken into consideration. LOS is highly dependent on the type of current injection during faults. It is worth mentioning that reactive current injection will be given priority during faults. This will be discussed in detail by considering different scenarios during severe faults. It should be noted that the point of fault ( $v_f$ ) remains the same.

Figure 2.14: Aggregated model for symmetrical faults

## 2.5 Loss of Synchronization during Symmetrical Faults

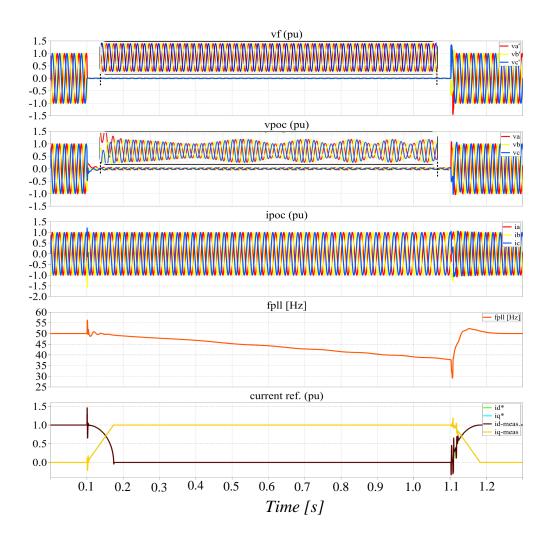

This section discusses the LOS during severe symmetrical faults. Two different cases will be considered with different current injection angle to analyse the limits to avert LOS. The fault-impedance  $(Z_f)$  is kept low to create a severe fault.

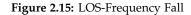

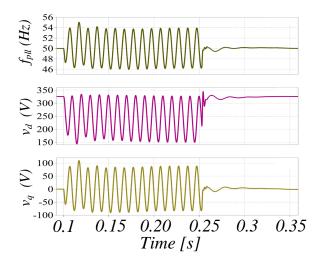

Initially, full reactive-current  $(i_q)$  is injected with  $v_f$  equivalent to 0.035 pu as represented in Fig.2.15. It can be noticed that the frequency of PLL  $(f_{pll})$  starts falling depicting the loss of synchronisation from the network. During the frequency fall the voltage instability occurs at  $v_{poc}$ . However, the voltage at  $v_{poc}$  is greater than that of  $v_f$  due to the presence of line-impedance. An envelope like pattern formed at  $v_{poc}$  is due to PLL instability [85] with respect to frequency fall.

#### 2.5. Loss of Synchronization during Symmetrical Faults

The  $v_f$  is still synchronised with 50 Hz, while  $v_{poc}$  is not this represents the im-685 pact of line-impedance during severe faults. It is worth mentioning that the active current is brought down to zero as per FRT strategy. This is the point where CM method fails to provide voltage stability leading to LOS. Only pure reactive current is injected the current angle ( $\theta_1$ ) is equivalent to 90°.

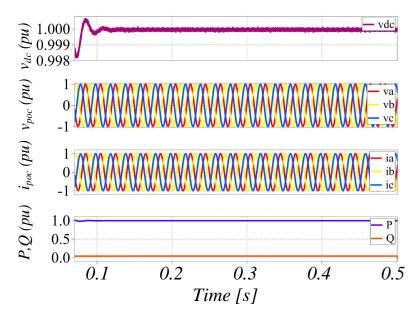

Figure 2.16: Synchronised to 50 Hz (No LOS)

Recent studies have shown that injection of adequate active current can avert 690 LOS. A similar case study is created, where the  $v_f$  is still equivalent to 0.035 pu during fault. The active current injection  $(i_d)$  is increased to avoid voltage and frequency instability as represented in Fig.2.17. The grid-current ( $i_{poc}$ ) is increased up to 1.35 pu for a short period of time. This case represents that injection of active current can avert LOS during severe faults. The current angle ( $\theta_1$ ) was found

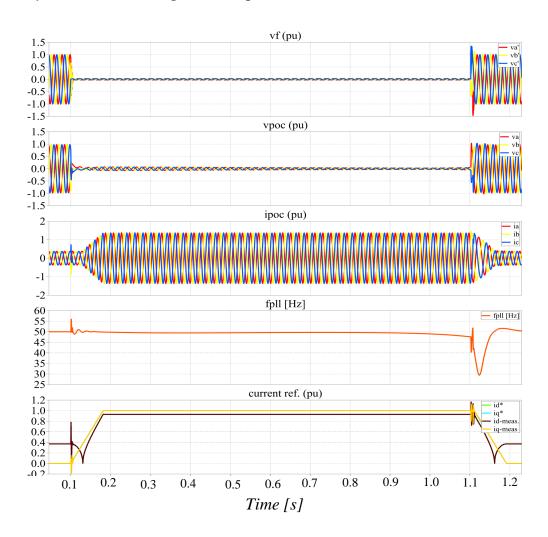

out to be 46.86° as high active current is injected. It is worth mentioning that for the presented case as in Fig.2.17 the system is synchronised to 50 Hz and no voltage instability would occur. This section can be concluded with the help of Fig.2.17 representing the physical understanding of LOS. It can be noticed that the LOS occurs only for the unit, while the main/rest grid continues to remain 700 synchronised at 50 Hz. Next section provides a clear overview of the active and reactive current transfer limits with respect to line impedance characteristics.

Figure 2.17: Physical understanding of LOS for single-unit

#### 2.6 Active and Reactive Current Transfer-limits during Symmetrical Faults

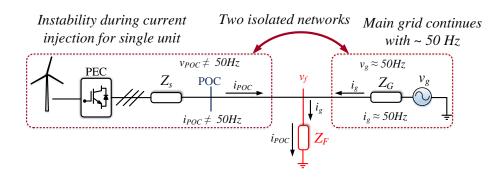

This section deals with the active and reactive transfer limits during severe symmetrical faults. The correlation between the sending end bus (POC) and receiving end bus  $(v_f)$  with respect to line impedance  $(Z_s)$  as a function of voltage magnitude will be discussed. The derived limits will provide a better understanding at which point does the LOS occurs. It should be noted that the impact of  $Z_s$  will be studied carefully as discussed in previous section. To avoid complexity POC will 710 be considered as  $v_s$  and  $v_f$  as  $v_r$ . Emphasize will not be given to the capacitance  $(C_s)$  considered for line impedance because it provides a couple of voltage boost. However, the variation of the derived limits due to capacitance can be considered as a part of future work.

#### 2.6.1 Power Flow on a line considering resistance

In this section power-flow for a line considering the line resistance and inductance will be discussed. Active  $(P_s)$  and reactive  $(Q_s)$  power flow equation can be derived as practised in [84]. This will be considered as the base case in this project.

#### 2.6. Active and Reactive Current Transfer-limits during Symmetrical Faults

$$P_s = \frac{v_s v_r X_s}{Z_s^2} sin\theta_s + \frac{v_s^2 R_s}{Z_s^2} - \frac{v_s v_r R_s cos\theta_v}{Z_s^2}$$

(2.11)

$$Q_s = \frac{v_s X_s}{Z_s^2} - \frac{v_s v_r X_s \cos\theta_v}{Z_s^2} - \frac{v_s v_r R_s \sin\theta_v}{Z_s^2}$$

(2.12)

Figure 2.18: Single line diagram for the resistive/inductive line tive/inductive line tive/inductive line

The derived equ.2.11 and 2.12 can be considered to understand the non-transferable active and reactive power during symmetrical faults. Considering a scenario where the  $v_r$  is equivalent to zero. So, the derived  $P_s$  and  $Q_s$  are represented as in equ.2.13.

$$v_r = 0 \Rightarrow P_s = \frac{v_s^2 R_s}{Z_s^2}; Q_s = \frac{v_s^2 X_s}{Z_s^2} \Rightarrow \frac{P_s}{Q_s} = \frac{R_s}{X_s}$$

(2.13)

It can noticed that when the  $v_r$  is zero the power from sending end will be dissipated in the form of active  $(i_{inj}^2 R_s)$  and reactive  $(i_{inj}^2 X_s)$  power losses of the line. However, when  $v_s > v_r$  a minimal amount of active power flow can be done to compensate for the losses arising due to reactive power flow. This statement is only valid for severe faults. In conclusion, the line impedance dictates the relationship between the  $v_s$  and  $v_r$ . This will help us understanding the active and reactive current transfer limits.

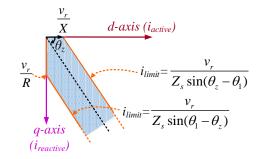

### 2.6.2 Current-Angle Characteristics

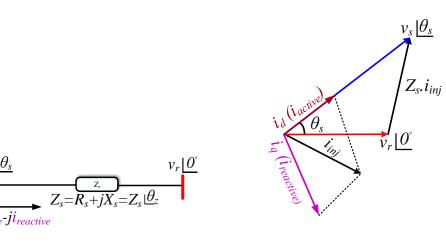

<sup>730</sup> The current injection defines the process to avert the LOS during severe faults. Active and reactive current transfer limits will be derived from equ.2.11 and equ.2.12. The derived equ.2.14 and equ.2.15 will form a base case scenario for deriving the current transfer limits. Considering the current flow from  $v_s$  to  $v_r$  with the considered line impedance the single-line diagram can be represented as

$$i_{active} = \frac{P_s}{v_s} = \frac{v_r X_s sin\theta_s}{Z_s^2} + \frac{v_s R_s}{Z_s^2} - \frac{v_r R_s cos\theta_v}{Z_s^2}$$

(2.14)

$$i_{reactive} = \frac{Q_s}{v_s} = \frac{v_s X_s}{Z_s^2} - \frac{v_s X_s cos\theta_s}{Z_s^2} - \frac{v_r R_s sin\theta_v}{Z_s^2}$$

(2.15)

tive/inductive line with current flow

Figure 2.20: Single line diagram for the resis- Figure 2.21: Phasor diagram for the resistive/inductive line with current flow

Considering a scenario for severe fault, where  $v_s > 0$  and  $v_r$  is equivalent to 735 zero. The  $i_{active}$  and  $i_{reactive}$  current can be obtained as in equ.2.16. It is worth mentioning that active and reactive current flowing creates losses on the resistance and reactance of the line. Under severe symmetrical faults when  $v_r$  is very low that means not equivalent to zero. This states that a fixed amount of active and reactive current injection is required depending upon  $\frac{X_s}{R_s}$  characteristics to avert the LOS. 740

$$v_r = 0 \Rightarrow i_{active} = \frac{v_s R_s}{Z_s^2}; i_{reactive} = \frac{v_s X_s}{Z_s^2} \Rightarrow \frac{i_{active}}{i_{reactive}} = \frac{R_s}{X_s}$$

(2.16)

The dependency of current transfer limits with  $\frac{X_s}{R_s}$  characteristics will be discussed further.

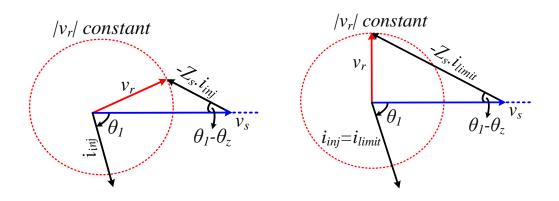

#### **Derivation of Current Transfer Limits** 2.6.3

Power-flow (power-angle) and current-angle characteristics were discussed in the above section. These sections were only limited to  $v_s$  and  $v_r$  with  $\frac{X_s}{R_s}$  characteristics. 745 It cannot provide the operating points for active and reactive current injection for low voltage magnitude. The single line diagram is represented as in Fig.2.22. The current phasor for the single line diagram is represented in Fig.2.22.

Figure 2.22: Single line diagram for derivation of current transfer limits

750

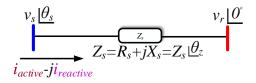

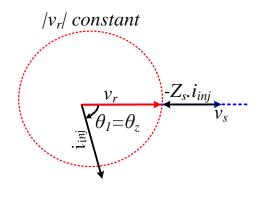

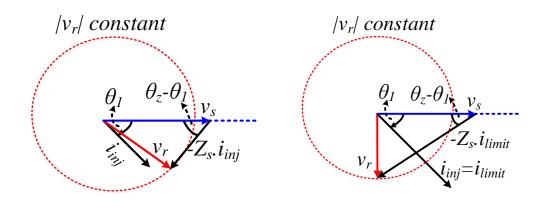

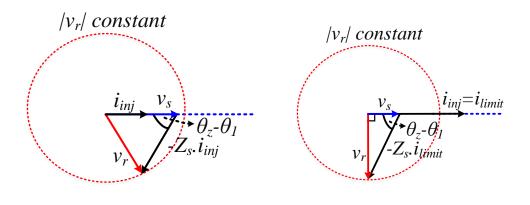

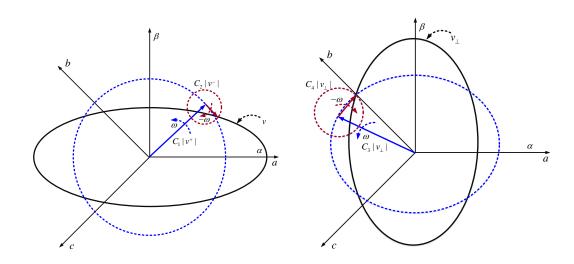

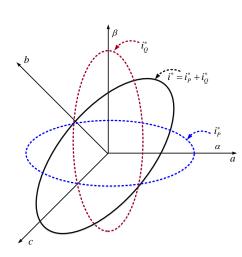

It is worth mentioning that when  $v_r$  drops to very low voltage the voltage and frequency instability occurs at the  $v_s$ . It is more important to analyse the converter active and reactive current injection limits at  $v_s$  because  $v_r$  remains stable. The current phasor methodology is represented in Fig.2.23 with  $i_d$  aligned to  $v_s$  on horizontal axis. The current angle  $\theta_1$  is the angle between the  $i_d$  and resultant vector  $i_{inj}$ . To analyse the current injection limits with respect to current-angle ( $\theta_1$ ).

<sup>755</sup> We consider that the  $v_r$  magnitude remains constant. The  $v_r$  can be found out by locating the tip of  $Zi_{inj}$  on the circle with  $v_s$  as reference axis. On the other hand the angle of  $v_s$  with respect to  $Zi_{inj}$  will be kept constant as  $\theta_1 - \theta_z$  knowing the fact magnitude of  $v_s$  is varied. It should be noted that impedance angle  $\theta_z$  is less than 90 degrees as it consists of resistive component. Further, to analyse the limits

<sup>760</sup>  $\theta_1$  will be varied from 0° to 360°.

**Figure 2.23:** Methodology to derive current phasor transfer limits

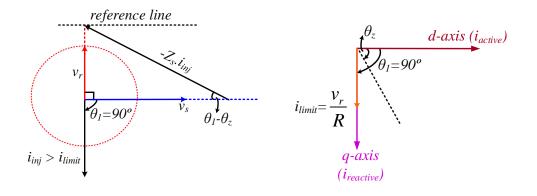

#### **Pure Reactive Current (** $\theta_1 = 90^\circ$ **)**

The methodology discussed in Fig.2.24 will be considered as base case scenario for all the derived limits. Initially, the reactive current injection starts considering the ramp rates with a low current magnitude as represented in Fig.2.25. The maximum reactive current injection is achieved that is  $i_{inj} = i_{limit}$  the angle between the  $v_s$  and

$v_r$  becomes 90° as represented in Fig.2.26. The vector  $Z_s i_{limit}$  is largest during this point considering the fact  $v_r$  is constant. It can be better explained with the help of Fig.2.27, if the magnitude of  $Z_s i_{inj}$  becomes greater than the limit the vector cannot be located between  $v_s$  and  $v_r$ . In order to achieve this situation a larger voltage magnitude  $v_r$  is required which is not possible. This states that if  $i_{inj}$  is greater 770 then the  $i_{limit}$  operating point cannot be located then it is just out of transfer limits.

**Figure 2.25:** Current transfer during pure reactive **Figure 2.26:** Current transfer limit at  $\theta_1 = 90^\circ$  current injection ( $\theta_1 = 90^\circ$ )

The current transfer limit can be derived as in equ.2.17. The derived limit can be represented in Fig.2.28

$$\theta_1 = 90^\circ \Rightarrow v_r = Z_s i_{limit} sin(\theta_1 - \theta_z) \Rightarrow i_{limit} = \frac{v_r}{R_s}$$

(2.17)

**Figure 2.27:** Out of transfer limits  $i_{inj} > i_{limit}$

#### 2.6. Active and Reactive Current Transfer-limits during Symmetrical Faults

The derived condition violated under severe symmetrical faults, when the receiving end voltage is very low. Only pure reactive current injection would lead to LOS.

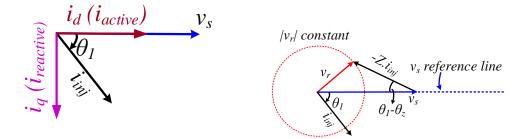

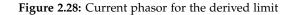

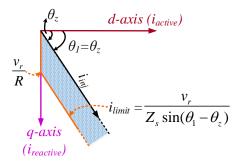

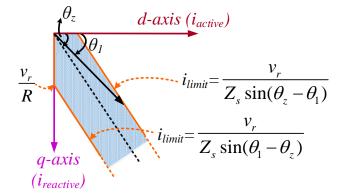

#### **Current magnitude limit** $90^{\circ} > \theta_1 > \theta_z$

780

This type of scenario is considered when active current is injected up to a certain limit to avoid LOS. The current magnitude is increased keeping  $\theta_1$  constant as represented in Fig.2.29. The point when  $i_{inj}$  is equivalent to  $i_{limit}$  that means largest current magnitude as represented in Fig.2.30  $v_s$  will be orthogonal to  $v_r$ . It is worth mentioning that the  $i_{limit}$  cannot be greater than the  $i_{inj}$  the operating point cannot be located.

**Figure 2.29:** Current transfer  $90^{\circ} > \theta_1 > \theta_z$  **Figure 2.30:** Cur

**Figure 2.30:** Current transfer limit  $90^{\circ} > \theta_1 > \theta_2$

The current transfer limit for this case can be derived as in equ.2.18.

$$90^{\circ} > \theta_1 > \theta_z \Rightarrow v_r = Z_s i_{limit} sin(\theta_1 - \theta_z) \Rightarrow i_{limit} = \frac{v_r}{Z_s sin(\theta_1 - \theta_z)}$$

(2.18)

785

The derived limit can be represented as in Fig.2.31. The blue shaded area represents the operating point. The orange line denotes the  $i_{limit}$  from the derived expression.

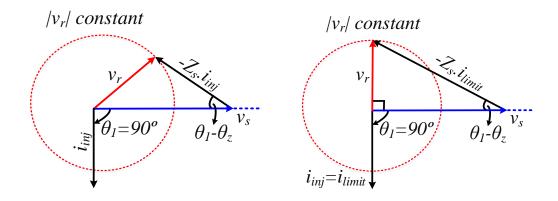

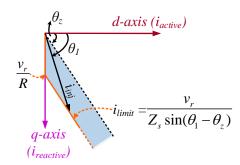

#### Current magnitude limit $\theta_1 = \theta_z$

790

This scenario is less likely to occur when the current angle  $(\theta_1)$  is equivalent to line impedance angle  $(\theta_z)$  as represented in Fig.2.32. This scenario does not have a current transfer limit but an operating point. If the current magnitude  $(i_{inj})$  is increased then the magnitude of  $v_s$  is also increased but cannot be increased due

**Figure 2.31:** Current phasor for the derived limit ( $90^{\circ} > \theta_1 > \theta_2$ )

to voltage limitations on  $v_s$ . It also depends upon converter current limitation to avoid undesirable trip. The derived limit is represented as in Fig2.33.

**Figure 2.32:** Current transfer  $\theta_1 = \theta_z$

**Figure 2.33:** Derived limit for  $\theta_1 = \theta_2$

#### **Current magnitude limit** $\theta_z > \theta_1 > 0^\circ$