# 2-Dimensional Control of VSC-HVDC

Master Thesis Magnus Svean, Astrid Thoen

Aalborg University Department of Energy Technology

Copyright © Aalborg University 2018

Title:2-ISemester:10°Semester theme:MaProject period:02ECTS:30Supervisor:FilProject group:EF

2-Dimensional Control of HVDC 10th Master Thesis 02.02.18 to 01.06.18 30 Filipe Faria da Silva EPSH4-1032

Astrid Thoen

Magnus Svean

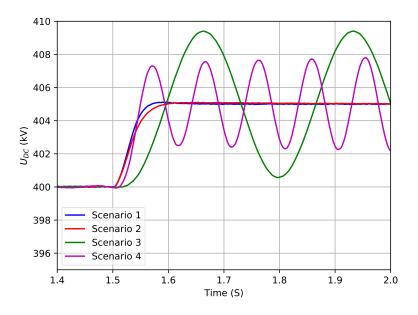

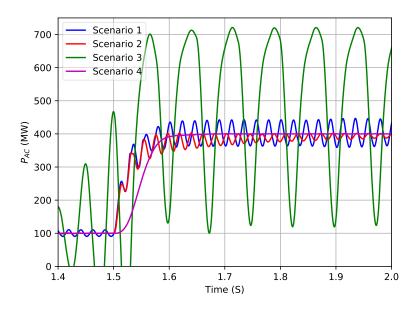

Pages, total including appendix: 119 Appendix: 13 structure is was observed that when performing an uncontrolled switching between control modes in the 1-D control structure, transients would be present. This thesis had the objective of developing a 2-D upper level control structure without a switch between the control modes to achieve a seamless switching. To evaluate the performance, the 2-D controller were compared with the 1-D controllers response as a reference. Tests showed that for PtP-HVDC and 3-terminal HVDC, the 2-D controller were able to achieve a seamless switching for all cases with negligible oscillation. Other factors observed was that 2-D in some cases had a slower response, but at the same time containing less transients in its response.

In a conventional VSC-HVDC control

By accepting the request from the fellow student who uploads the study group's project report in Digital Exam System, you confirm that all group members have participated in the project work, and thereby all members are collectively liable for the contents of the report. Furthermore, all group members confirm that the report does not include plagiarism.

# Preface

The Master Thesis concludes the 4th semester of the M.Sc. in Electrical Power Systems and High Voltage Engineering at the Department of Energy Technology at Aalborg University. The Thesis was conducted in the period from February 2nd to June 1st 2018. The project concerns Testing and design of a new upper level control structure for the voltage source converter for a Point-to-Pint and a 3-treminal multi terminal HVDC system

## Acknowledgement

We would like to give credit to several people who were involved during the MSc thesis which were providing feedback in the form of supervisor meetings, helping and leading us in the right direction towards completion of the thesis. We would like to acknowledge Aalborg University and the Energy Department. We would like to express our gratitude to our supervisors Fillipe f. da silva and Roni Irnawan For giving us the opportunity to explore the field within HVDC technologies and power systems We would like to thank them for their advice and guidance despite their often tight time schedule and we appreciate the regular follow up during throughout the thesis.

# Abbrevation

| Index       | Description                                |

|-------------|--------------------------------------------|

| 1-D Control | 1-dimensional upper level control scheme   |

| 2-D Control | Two-dimensional upper level control scheme |

| Bm          | Bus-bar                                    |

| Cm-A1       | Converter station                          |

| Cm-C1       | Converter station                          |

| Cm- $B2$    | Converter station                          |

| Cm- $B3$    | Converter station                          |

| Cm- $F1$    | Converter station                          |

| DCS1        | Test system developed by Cigre             |

| DCS2        | Test system developed by Cigre             |

| HVAC        | High voltage alternating current           |

| HVDC        | High voltage direct current                |

| IGBT        | Insulated Gate Bipolar Transistor          |

| LCC         | Line commutated converter                  |

| MTDC        | Multi-terminal HVDC                        |

| MMC         | Multi-Level Modular Converter              |

| NLC         | Nearest level control                      |

| OWF         | Offshore wind farm                         |

| PCC         | Point of Common Coupling                   |

| PLL         | Phase lock loop                            |

| PtP         | Point-to-Point                             |

| PWM         | Pulse Width Modulation                     |

| RES         | Renewable Energy Sources                   |

| SPWM        | Sinusoidal PWM                             |

| SM          | Sub-Module                                 |

| VSC         | Voltage Source Converter                   |

| Symbol         | Description                          | Notation                    |

|----------------|--------------------------------------|-----------------------------|

| $\alpha$       | alpha                                | -                           |

| $\beta$        | beta                                 | -                           |

| $1/k_v$        | Droop slope                          | $\frac{\Delta P}{\Delta V}$ |

| $C_{cell}$     | Cell capacitance                     | F                           |

| d              | delta                                | -                           |

| $e_t$          | Error in a function of time          | -                           |

| $rac{e_t}{f}$ | Space vector                         | -                           |

| f              | frequency                            | Hz                          |

| $f_s$          | switching frequency                  | Hz                          |

| $K_v$          | Droop constant                       | $\frac{kV}{MW}$             |

| $K_i$          | Integral gain                        | -                           |

| $K_p$          | Proportional gain                    | -                           |

| $T_i$          | Reset time                           |                             |

| $L_{arm}$      | Arm inductance                       | Н                           |

| I, i           | Current                              | А                           |

| $m_a$          | Amplitude modulation                 | -                           |

| $N_{SM}$       | Number of sub modules in a converter | -                           |

| $P_{ac}$       | Active power                         | W                           |

| $P^*$          | Power reference                      | MW                          |

| $Q_{ac}$       | Reactive power                       | VAr                         |

| R              | Resistance                           | Ω                           |

| $S_{MMC}$      | Apparent power of the converter      | -                           |

| t              | Time                                 | 8                           |

| $V_{dc}$       | DC Voltage                           | V                           |

| $V_{ac}$       | AC Voltage                           | V                           |

| $V^*$          | Reference voltage                    | V                           |

| $V_s$          | Voltage potential AC terminal        | -                           |

| $V_d$          | DC leg voltage                       | -                           |

| $V_{cell}$     | Cell voltage signal                  | -                           |

| $v_{tri}$      | Triangular voltage signal            | -                           |

| $v_{control}$  | sinusoidal signal                    | -                           |

| $V_c$          | Capacitor voltage                    | -                           |

| $V_{SM}$       | Sub module voltage                   | -                           |

# Summary

The increased focus on limiting global warming and wish to reduce greenhouse gas emissions have led to an increased focus on renewable energy sources (RES)[1]. Offshore wind farms are one of these RES. Offshore wind power implies long distance transmission of power, where HVDC has been proven to be the most beneficial technology [2, 3]. The voltage source converter technology (VSC) is the best option when wanting to transmit power from an OWF over a long distance [4, 4, 5]. VSC-based HVDC implies the use of a modularmultilevel converter (MMC) technology. The upper level control structure which is most often used in VSC-HVDC transmission is the current vector control. The current vector control strategy use reference frame transformation to change three phase AC systems into two constant DC signals.

The control structure of the conventional upper level control [6] consists of four loops divided into the d-axis ( $V_{dc}$ ,  $P_{ac}$  loops), and q-axis loop ( $V_{ac}$  and  $Q_{ac}$  loops) control. In some situations it could be necessary for the system operator to switch the control mode from for example  $V_{dc}$  to  $P_{ac}$  control. An uncontrolled switching between these control loops cause transients in the system. The main goal for this thesis is therefore to propose a new upper level control scheme based on a 2-dimensional structure, (referred to as the 2-D controller). The 2-D upper level control strategy is based on making  $V_{dc}$  and  $P_{ac}$  in the d-axis and  $V_{ac}$ and  $Q_{ac}$  in the q-axis dependent on each other. The four loops in the conventional upper level control scheme (from now referred to as the 1-D control scheme) is therefore reduced from four to two loops. Each loop will consist of only one PI controller, hence tuning will be needed to find proposed gains. The operation of the 2-D controller will be compared to the 1-D controller to validate its performance.

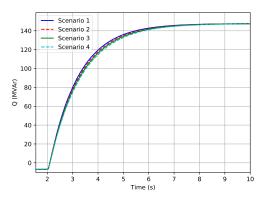

The d-axis and q-axis control loops in the 1-D and 2-D controller were evaluated for different test cases when only one converter was connected to an ideal voltage source or open terminals. The test cases investigated the response of the 2-D controller when applying a step, droop control and how the controller worked to keep the limits set in the controller. The results from the test cases validated that the 2-D controller upper level scheme worked correctly, while at the same time finding advantages and drawbacks of the two control strategies.

To validate that the 2-D controller could operate in a more realistic scenario, it was tested in a PtP HVDC link and in a 3-terminal MTDC system. Some of the different test cases were seamless switching and fault analysis. The results showed that the 2-D controller will be able to perform seamless switching both in a PtP-HVDC link and a 3-terminal MTDC system. Other factors observed was that the 2-D controller in some cases had a slower response than the 1-D, but at the same time the 2-D controller has less transients in the response. The 2-D controller with the proposed tuning gains showed a good performance of keeping the limits set in the controller during a fault.

# Contents

| 1                                                                   | Intr                    | Introduction   |                                                                    |                 |  |

|---------------------------------------------------------------------|-------------------------|----------------|--------------------------------------------------------------------|-----------------|--|

|                                                                     | 1.1 VSC-HVDC Technology |                |                                                                    | 2               |  |

|                                                                     | 1.2                     | Scope          | of Work                                                            | 4               |  |

|                                                                     |                         | 1.2.1          | Main Objectives                                                    | 8               |  |

|                                                                     | 1.3                     | Limita         | ations                                                             | 8               |  |

| <b>2</b>                                                            | Тор                     | ology          | and Operation of the Voltage Source Converter                      | 9               |  |

|                                                                     | 2.1                     |                | Converter                                                          | 9               |  |

|                                                                     |                         | 2.1.1          | Sinusoidal Pulse Width Modulation                                  | 11              |  |

|                                                                     | 2.2                     | Topolo         | bgy and Operation of the Half-Bridge MMC                           | 12              |  |

|                                                                     |                         | 2.2.1          | Nearest Level Control                                              | 14              |  |

| 3                                                                   | Svet                    | tom an         | nd Control of VSC-HVDC Systems                                     | 17              |  |

| J                                                                   | 3.1                     |                | ol of VSC-HVDC systems                                             | 17              |  |

|                                                                     | 0.1                     | 3.1.1          | Upper Level Control                                                | 18              |  |

|                                                                     | 3.2                     |                | at Vector Control                                                  | 20              |  |

|                                                                     | 0.2                     | 3.2.1          | Clarks Transformation                                              | $\frac{20}{22}$ |  |

|                                                                     |                         | 3.2.1<br>3.2.2 | Parks Transformation                                               | 22              |  |

|                                                                     | 3.3                     | 0              | ntroller                                                           | $\frac{23}{24}$ |  |

|                                                                     | 0.0                     | 3.3.1          | PI Controller Tuning                                               | $\frac{24}{25}$ |  |

|                                                                     |                         | 3.3.2          | Evaluation of a 2.Order System                                     | $\frac{25}{25}$ |  |

|                                                                     |                         | 3.3.2<br>3.3.3 | Controller Tuning of the DC Voltage Loop                           | $\frac{25}{27}$ |  |

|                                                                     |                         | 3.3.4          | Controller Tuning of AC Power Loop                                 | $\frac{21}{28}$ |  |

|                                                                     |                         | 3.3.4          | Integrator Wind-up                                                 | $\frac{20}{30}$ |  |

|                                                                     | 3.4                     |                | re Control Methods                                                 | $\frac{30}{31}$ |  |

|                                                                     | 0.4                     | 3.4.1          | ·                                                                  | 31<br>31        |  |

|                                                                     |                         | 3.4.1<br>3.4.2 | Master-Slave Strategy       DC Voltage Droop Control               | 31<br>31        |  |

|                                                                     |                         | 3.4.2<br>3.4.3 | AC Voltage Droop Control                                           | 33              |  |

|                                                                     |                         | 0.4.0          |                                                                    | 55              |  |

| 4 Design, Test and Validation of the 2-D Upper Level Control Scheme |                         | <b>35</b>      |                                                                    |                 |  |

|                                                                     | 4.1                     | 2-D U          | -D Upper Level Control Structure                                   |                 |  |

|                                                                     |                         | 4.1.1          | Design of the 2-D Error Block                                      | 37              |  |

|                                                                     |                         | 4.1.2          | Comparison of the Calculation Method in the 1-D And 2-D Controller | 41              |  |

#### Contents

|   | 4.2            | 0       |                                                                                                                          |     |

|---|----------------|---------|--------------------------------------------------------------------------------------------------------------------------|-----|

|   | 4.3            | Valida  | tion of the d-axis Control Loop                                                                                          | 43  |

|   |                | 4.3.1   | Response Comparison of The Controllers in the d-axis loop                                                                | 43  |

|   |                | 4.3.2   | Evaluation of Tuning Parameters for the d-axis Control Loop                                                              | 45  |

|   |                | 4.3.3   | Trial and Error Procedure to Find Proposed Tuning Parameters For                                                         |     |

|   |                |         | The PI Controller In The d-axis Control Loop                                                                             | 47  |

|   |                | 4.3.4   | Validation of the Proposed Tuning Parameters                                                                             | 52  |

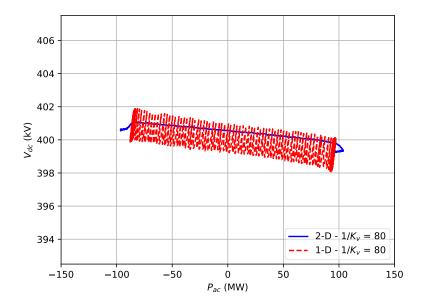

|   |                | 4.3.5   | Evaluation of the Response when Operating in Droop Control                                                               | 54  |

|   |                | 4.3.6   | Validation of The Voltage and Power Limits for the 2-D Controller                                                        | 58  |

|   | 4.4            | Valida  | tion of the q-axis Control Loop                                                                                          | 61  |

|   |                | 4.4.1   | Adapting The AC Grid To q-axis Simulations By Calculating Different<br>Short Circuit Ratios                              | 61  |

|   |                | 4.4.2   | Changing The Control Structure of the 1-D Controller q-axis Loop To<br>Be Comparable With The 2-D Controller q-axis Loop | 62  |

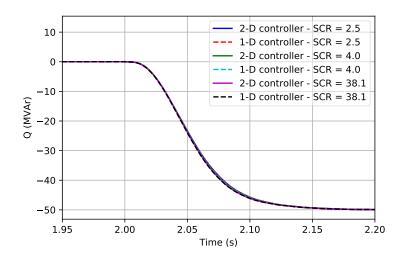

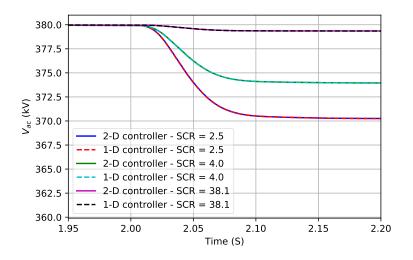

|   |                | 4.4.3   | Response Comparison of the Controllers in the q-axis Loop                                                                | 63  |

|   |                | 4.4.4   | Trial and Error Using Different Ti to Optimize the Response for a AC Droop Control                                       | 66  |

|   |                | 4.4.5   | Droop Control Comparison of the 1-D and 2-D Controllers for the q-<br>axis Control Loop                                  | 68  |

|   |                | 4.4.6   | Reactive Power and AC voltage Limit Comparison of the 1-D and 2-D Control                                                | 71  |

|   |                |         |                                                                                                                          |     |

| 5 | $\mathbf{Res}$ |         | om Testing the 2-D controller in a PtP and MTDC System                                                                   | 75  |

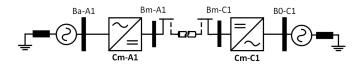

|   | 5.1            |         | ess Switching of d-axis Control Loop in a PtP-HVDC System                                                                | 76  |

|   | 5.2            | Fault . | Analysis of PtP-HVDC link                                                                                                | 79  |

|   |                | 5.2.1   | 3-Phase to Ground Fault on Ba-A1                                                                                         | 80  |

|   |                | 5.2.2   | 3-phase to Ground Fault Applied at B0-C1                                                                                 | 83  |

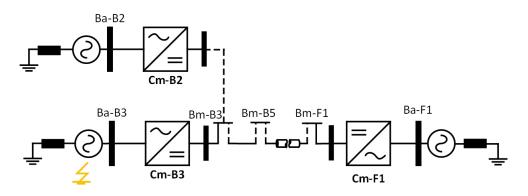

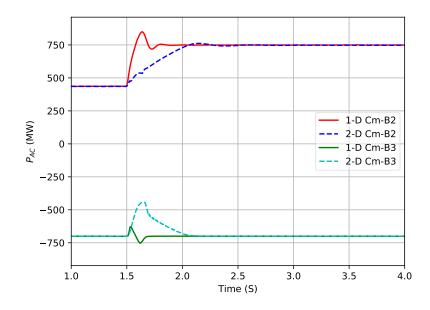

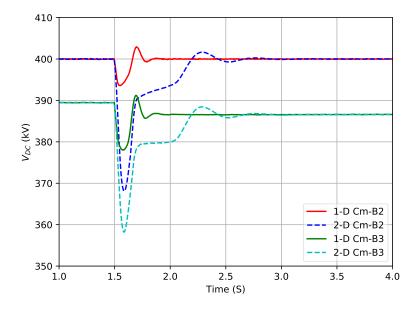

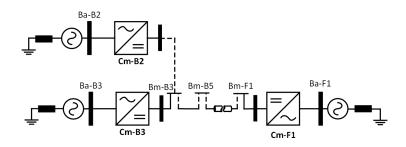

|   | 5.3            |         | Control Comparison Between the Controllers in a MTDC system $\ . \ . \ .$                                                | 85  |

|   |                | 5.3.1   | Switching Between Control Modes in a 3-terminal MTDC System $~$                                                          | 88  |

|   | 5.4            | Fault . | Analysis of 3-Terminal MTDC System                                                                                       | 90  |

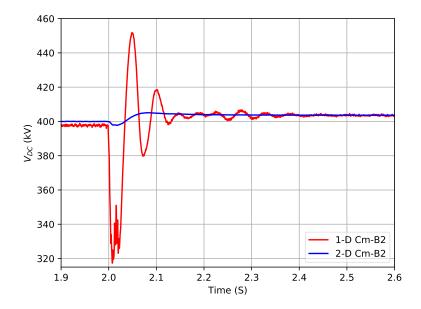

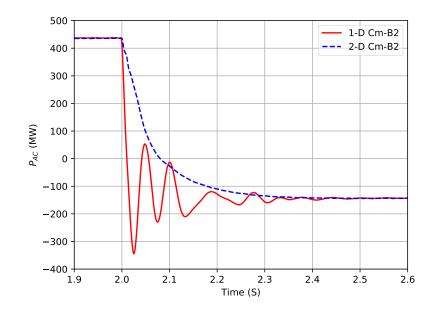

|   |                | 5.4.1   | 3-Phase to Ground Fault Applied at Ba-B3 to Cause an Outage of Cm-B3                                                     | 91  |

|   |                | 5.4.2   | Permanent Fault Applied at Bm-F1 with Cm-B2 and Cm-B3 in Droop<br>Control                                                | 93  |

| 6 | Cor            | clusio  | n                                                                                                                        | 99  |

| U | 6.1            |         | Work                                                                                                                     | 102 |

|   | 0.1            | rutur   | WOIK                                                                                                                     | 102 |

| A | -              |         | esign and Theory                                                                                                         | 103 |

|   | A.1            |         | num Voltage                                                                                                              | 103 |

|   | A.2            |         | n Parameters                                                                                                             | 103 |

|   | A.3            |         | ior of the reference line during a step                                                                                  | 104 |

|   | A.4            |         | nining the Tuning Procedure for the Proposed Tuning Gains                                                                | 105 |

|   | A.5            | Test S  | ystems                                                                                                                   | 106 |

|   | A.6            | System  | n Design                                                                                                                 | 106 |

х

|              |     | A.6.1                            | Droop slope                                                         | 106 |

|--------------|-----|----------------------------------|---------------------------------------------------------------------|-----|

|              |     | A.6.2                            | q-axis Control Loop                                                 | 107 |

|              |     | A.6.3                            | Trial and error tuning for the q-axis loop                          | 108 |

| в            | Cal | culatio                          | ns                                                                  | 109 |

|              | B.1 | Calcul                           | ating the Error                                                     | 109 |

|              |     | nentation of Errorblock in PSCAD | 110                                                                 |     |

|              |     | B.2.1                            | Script in FORTRAN                                                   | 111 |

|              | B.3 | DC Re                            | esistance Calculation                                               | 112 |

|              |     | B.3.1                            | SCR for the CIGRE test system                                       | 112 |

|              |     | B.3.2                            | Transforming an equivalent network to match a weak grid             | 114 |

|              |     | B.3.3                            | Transforming an equivalent network to match an almost strong grid . | 115 |

|              |     | B.3.4                            | SCR ratios for different AC grids                                   | 115 |

| References 1 |     |                                  |                                                                     |     |

# Chapter 1 Introduction

Due to the worlds increased focus on limiting global warming and wanting to reduce the amount of green house gas (GHG) emissions, more attention has been drawn to the development and use of renewable energy sources (RES) [1]. Wind energy technology is currently one of the leading RES technologies due to its mature technology and large scale of wind resources. According to [7] the wind power penetration level is only expected to increase in the future making it an important renewable energy resource for the world. Most of the wind farms existing today are placed onshore, but due to good wind conditions, small impacts on the environment and a reduction of construction costs at offshore locations, it is wanted to increase the amount of offshore wind farms (OWFs) in the future [7]. Both the size of the wind farms and the distance to the shore is expected to increase. This implies the importance of investigating in technology for transmission and control of bulk power transmitted over longer distances from large OWFs.

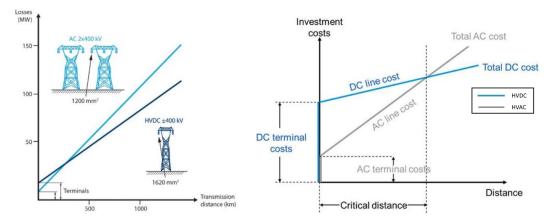

The two alternatives for transmission of power are HVAC and HVDC technology. A comparison between these technologies are depicted in Figure 1.1.

**Figure 1.1:** The figure to the left shows a comparison of the losses between HVAC and HVDC. The figure to the right depicts the cost comparison between HVDC and HVAC [8]

The figure to the left shows losses plotted against transmission distance. It can be observed that for longer distances after a certain break-even distance, HVDC will have lower power losses than HVAC. This implement that HVDC is the most cost efficient solution for transferring power over distance that is greater than the break-even distance[2]. The figure to the right shows that HVDC has higher converter station investment costs than HVAC. [3] states that the onshore converter station costs for a 1000 MW VSC-HVDC system is 110 M $\in$ . As a comparison the HVAC onshore converter station with the same power rating costs 28 M $\in$ . Despite the higher investment costs for HVDC it can be seen that above a certain distance, "break-even distance", HVDC will have lower losses and total costs, hence giving it being the most feasible economical option for a long distance high voltage transmission [2].

Other advantages are that HVDC does not have problems with reactive power compensation. In HVAC cables the reactive power needs to be compensated due to the high capacitance in the cables. The need for reactive power compensation limits the maximum length of the power cable, hence the transmission distance. HVDC inherit the possibility for asynchronous connection of AC grids with different magnitude and/or frequency, as-well as an easier control of active power in the system [2]. As a small conclusion, the most efficient and economical way of transmitting large amount of energy over long distances is by using HVDC technology.

## 1.1 VSC-HVDC Technology

Nowadays HVDC links can be implemented as either VSC-HVDC or LCC-HVDC also known as HVDC-classic. The HVDC-classic is based on thyristor technology and is widely used across the world for distributing bulk of power. The LCC-HVDC technology has some drawbacks regarding that black-start capability and connection to weak offshore grids becomes difficult. The LCC technology needs to be connected to a strong AC grid since converters require a stable commutation voltage across its thyristors which limits HVDC-classic to onshore power-transmission. The limitations of HVDC-classic makes placement of offshore converters impossible. Another factor is that the size of the offshore converter station is large and it weighs a lot which is not good in cooperation with offshore placement, hence leading to a high economical expense[4, 4, 5].

Regarding VSC-HVDC, the first commercial VSC-HVDC project was commissioned in Gotland, Sweden in the year of 1999[9]. Since then, there have been a big development in projects including the VSC strategy. VSC-HVDC is based on the use of self-commutating switches (often IGBT technology). In a VSC, the DC voltage polarity is kept constant and it is the polarity of the DC current that changes the direction of the power flow. It uses pulse width modulation (PWM) techniques in order to control the gate switching frequency of the IGBT [10]. VSC-HVDC also allows for independent control of reactive and active power.

Until recently, the 2-level converter was most commonly used for VSC-HVDC, but with advances in power electronics technology the modular multilevel converter (MMC) structure has gained more and more attention. These two converter types will be explained more in detail in chapter 2.

The main advantages of using VSC-HVDC compared to the classic-HVDC technology are according to [11, 12]:

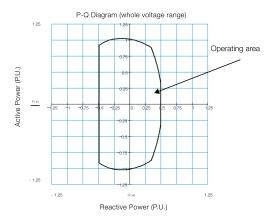

• The possibility to have independent control of active  $(P_{ac})$  and reactive power  $(Q_{ac})$

- Control of the voltage in the AC voltage while the transmitted active power is kept constant, improves power quality

- The instant reversal of power flow happens because of a reversal in DC current direction and not the DC voltage polarity. This allows for using XLPE cables.

- Black-start capability, VSC-HVDC has the ability of operating a no-load condition (i.e no current is flowing) to restore power to a AC network.

- Better suited for multi-terminal connection

- Smaller footprint of converter stations (better suited for offshore wind-farms) i.e less harmonic content in the AC waveform leading to less filtering to obtain a close to sinusoidal AC waveform.

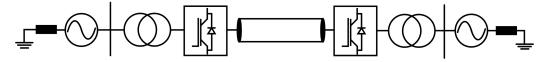

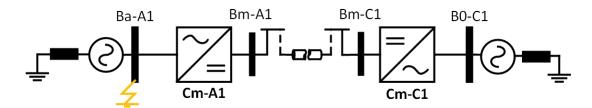

Figure 1.2 depicts a generic point-to-point (PtP) configuration of a VSC-HVDC link. As it can be seen the VSC-HVDC consists of two VSC stations and a DC cable connection consisting of 1 or more lines for power transmission. Both converters are connected to equivalent AC grids. The DC side of the converter has a capacitor which stabilizes the DC voltage. The size of the capacitor is reduced when a higher switching frequency is applied. The phase reactor stabilizes the AC current and also reduces the harmonic components in the current, which occurs because of the converter switching. The configuration of the HVDC link is a symmetric monopole. In a symmetric monopole configuration the grounding is placed in between the two lines of transmission so that no DC current flows trough ground.

Figure 1.2: PtP-Configuration of two equivalent grids trough a VSC-HVDC transmission system [1]

In order to have a functioning HVDC system one converter has to operate in rectifiermode and one in inverter-mode. During normal conditions both converter stations control active and reactive power independent of the other converter station. But still the active power in the DC cables has to be balanced, hence the active power entering the HVDC link has to be the same as the output power (neglecting power losses). To have this power balance one of the stations have to control the DC voltage  $V_{dc}$ , while the other one controls the active power  $P_{ac}$  [13]. To maintain the voltage amplitude in the adjacent grid, reactive power ( $Q_{ac}$ )- and AC voltage ( $V_{ac}$ ) control is used to support the grid.

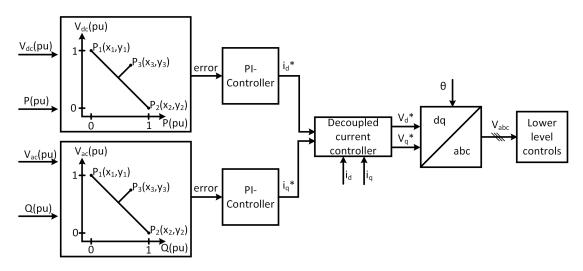

The performance of the VSC-HVDC system does not only rely on the efficiency of the converters but also on how the system is controlled. The control mode used for VSC-HVDC is often the current vector control. The current vector control strategy uses reference frame transformation to change three phase AC systems into constant two phase DC signals. It has two control loops upper level control loop, and the lower level control loop. The upper level control loop consists of four control loops controlling active power, DC voltage, AC voltage and reactive power. The upper level control is responsible for sending a current reference to the lower level control loop. The lower level control, manages the switching states of the converters and monitors the voltage reference of the grid[14].

As stated in [6] the upper level control can either be connected to an AC system with active synchronous generation known as a non-islanded system, or it can be connected to an isolated or weak AC system known as an islanded system. This thesis will consider a non-islanded connection of the upper level control. The main objective will be to optimize the upper level controls for the control scheme of the VSC-HVDC system.

When VSC-HVDC is used to distribute power to other converters present in the DC grid, a control which can control a constant voltage-, constant power or a droop control can be enforced to the onshore converters to provide the necessary amount of power to ensure a stable voltage at the DC side and at the same time ensuring a stable voltage and power-factor(PF) at the AC side where the HVDC link is connected. Converter stations which has this type of controls are usually onshore converters (i.e converters that are connected a larger area). For offshore converter stations used to connect OWFs to the HVDC grid, control-schemes are not used due to that it is wanted to transmit all of its power production to the grid.

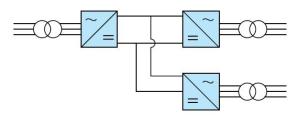

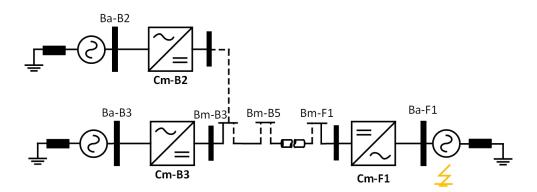

Nowadays, an increasing number of VSC-HVDC links are planned or already in operation. The feasibility of connecting planned HVDC links to existing HVDC links, which naturally is transformed to a multi-terminal HVDC grid (MTDC). The objective the MTDC network is to create secure an efficient interconnection of several HVDC links in the near future, participating in a gradual DC grid development. A MTDC system consists of either three or more terminals. Figure 1.3 shows the configuration of a 3-terminal symmetric monopole MTDC system.

Figure 1.3: 3-terminal MTDC system based on symmetric monopole configuration [15]

The control of the MTDC grid should ensure that the DC grid is strong and reliable and also that it can support its connected AC grids properly. If a fault occurs in a MTDC grid, the part where the fault happens will be isolated and the power flow will instead be directed through the healthy DC grid [16].

Examples of MTDC systems that have been proven feasible are the 3-terminal system between Corsica (France) and Sardinia (Italy), and the Quebec - New England 3-terminal system which is located onshore between Canada and USA [10].

## 1.2 Scope of Work

The scope of this thesis is to design a 2-dimensional (2-D) controller for use in VSC-HVDC networks. The study in this thesis will use a power system software named PSCAD/EMTDC. The CIGRE B4 test group have designed a PtP HVDC link model (DCS1) and a 4-terminal MTDC system (DCS2). The configuration of the upper level control scheme used in the

mentioned test systems developed by CIGRE can be found in [6]. The upper level control scheme will be used as a reference for simulations this thesis. For convenience it will be referred to as the 1-D controller due to its 1-dimensional configuration.

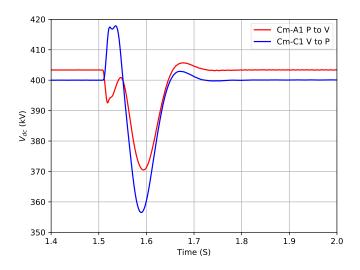

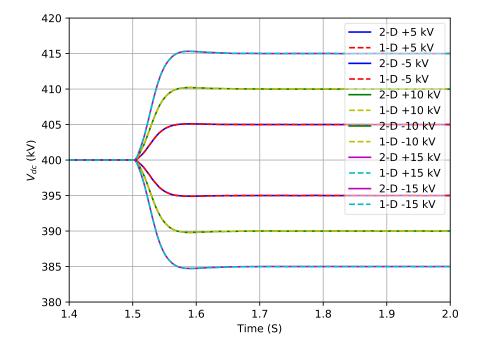

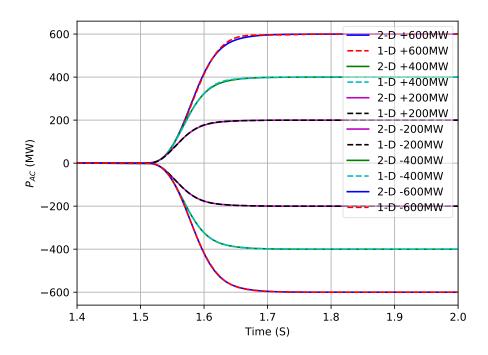

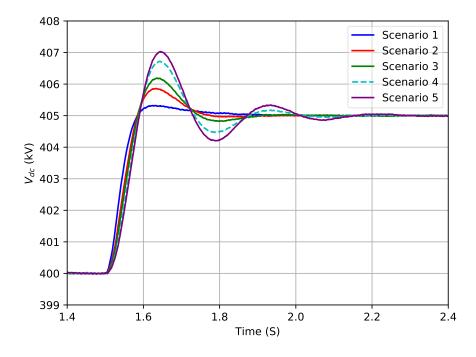

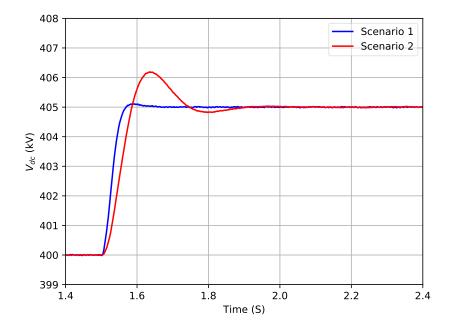

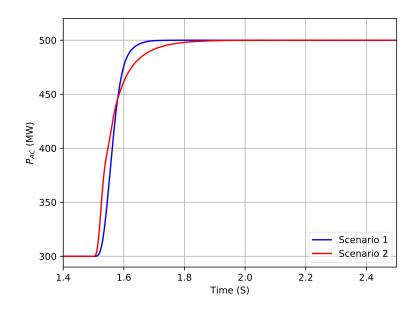

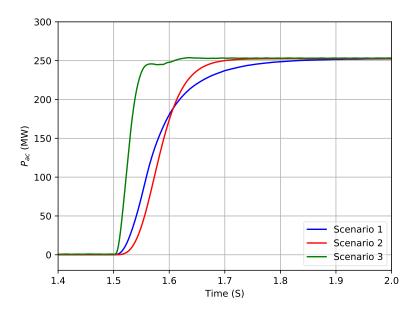

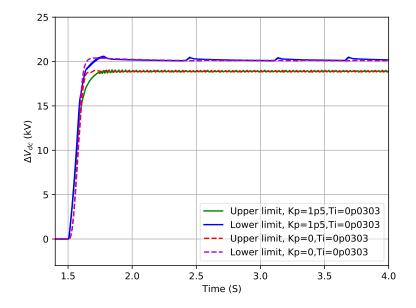

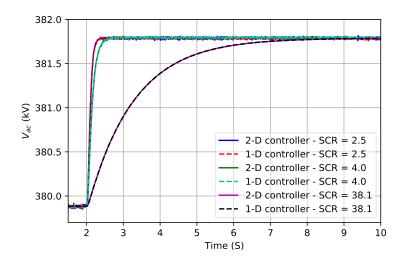

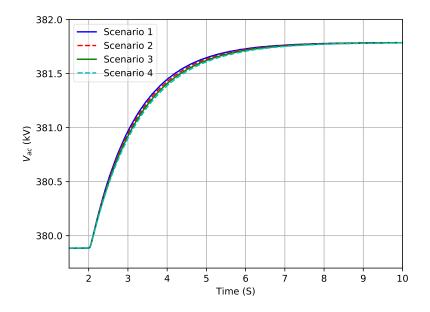

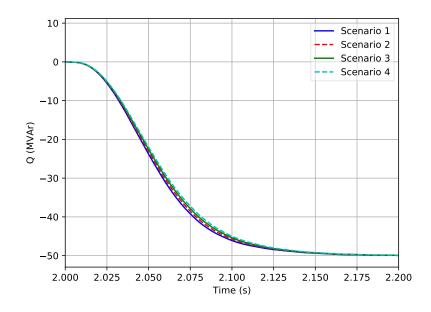

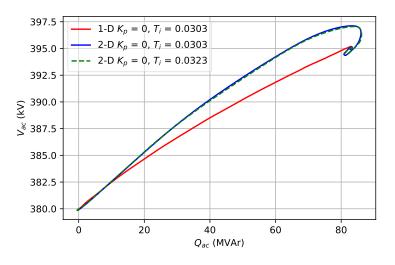

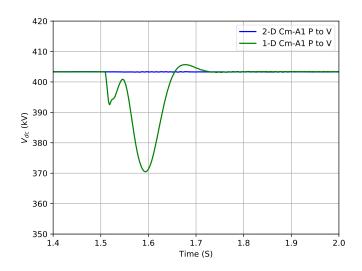

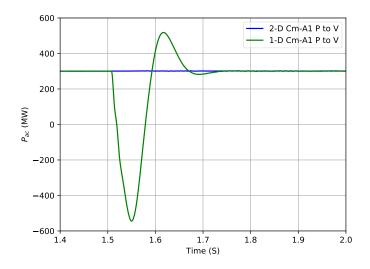

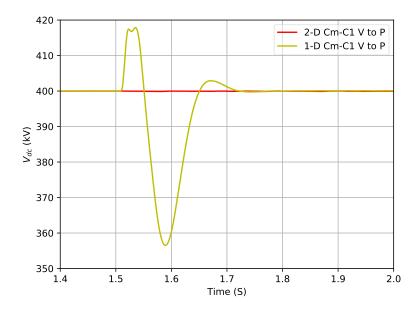

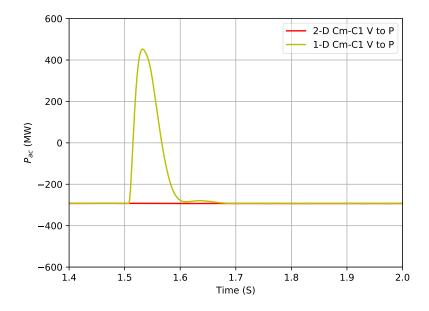

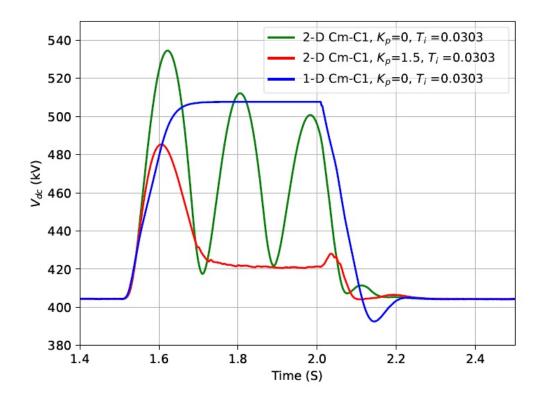

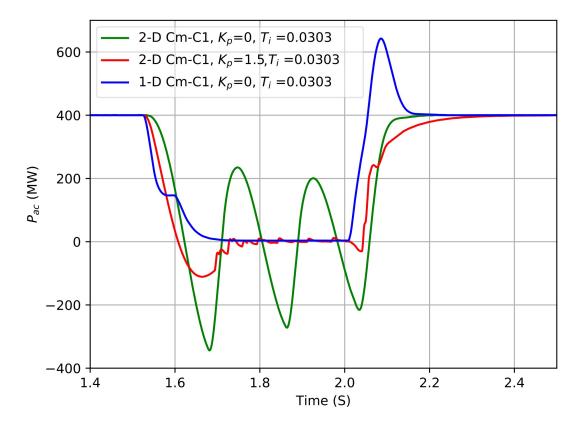

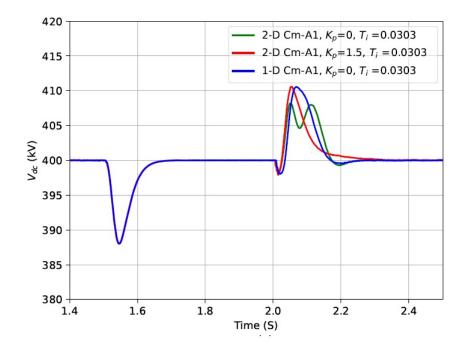

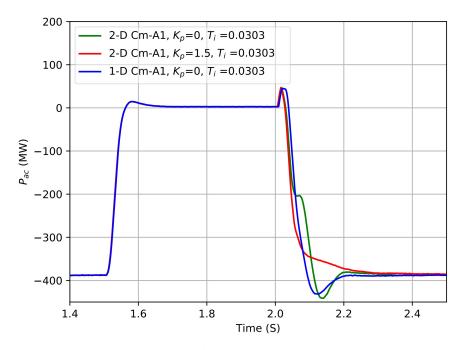

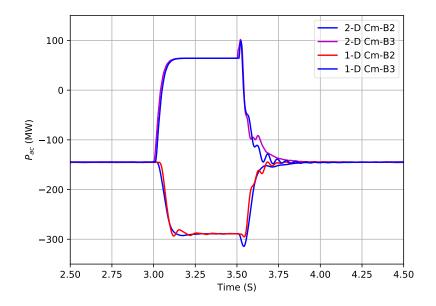

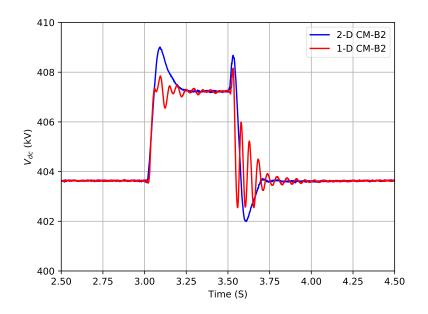

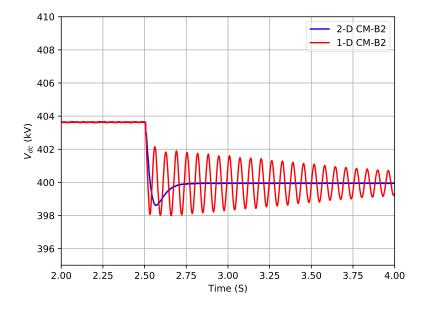

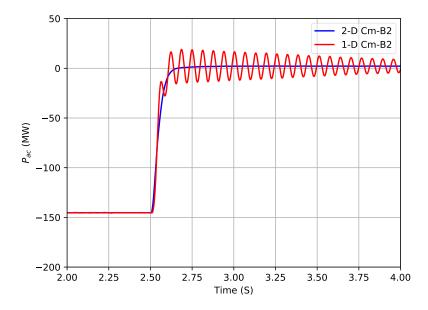

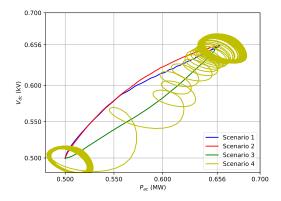

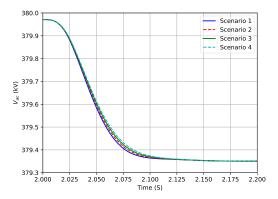

The upper level control of the DCS1 and DCS2 test systems are based on a current vector control scheme. In the upper level control configuration of that a switch is needed to change the control state between  $P_{ac}$  control and  $V_{dc}$  control, as well as between  $Q_{ac}$  control and  $V_{ac}$  control. The problem with conducting an uncontrolled switching between the control loops is that it cause transients in the system. A simulation showing the transients during an uncontrolled switching can be seen in Figure 1.4. The simulation was performed by switching converter Cm-A1 from  $P_{ac}$  to  $V_{dc}$  control, and the converter Cm-C1 from  $V_{dc}$  to  $P_{ac}$  control in an HVDC link. The switching was performed at the same time for both control loops.

Figure 1.4: Voltage transient during switching of control loops

The figure shows that an uncontrolled switching between the control loops can cause transients in the system that in this case lasts for around 0.2 seconds. To avoid this situation, the dispatch control operator has to manually operate a switch between the two control loops (i.e.  $P_{ac}$  and  $V_{dc} / Q_{ac}$  and  $V_{ac}$ ). Switching between the control loops can only be conducted when the currents in the two loops are approximately at the same value. This is important in order to avoid over-current and over-voltage situations[17].

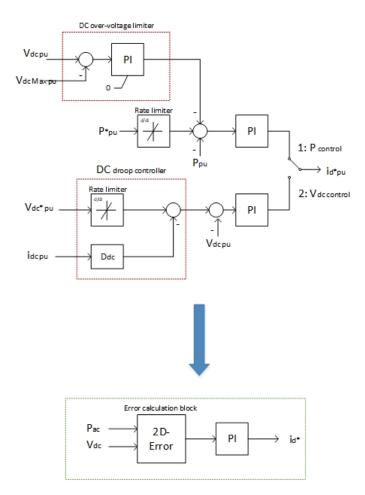

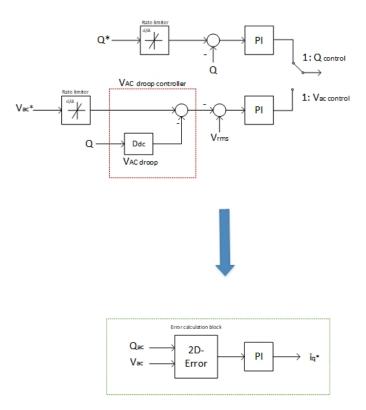

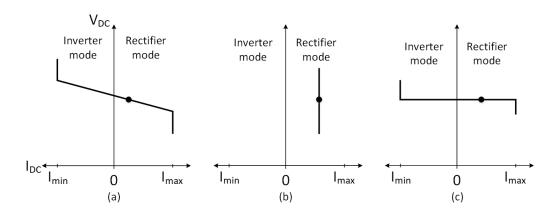

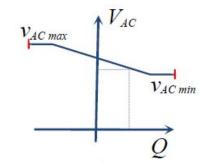

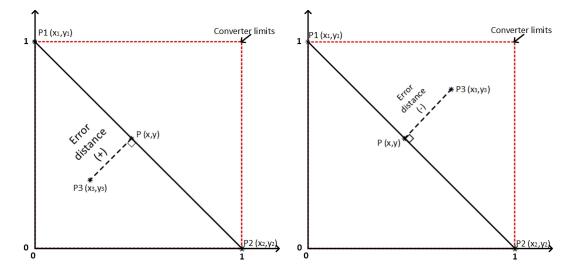

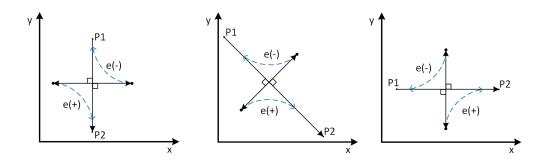

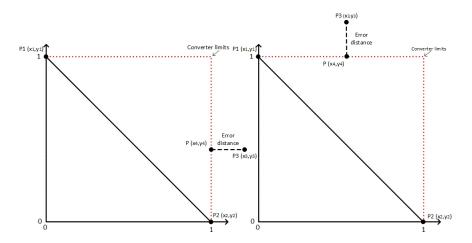

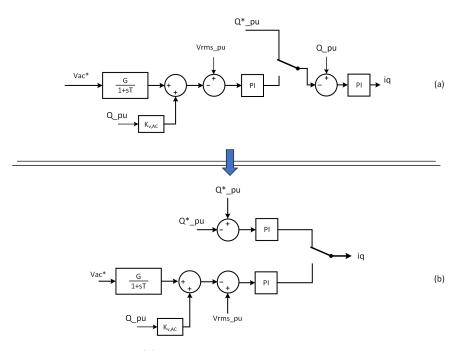

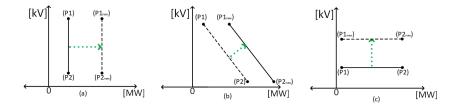

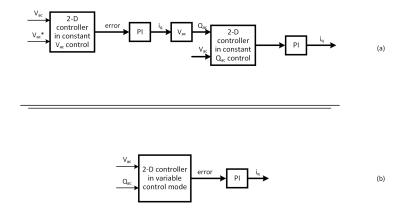

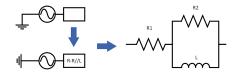

This thesis proposes a new upper level control scheme that can replace the 1-D control scheme developed by CIGRE in the [6]. The goal for the new controller will be to have a seamless switching between the control loops. In the proposed control scheme a droop control will be implemented to control the four controllers. This means that the control loops  $P_{ac}$  and  $V_{dc}$  will be dependent on each-other, and the  $Q_{ac}$  and  $V_{ac}$  loops will be dependent on each-other, and the Qac and Vac loops will be dependent on each other in a 2-dimensional plane. The conventional CIGRE system contains four, 1-dimensional (1-D) control loops. By making the control loops dependent on each other the four 1-D control loops will be reduced to two 2-D control loops. Figure 1.5 and Figure 1.6 depicts how the number of control loops are reduced.

Figure 1.5: Conventional and the proposed 2D-controller for P and  $V_{dc}$  control

**Figure 1.6:** Reduction of the reactive power and  $V_{ac}$  loop

As illustrated, a simplification of the 1-D system into the 2-D control system proposed in the green square. It can be seen that the switch between the  $V_{dc}$  and  $P_{ac}$  lops and the  $Q_{ac}$  and  $V_{ac}$  is eliminated, hopefully creating a seamless switching between the control loops. Another factor is that the 2-D controller will reduce the number of PI controllers in the upper level control structure. It is wanted to have one PI controller in the d-axis control loop, and one in the q-axis loop. This implies that the DC over voltage limiter loop which contains one PI controller will be eliminated. The goal is to instead create a new 2-D error calculation block as seen on Figure 1.5 and Figure 1.6, which contains an algorithm that will calculate the error between in the system. The error block should also contain limits for DC voltage, active power, reactive power and AC voltage. Reducing to only one PI controller for each control loop should lead to a shorter processing time, and a faster response if PI controllers placed in cascade are eliminated. A reduction in the number of PI controllers will also lead to less controllers that need to be tuned which means that the control will be easier to implement. The system will also have a higher reliability since there will be less components in the system.

The performance of the d- and q-axis loop in the 2-D controller has to be compared and verified with the performance of the 1-D controller. This will be conducted for ideal conditions. The 2-D controller will also be tested for its performance compared to the 1-D during non-ideal conditions in a PtP- and 3-terminal HVDC system. The goal of the testing in to verify that the 2-D controller can operate according to the 1-D controller. It is also wanted to investigate the advantages and drawbacks with the 2-D controller compared to the 1-D controller.

#### 1.2.1 Main Objectives

The objectives of the thesis will be conducted in the following steps listed as bullet points:

- Do a literature survey and get a deeper understanding of how the upper level control of VSC and the tuning of PI controllers works.

- Design a 2-dimensional controller that will achieve seamless switching

- Create a new upper level control scheme in PSCAD

- Develop a 2-D control loop that will operate to control  $P_{ac}$  and  $V_{dc}$

- Tune the PI controller to obtain tuning parameters working for  $P_{ac}$ ,  $V_{dc}$  and DC voltage droop control

- Develop a 2-D control loop that will operate to control  $Q_{ac}$  and  $V_{ac}$

- Tune the PI controller obtain tuning parameters working for  $Q_{ac}$  and  $V_{ac}$ ,

- Verify the operation of the d- axis and q-axis control loops by testing them for one converter during ideal conditions

- Test and performance of the d-axis control loop of the 1-D and 2-D controller in a PtP and 3-terminal HVDC system and compare the performance

- Seamless switching

- 3-phase to ground fault

- DC voltage droop control

- Permanent outage of one converter

- Evaluate and discuss the advantages/drawbacks of the 2-D controller compared to the 1-D

## 1.3 Limitations

- The only tuning parameters evaluated for use in the 1-D controller are the ones obtained from [6].

- The results of the 2-D controller will be evaluated for an equivalent grid.

- The q-axis control loop will not be tested for a PtP HVDC link or a 3-terminal MTDC system.

- The upper level control scheme for the 2-D controller do not contain a method to implement the decoupled current controller

- Gain scheduling will not be implemented for the 2-D controller

## Chapter 2

# Topology and Operation of the Voltage Source Converter

This chapter presents the basic topology and operation of a voltage source converter (VSC). First, the 2-level converter is presented and the PWM technique is described. Then the topology and operation of the half bridge MMC is explained. In the end the nearest level control (NLC) is presented.

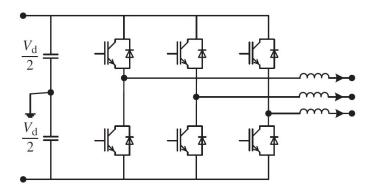

## 2.1 2-level Converter

The most simple converter topology of a VSC is the 2-level converter. The 2-level converter can be used to explain the basic operation principle of a VSC. Figure 2.1 depicts a 2-level converter with 3 phase legs. A 2-level converter can work either as a rectifier or an inverter, by changing the direction of the current. The capacitor in the converter works as a short term energy storage to keep the DC voltage constant between switching. The inductance connected in series between the midpoints of the phase leg and the the AC terminals ensures to maintain a constant current on the AC side in between phase leg commutations [18].

Figure 2.1: Configuration of a 2-level converter with 3-phase legs[18]

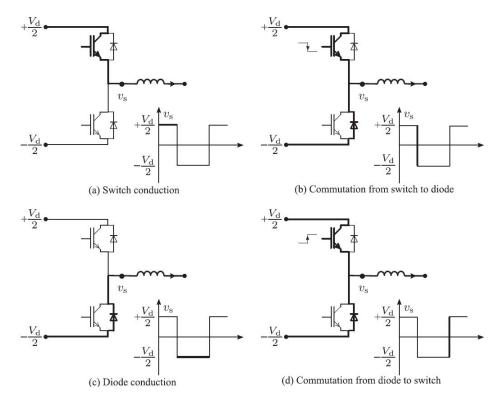

The switching sequence of a 2-level converter is shown in Figure 2.2 and can be used to explain the switching sequence of a 2-level converter. In the switching sequence, the AC-current is going in the same direction as indicated by the arrow on the figure. As seen in figure (a) the sequence starts with the upper switch conducting. The potential at the AC terminal, denoted as  $V_s$ , is now the same as the positive DC leg  $+\frac{V_d}{2}$ . Then in (b), the switch is turned off and the current will pass trough the lower diode. When the current is fully commutated to the lower diode as shown in (c), the voltage potential at the AC terminal will be negative  $-\frac{V_d}{2}$ . To make it possible to change the direction of the phase current, the lower switch is turned on after a delay named "blanking time". The blanking time makes sure that both switches are not in the on state at the same time which could damage the converter. To get a positive DC terminal potential again, the current is commutated from the lower diode to the upper switch as seen in (d). When the lower diode turns off, the DC terminal voltage is the same as in figure (a) and the cycle is repeated [18].

Figure 2.2: Switching sequence of a 2-level converter [18]

If the direction of the current had been in the opposite direction of what is indicated in Figure 2.2, the sequence would be the same except that the current would be commutating between the upper diode and the lower switch in (a). The potential at the AC terminal can be calculated by equation[18]:

$$V_s = s \frac{V_d}{2} \tag{2.1}$$

Here, s is denoted as +1 when the phase leg is connected to the positive DC terminal

and -1 when connected to the negative terminal.

#### 2.1.1 Sinusoidal Pulse Width Modulation

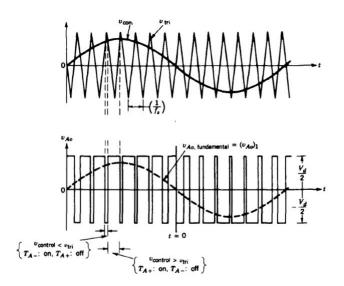

A modulation technique that is used for controlling the output voltage of a power converter is sinusoidal pulse width modulation (SPWM). The goal is to have a sinusoidal output of the converter where it is possible to control the magnitude and frequency. The principle of SPWM is presented in Figure 2.3. The sinusoidal voltage waveform is created by comparing a triangular waveform  $v_{tri}$  (often named carrier waveform) with a sinusoidal waveform/control signal ( $v_{con}$ ) at the wanted frequency.

Figure 2.3: Sinusoidal pulse width modulation waveforms [18]

It is the modulating frequency  $f_1$  of  $v_{con}$  that verify if the output voltage is not a clean sinusoidal waveform. The amplitude modulation can be expressed by the peak value of the two signals in Equation 2.2.

$$m_a = \frac{v_{con}}{v_{tri}} \tag{2.2}$$

$v_{tri}$  determines the switching frequency  $(f_s)$  of the converter. If the frequency of  $v_{tri}$  is of an odd multiple integer of the fundamental frequency, no even harmonics will exist in the waveform. In a balanced three phase AC system all zero sequence components (third, ninth...etc.) will be eliminated in the line voltages [11, 19]

The 2-level converter has drawbacks with power losses because of a high switching frequency leading to high amounts of harmonics and a low efficiency. Another drawback of the 2-level converter is that if it is wanted to increase the power rating, more and more IGBTs have to be connected in series[11].

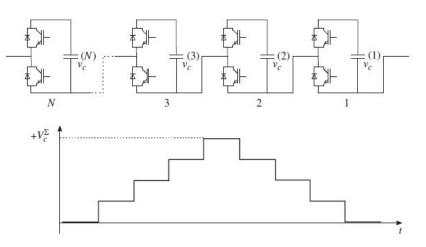

### 2.2 Topology and Operation of the Half-Bridge MMC

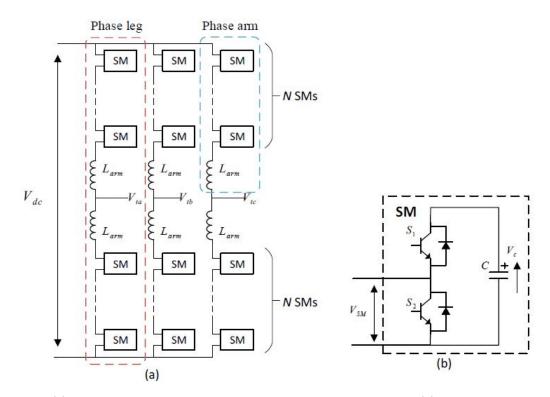

The two main topologies of the MMC used for VSC-HVDC today are named half bridge and full-bridge. The half bridge MMC topology is the one that will be considered in this thesis. In the half bridge, sub-modules (SMs) are assumed to be ideal voltage sources always having a constant voltage at the DC terminals. Figure 2.4 (a) present the topology of a three phase half bridge MMC and (b) shows the configuration of how a SM is designed[11, 18].

Figure 2.4: (a) shows the topology of a half bridge MMC with N SMs, while (b) presents the configuration of a SM[20]

As can be seen on the figure the converter has three phase legs, where each phase leg has one positive and one negative phase arm. The phase arms consists of a number of SMs in a string which again is connected in series. The SM contains two IGBTs, each connected across a freewheeling diode and in parallel with a capacitor)[18]. The freewheeling diode has the purpose of reducing over voltages (voltage spikes) due to the reverse recovery current at turn-off [19]. The capacitor should have a large capacitance and high voltage capability to maintain a stable voltage during commutation. The arm inductors are important for reducing the circulating current harmonics that occurs due to the SM switching[11]. The AC terminal is connected to the midpoint of the converter in the interconnection of the two arm inductors [21].

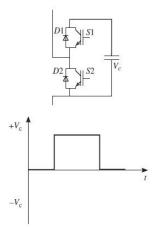

There are three operating states of the SM that exist, namely "inserted", "bypassed" and "blocked". The switching sequence of a SM is explained by using Figure 2.5 and is the following: In "inserted", (ON state) S1 is on and S2 is off. The output voltage of the

#### 2.2. Topology and Operation of the Half-Bridge MMC

SM,  $V_{SM}$  is in this state equal to the capacitor voltage  $V_c$ . The capacitor will charge with positive current and discharge with negative current. If "bypassed", (OFF state) the lower switch S2 is on and S1 is off.  $V_{SM}$  is zero and the voltage of the capacitor is constant. When the switching state is "blocking", both S1 and S2 are off meaning that the current can only conduct trough the freewheeling diodes. In this state capacitors will charge with positive currents, but it should ideally not discharge with negative currents [21]. The output voltage of the SM can explained by equation:

$$V_{SM} = sV_c \tag{2.3}$$

Where  $V_c$  is the capacitor voltage, s can be either 0 or 1, 0 if bypassed and 1 if inserted.

Figure 2.5: Upper and lower SM string voltages during one cycle[18]

By connecting SMs in series forming a string it is possible for the converter to operate with a higher terminal voltage since the voltage level is depending on how many SMs connected. Converters designed for high voltage can contain strings with hundreds of SMs connected in series. Using a high level of SMs will result in a more complex converter with more levels where each level will be smaller in size creating an almost sinusoidal output voltage [18, 21]. A MMC with N SMs per arm has N+1 number of phase voltage levels[20]. The number of voltage levels and output voltage is depicted in Figure 2.6.

Figure 2.6: Possible voltage levels for a half bridge string[18]

#### 2.2.1 Nearest Level Control

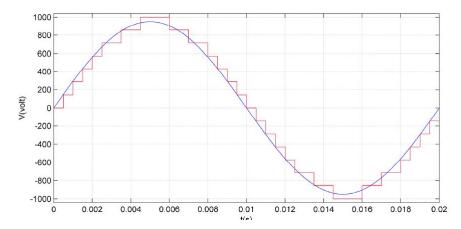

A modulation technique that will be used for the half-bridge MMC in this thesis is the nearest level control (NLC). NLC is a good modulation method when operating with converters that has a high number of SMs per phase arm. This makes the AC voltage being generated as steps leading to less commutations each semiconductor and lower switching losses. Because of the high number of SMs in each phase arm, the low frequency harmonics and the filter requirements becomes lower. The sampling time in the NLC can either be fixed or variable.

When the NLC operates with a fixed sampling time the variation between the voltage steps will make the voltage output deviate from the desired AC waveform. It is important that the sampling time is low so the variation in the AC voltage is only one step and not multiple steps. The reference voltage is then approximated to the nearest level that is available. This behaviour can be seen in Figure 2.7[18, 22].

Figure 2.7: NLC with fixed sampling period. The sinusoidal reference is marked in blue and the generated voltage is red[22]

#### 2.2. Topology and Operation of the Half-Bridge MMC

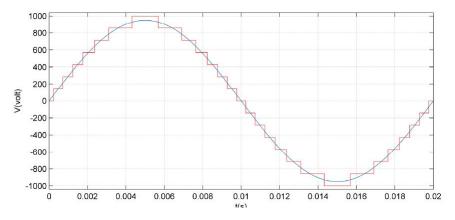

When operating with a variable sampling period, the switching in the between the levels occurs when the sinusoidal reference exceeds the "middle" value between the two levels. An example of this can be seen on Figure 2.8. This method has the advantage of balancing the capacitor voltage in each SM[18, 22].

Figure 2.8: NLC with varied sampling period. The sinusoidal reference is marked in blue and the generated voltage is red[22]

## Chapter 3

# System and Control of VSC-HVDC Systems

This chapter introduces the upper level control structure, and the theory for control modes used for the VSC control scheme. First the hierarchy and upper level control scheme for the 1-D controller is described. Then the current vector control scheme is explained followed by the PI-controller. At last, three voltage control schemes are explained, namely DC voltage droop control, master-slave strategy and the AC voltage droop.

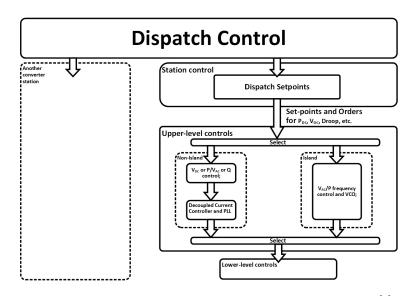

## 3.1 Control of VSC-HVDC systems

The control structure of a VSC-HVDC can be separated into the following three levels, dispatch control, upper level control and lower level control. Figure 3.1 illustrates the control hierarchy with dispatch control being the control on top sending the dispatch settings onto the upper level control, from here signals are further distributed down the the lower level controls. According to [6] the definition of the dispatch controller is; "the control mode refers to how functionality of the converter is operated, DC voltage control, power control of frequency, and AC voltage control vs. reactive power Q or power factor control". The dispatch control is responsible for changing control settings at the converter terminals when it is needed, and provides the reference signals,  $P_{ac}$ ,  $V_{dc}$ ,  $Q_{ac}$ , and  $V_{ac}$  for the upper level control modes,  $P_{ac}$  control the converter will be set as rectifier/inverter to inject/consume to/from the grid, also known as a slave bus in the master-slave control structure. In  $V_{dc}$  control the converter is set as maintaining a fixed voltage in the DC grid, making the  $V_{dc}$  as a control mode that can inject/withdraw power to maintain a stable DC grid, also known as a master bus in the master-slave control strategy.

Figure 3.1: Control hierarchy of the non-islanded VSC controls [6]

The upper level control receives orders/set-points from the dispatch control and provides reference signals to the lower level controls. The configuration of the controller is changed based on if the control is connected to a non-islanded or islanded system. The non-islanded control mode is used when the converter is connected to an AC system with active synchronous generation. Figure 3.3 shows the standard upper level control scheme configuration when using current vector control [6].

#### 3.1.1 Upper Level Control

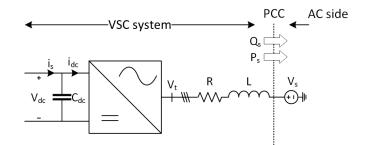

When looking into the upper level control scheme it is of big help to represent the different control modes of the control scheme to understand their behaviour. Figure 3.2 depicts a VSC converter connected to a equivalent grid. The figure displays where the parameters  $P_{ac}$ ,  $V_{dc}$ ,  $Q_{dc}$  and  $V_{ac}$  are measured and fed into the control of the VSC [23, 24].

Figure 3.2: VSC connected to a passive network

In the figure  $V_s$  represent grid voltage,  $V_t$  converter voltage,  $P_{ac}$  active power flow,  $Q_{ac}$  reactive power flow, the RL filter, the DC capacitor  $C_{dc}$  and  $V_{dc}$  which measures the DC voltage level at the DC side of the converter. Because of the VSC capability of controlling

#### 3.1. Control of VSC-HVDC systems

the current in both d-axis  $(i_d)$  and q-axis  $(i_q)$ . The control scheme is divided where the d-axis controls  $V_{dc}$  and  $P_{ac}$  produces reference for  $i_d$  and in q-axis control where  $Q_{ac}$  or  $V_{ac}$  provides a reference for  $i_q$ . This Control scheme is conducted by implementing a current vector control[23, 24].

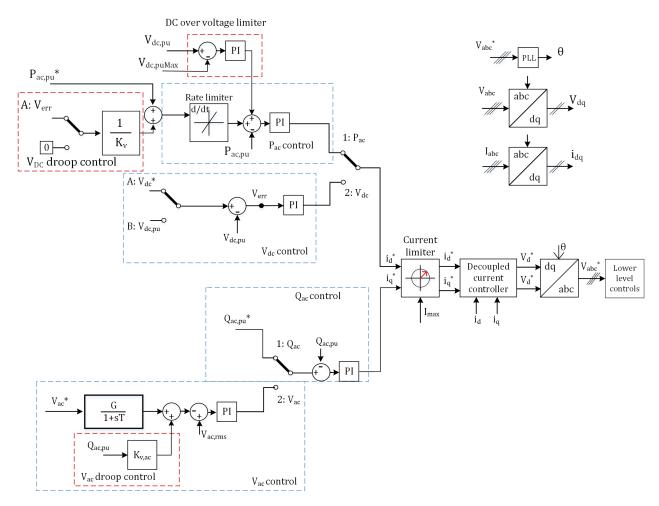

The upper level control structure for VSC for the 1-D controller used by CIGRE [6] is depicted in Figure 3.3. The figure displays the control loops for d-axis and q-axis and that the reference signals  $i_d^*$  and  $i_1^*$  is further distributed to the decoupled current controller.

Figure 3.3: The upper level control structure for VSC[6]

The control structure shows for the d-axis control loop that if the control mode is set to operate as  $V_{dc}$  control, the control loop will use  $V_{dc}^*$  and subtract  $V_{dc,pu}$ , where the difference (error)  $V_{err}$  will be passed on to the PI controller. When the control mode is set to  $P_{ac}$  control the switch shown in  $P_{ac}$  control loop will be set to state B, which will eliminate the droop control term. When the controller operates in  $P_{ac}$  control the difference between  $P_{ac}^*$  and  $P_{ac,pu}$  will be sent as the error into the PI controller. If the control mode is set as DC voltage droop control, the switch choosing between  $V_{dc}$  and  $P_{ac}$  will be set to  $P_{ac}$  and the

switch in  $P_{ac}$  control be set to state B, here the  $V_{dc_err}$  will be multiplied with  $\frac{1}{K_v}$ .  $V_{dc_err} \frac{1}{K_v}$  is then added together with  $P_{ac,pu}$  before the error is sent to the PI-controller. The result of this addition is then subtracted by  $P^*_{ac,pu}$ . This means that the error passed on to the PI-controller in droop control mode for d-axis can be expressed by Equation 3.1 and for q-axis in Equation 3.2:

$$error_{DC,droop} = (V_{dc,pu}^* - V_{dc,pu})\frac{1}{K_v} + (P_{ac,pu}^* - P_{ac,pu})$$

(3.1)

$$error_{AC,droop} = V_{ac,rms} - (V_{ac}^* + K_{v,ac} \cdot Q_{ac,pu})$$

(3.2)

The q-axis loop is presented as a cascaded system. When the control mode is operating in  $Q_{ac}$  control the error is the difference between  $Q_{ac,pu}^*$  and  $Q_{ac,pu}$ . In  $V_{ac}$  control it can be seen that both  $V_{ac}$  and  $Q_{ac,pu}$  are inputs in the  $V_{ac}$  loop where both values are subtracted from the  $V_{ac,rms}$ . Since  $V_{ac}$  and  $Q_{ac}$  are measured at the same PCC as shown in Figure 3.2, the operation of the  $V_{ac}$  loop can evaluated in a way so that the  $V_{ac}$  control provides a "reference" for the reactive power control. The reactive power control will then adjust its behaviour after the value of the  $V_{ac}$ . In AC droop control the same principle will work as for the  $V_{ac}$  control, it is just that the  $Q_{ac,pu}$  will be multiplied by the droop constant  $K_v$ .

The  $i_q^*$  and  $i_d^*$  provided by the d-axis and q-axis control loops are then sent into a decoupled current controller. The decoupled current controller will allow control of both  $i_d$  and  $i_q$  individually. Hence it is possible to control both  $P_{ac}$  and  $Q_{ac}$  individually which are sent into the grid to contribute to a stable grid voltage and power angle[6].

## 3.2 Current Vector Control

Current vector control is a common method to control VSC-HVDC systems. The method represents 3-phase signals as 2-static signals in a 2-dimensional system known as d-q reference frame. It also has the possibility for independent control of active and reactive power. This allows for the use of PI controllers to remove static errors [14]

The transformation from three phase signals to two phase rotating signals in a 2 axis, 2 dimensional system is represented by the following steps:

- Transformation from the stationary abc reference frame (three phase signals) to the stationary  $\alpha\beta$  reference frame, also named Clark transformation

- Transformation from the stationary  $\alpha\beta$  reference frame to the synchronously rotating d-q reference frame, also referred to as Parks transformation

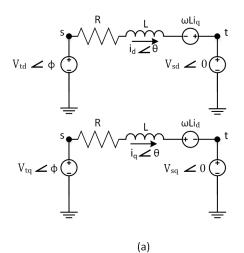

In current vector control, the currents  $i_d^*$  and  $i_q^*$  can be controlled separately. The current  $i_d^*$  controls either active power or DC voltage, while  $i_q^*$  regulates Q into a strong grid or supports with AC voltage when connected to a weak grid[25]. To control both  $i_d$  and  $i_q$  separately, two equivalent circuits can be obtained from Figure 3.2, which is depicted in Figure 3.4.

Figure 3.4: (a) Equivalent circuit for calculating the active and reactive power[23]

The equivalent circuits can be used to obtain equations for  $P_{ac}$  and  $Q_{ac}$  as Equation 3.3 and Equation 3.4.

$$P_{dq} = \frac{3}{2} V_{td} i_d \tag{3.3}$$

$$Q_{dq} = -\frac{3}{2} V_{td} i_q \tag{3.4}$$

As it can be observed,  $V_{sq}$  do not appear in the equations since  $V_t$  is always aligned with the  $V_{td}$  to ensure a stable system[23].

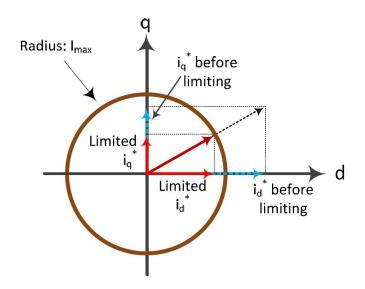

The reference currents  $i_d^*$  and  $i_q^*$  are then sent to a current limiter block. The current limiter limits the magnitude of the current to  $i_{max}$ . Figure 3.5 shows how the current limiter limits the reference currents  $i_d^*$  and  $i_q^*$  and are sent to the decoupled current controller. The decoupled current controller generates the reference voltages  $V_d^*$  and  $V_q^*$  and sends them to the reference frame transformation block, where the voltage is synchronized with the angle from the PLL. The reference voltage  $V_{abc}$  is then sent to the lower level controls [6].

Figure 3.5: Current limiting scheme showing how the reference currents  $i_d$  and  $i_q$  are limited [6]

#### 3.2.1 Clarks Transformation

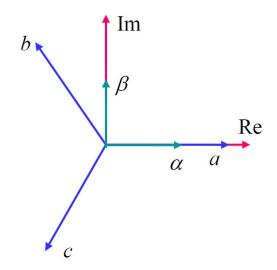

In this transformation the three phase signals are represented as a 3-axis, 2 dimensional plane namely stationary abc reference frame. Each axis in the 3-axis plane are placed with 120° between each other. This is also illustrated by the following equations. The representation of abc reference frame displayed together with the stationary  $\alpha\beta$  reference frame is shown in Figure 3.6

$$f_a = f_{peak}cos(\omega t)$$

$$f_b = f_{peak}cos(\omega t - 120^\circ)$$

$$f_c = f_{peak}cos(\omega t + 120^\circ)$$

**Figure 3.6:** Representation of the abc and  $\alpha\beta$  in the same coordinate system

It can be seen in the figure that the  $\alpha$  axis is aligned with the real axis and the  $\beta$  axis is aligned with the imaginary axis with 90° separation between the axes.

The Clarks transformation from abc to  $\alpha\beta$  reference frame is:

| $\begin{bmatrix} f_{\alpha} \\ f_{\beta} \\ 0 \end{bmatrix} = \frac{2}{3}$ | $\begin{bmatrix} 1 \\ 0 \\ 0 \end{bmatrix}$ | $\begin{array}{c} -\frac{1}{2} \\ \frac{\sqrt{3}}{2} \\ 0 \end{array}$ | $\begin{bmatrix} -\frac{1}{2} \\ -\frac{\sqrt{3}}{2} \\ 0 \end{bmatrix}$ | $\begin{bmatrix} f_a \\ f_b \\ f_c \end{bmatrix}$ |

|----------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------|

|----------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------|

#### 3.2.2 Parks Transformation

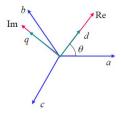

The  $\alpha\beta$  reference frame can be transformed into a rotating d-q reference frame by using Park/inverse Park transformation. In the d-q frame the d-axis is aligned with the real axis and the q-axis is always 90° projected from the d-axis at all times. The d-q frame is synchronized with the grid the voltage and currents will appear as constant d-q frame vectors as can be seen in Figure 3.7 [23, 25].

Figure 3.7: Representation of the rotating d-q reference frame [26]

When transforming from  $\alpha\beta$  to d-q reference frame the angle between the  $\alpha$  axis and the d-axis is used. The voltage vector position is expressed by:

$$\theta = \tan^{-1}(\frac{V_{\beta}}{V_{\alpha}}) \tag{3.5}$$

$V_{\alpha}$  and  $V_{\beta}$  are the voltage components of the  $\alpha\beta$  reference frame. This angle is important for having independent control of active and reactive power.

The parks transformation matrix from  $\alpha\beta$  to d-q frame is shown in:

| $\left[f_d\right]$       | $\cos\theta$ | $sin\theta$ | 0 | $f_{\alpha}$          |

|--------------------------|--------------|-------------|---|-----------------------|

| $\left  f_{q} \right  =$ | $-sin\theta$ | $cos\theta$ | 0 | $f_{\beta}$           |

| $f_0$                    | 0            | 0           | 1 | $\lfloor f_0 \rfloor$ |

In Equation 3.5, the value of  $\theta$  is obtained by using the phase lock loop (PLL) technique [14]. The PLL tracks the phase angle of the AC grid, and gives a reference signal to the converter controller in order to synchronize with the grid [11]. In the PLL, it is chosen to set the voltage vector of phase-a equal to the d-axis at a point of common coupling (PCC), since the PLL operates in steady state. The phase lock loop should be locked onto the phase-a vector at the PCC. PCC represents where the VSC is physically connected to the ac grid. [25].

## **3.3** PI Controller

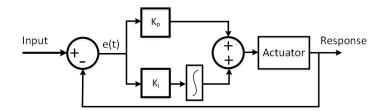

Since PI controllers are often used in control loops and some places in the VSC control structure, it is of good knowledge to understand its behaviour and how to perform tuning of a PI controller. This section presents the PI controller followed by its transfer function and tuning.

The objective of a PI controller is to remove the difference between a set-point and a desired steady-state (S.S) value. The PI controller consists of a proportional (P) and an integral (I) gain. These two controller gains are both multiplied with the error of the system. If the I-term in a PI controller is set to zero, the PI controller is equal to the P controller. A drawback with the P-controller is that it will not have the ability to remove steady state errors completely from the system. With a PI controller this problem is solved since the I-term is used to integrate the error over time and remove its steady-state error during operation.

A representation of the PI controller as a block diagram is depicted in Figure 3.8. The PI controller is set to control an actuator/plant which represent the actual system a PI controller is set to control. It can be seen that the PI-controller operates as a feedback loop, which means that the controller will go in a loop until the error between the reference and the measured value is eliminated.

Figure 3.8: Generic representation of a PI controller

The block diagram of the PI controller can be represented as the in Equation 3.6. It is first expressed in the time domain, then transformed and represented in the Laplace domain.

$$g(t) = e(t) \cdot K_p + K_i \int e(t) \cdot dt$$

$$\downarrow$$

$$\mathcal{F}\{g(t)\}$$

$$\downarrow$$

$$G(s) = K_p + \frac{K_i}{s} = K_p + \frac{1}{T_i s}$$

$$(3.6)$$

Here,  $K_p$  represents the proportional gain,  $K_i$  represents the integration gain. When tuning, having a high  $K_p$  will create a large change in the output for a given change in the error. A too large  $K_p$  can make the system unstable. On the other hand, a small  $K_p$  makes the system less sensitive meaning that it will have a small response to a large input error. A too low  $K_p$  can create a situation where the system does not manage to respond good enough to system disturbances[27].

$T_i$  is a constant that is used to describe how much weight that should be put onto the integral factor compared to the proportional part. It is important to notice that  $K_i = \frac{1}{T_i}$  meaning that a higher  $T_i$  gives a small contribution from the integral part, and a lower  $T_i$  gives a higher contribution. The size of  $T_i$  is important for how fast the error can be removed. If  $T_i$  is set to infinite, the contribution from the integral term will be zero. The higher the  $T_i$  the longer the time to reach the final value. A too low  $T_i$  can lead to oscillations and an unstable system. The tuning of the PI controller is based on adjusting the values of  $K_p$  and  $T_i[14, 28, 29]$ .

#### 3.3.1 PI Controller Tuning

It is important to implement the correct tuning gains in the PI controller in order to make it work properly. In a HVDC system, the PI controller should be tuned as a compromise between how fast the response should be, how stable the system is going to be during a small disturbance and how robust it is towards large disturbances in the signal. The outer loop should be tuned to towards stability and to have the best regulation (little disturbance). The outer voltage loop should also work to stabilize the DC voltage, hence this is how the PI controller should be tuned. The inner control loop should be tuned to have a fast response. When PI controllers are arranged in a cascaded arrangement, the outer loop should be so slow that it will always be able to read a S.S value from the inner PI controller, hence normally it should be 10 times slower than the inner control loop[14].

#### 3.3.2 Evaluation of a 2.Order System

The objective of this subsection is to present and explain important factors when evaluating the performance of a PI-controller and tune to it correctly. A generic transfer function for a 2. order system in the Laplace domain can be defined as Equation 3.7 [30]:

$$Y(s) = \frac{\omega_n^2}{s^2 + 2\zeta\omega_n s + 1}R(s) \tag{3.7}$$

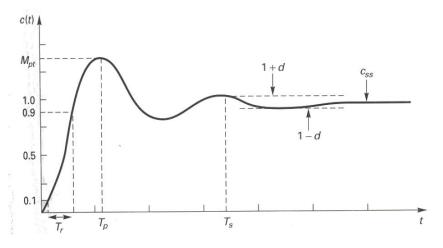

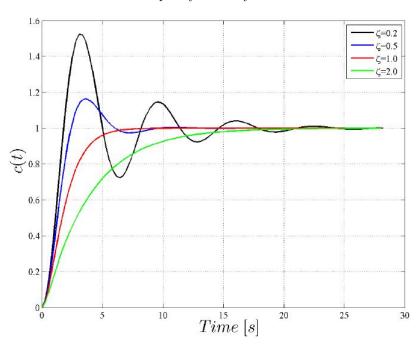

Here,  $\omega_n$  is the natural frequency,  $\zeta$  is the damping coefficient which can be decided based on the wanted performance within the operating range of the system, R(s) is the output, and Y(s) is the input. To evaluate the performance of a 2.order system, the unit step response shown in Figure 3.9 can be used.

Figure 3.9: Unit step response for a 2.order system showing different terms as rise time, peak amplitude and final value [31]

The parameter  $T_r$  represents the rise time of the system and is according to [31] referred to as "the time it takes for a response to rise from 10 % of its final value to 90% of its final value".  $C_{ss}$  is the final value of the response. The peak value is denoted as  $M_{pt}$ , and  $T_p$ is the time it takes to reach this peak value. The overshoot is defined in percentage as the difference between the peak value and the final value, as can also be seen in the equation below[30]:

$$Overshoot = \frac{M_{Pt} - C_{ss}}{C_{ss}} \cdot 100 \tag{3.8}$$

The settling time  $T_s$  is according to [30] defined as "the time required to for the system to settle within a certain percentage delta ("d") of the input amplitude". The delta (d) can be seen in Figure 3.9 as the area 1-d, and 1+d. For a 2.order system it is wanted to find the  $T_s$  when it is approximately 1% or 2% of the final value. To have the system settle at its final value within 2% around 4 time constants are needed. This Equation 3.9 where  $T_s$  can be calculated by the 2% criteria [30, 31].

$$T_s = 4\tau = \frac{4}{\zeta\omega_n} \tag{3.9}$$

All parameters described above can be used to evaluate the performance of the 2.order system. Especially the overshoot and  $T_s$  are important parameters for evaluating stability and speed.

The parameter  $\zeta$  is known as the damping coefficient and can be determined based on what response is wanted from the system. The definition of all parameters are based on an under-damped system. In an under-damped system  $0 < \zeta < 1$ , in un-damped system  $\zeta = 0, \zeta = 1$  gives a critically damped system and  $\zeta > 1$  leads to an over-damped system. Figure 3.10 shows different step responses for a 2.order system using various values for  $\zeta$ . It can be seen that the there is a higher overshoot and also more oscillations when using a  $\zeta$ equal to 0.2, while  $\zeta$  equal to 2 the signal use more time to reach the reference value. The natural frequency  $\omega_n$  is defined as [30, 31]:

$$\omega_n = 2\pi f \tag{3.10}$$

Where f is 50 Hz and the natural frequency of the system.

**Figure 3.10:** Step response for a 2.order system using different values for  $\zeta$  [32]

#### 3.3.3 Controller Tuning of the DC Voltage Loop

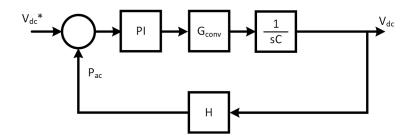

The method used to tune the PI controllers in the upper level control of the 1-D controller is proposed by Akkari [16]. The DC voltage loop can be represented by Figure 3.11 as a block diagram .

Figure 3.11: DC voltage loop

As it can be seen from the block diagram, the transfer function for the DC loop can be obtained by multiplying the function of the PI controller with the converter and the plant. In order to avoid disturbances with the control loops in series (outer and inner control loops), the outer control loop is usually set as 10 times slower than the inner control (i.e current control), so that the inner control loop is able to complete its loop before the outer control loop. This means that when calculating the transfer function of the DC loop, the inner control can be neglected. The  $V_{dc}$  PI control loop will be represented on the following form:

$$G_{V_{dc}}(s) = K_{pV_{dc}} + \frac{K_{iV_{dc}}}{s}$$

(3.11)

The transfer function of the plant is  $\frac{1}{sC}$  and the converter is represented as a gain with the value of 1. The "sensor" H is used to transform the measured value into a value that can be used in order to calculate the error sent to the PI controller. In this case H has the value of 1.

The closed loop function of the system is:

$$\frac{Vdc}{Vdc, ref} = \frac{G_{PI}G_{conv}G_{plant}H}{1 + G_{PI}G_{conv}G_{plant}H}$$

The transfer function of the DC loop then becomes:

$$\frac{V_{dc}}{V_{dc,ref}}(s) = \frac{1 + \frac{K_{p,V_{dc}}s}{k_{i,V_{dc}}s}s}{1 + \frac{K_{pV_{dc}}s}{K_{iV_{dc}}s} + \frac{C_{dc}}{K_{iV_{dc}}s^2}s^2}$$

The tuning parameters can then be extracted by comparing the transfer function of the DC loop with the second order system transfer function from Equation 3.7. The equations for tuning  $K_p$  and  $T_i$  in the DC voltage loop is shown below:

$$K_{i,V_{dc}} = \omega_n^2 C_{dc,eq}$$

$$K_{p,V_{dc}} = 2\zeta \omega_n C_{dc,eq}$$

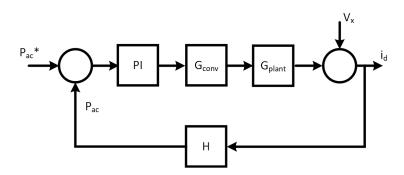

#### 3.3.4 Controller Tuning of AC Power Loop

The principle of the tuning method proposed by Akkari [16] has also been used to obtain the transfer function of the  $P_{ac}$  control loop. The  $P_{ac}$  control loop is depicted in Figure 3.12.

Figure 3.12: Active power loop

By using the PI control loop as shown in section 3.3, the PI control loop can be expressed as the following:

$$G_{P_{ac}} = K_{pP_{ac}} + \frac{K_{iP_{ac}}}{s} \tag{3.12}$$

as well as, H represent a gain which transform  $i_d$  into  $P_{ac}$  which is equal to 1 pu. It is important to notice that H represent the measured voltage in the system. The transfer function of  $G_{conv}$ , which represent the impedance of the low-pass filter is:

$$G_{conv} = \frac{1}{1+Ts} \tag{3.13}$$

Due to the design process the noise from  $V_x$  as shown in Figure 3.12 is considered as zero. By combining the gains to create and to obtain a closed loop transfer function, the total transfer function becomes:

$$\frac{i_d}{P_{ac}*} = \frac{G_{P_{ac}}G_{plant}G_{conv}H}{1 + G_{PI}G_{plant}G_{conv}H}$$

(3.14)

From Equation 3.14, the controller gains  $K_p$  and  $K_i$  can be obtained and is as follows

$$K_{pPac} = \frac{2\zeta\omega_n}{L} - 1$$

$$K_{iPac} = \frac{\omega_n^2}{L}$$

#### Manual Tuning of the PI Controller

There are several ways of tuning a PI-controller, one method that does not require any calculations or equations is the manual tuning method of the PI-controller. The fastest loop (i.e. shortest settling time) is the one adjusted first by either increasing or reducing  $K_p$  and  $T_i$ . Then the response of the loop is analyzed (by evaluating the parameters explained in subsection 3.3.2 and if it is not good enough, the tuning parameters has to be adjusted and a new simulation has to be conducted. According to [27] there are some rules of thumb when tuning the PI-controller by the trial and error method:

- If the response is oscillating too much then reduce  $K_p$  or increase  $T_i$

- If the response time is to long when conducting a step then reduce  $T_i$

- If the dynamic deviation is to big, increase  $K_p$

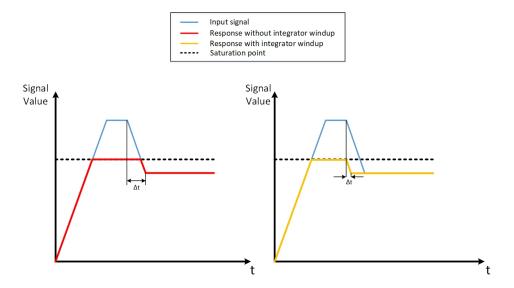

#### 3.3.5 Integrator Wind-up

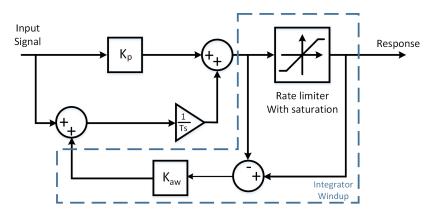

For a PI controller where saturation occurs, anti-windup can be implemented to avoid such phenomena where the system cannot respond to changes due to where the signal value has reached beyond the saturation point. Without this action the controller cannot perform any changes in the system before it has moved away from the saturation point. As shown in Figure 3.13, the response time is reduced when such improvement is added to the system. The controller can therefore respond to changes even though the signal value appears outside of the saturation point of the system (i.e. response time of the system  $\Delta t$  is reduced). [28, 33]

Figure 3.13: Graphical representation of the function of a Integral wind-up

As illustrated in the figure,  $\Delta t$  become reduced when an integrator wind-up is added to the system. A presentation of this addition when implemented in the system is presented in Figure 3.14.

Figure 3.14: Circuit representation of the function of the Integrated integral action added to the PI controller

As depicted, a signal before and after the rate limiter is measured, when these values are not equal, the difference is multiplied with the anti-windup constant and added to the I integrator term to amplify the integrator gain, this will create a behaviour as already illustrated in Figure 3.13

## **3.4** Voltage Control Methods

Several strategies exist for controlling the voltage. The ones important for this thesis are mentioned here to give an overview of how the methods work.

#### 3.4.1 Master-Slave Strategy

This control strategy is a proposed strategy for controlling power flow within a MTDC system. A control mode which is built on conventional PtP-HVDC control[34]. In a DC network  $V_{dc}$  is the signal that will be held as a reference to control and maintain power flow between converters.

The master-slave strategy works with the slave bus operating as a passive load/generation, while the master-station operate to ensure power balance of the system by injecting/consuming power to stabilize the system. The master bus will ensure to control  $V_{dc}$ . This means that if  $V_{dc}$  decreases, the master converter will inject power to maintain a stable grid, while a slave bus will control a constant power in either inverter/rectifier mode at its PCC. A drawback of the method is that if the master converter is disconnected/trips, the entire system will break down. Also the choice of which converter station that is going to be chosen as the master station will depend on the converters ability to deal with large large power deviations which leads to that the station with the highest power rating to become the master station [35].

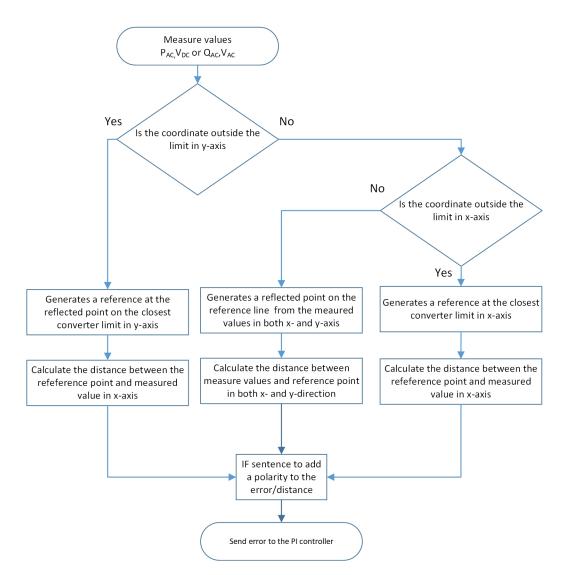

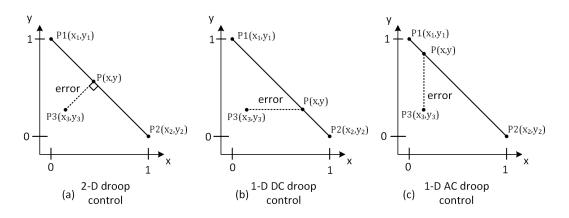

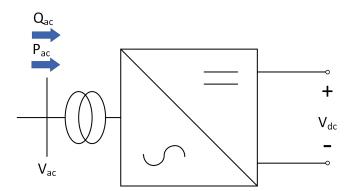

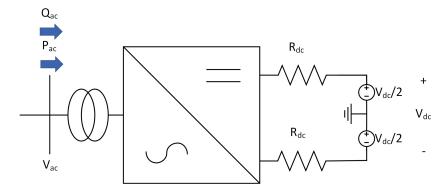

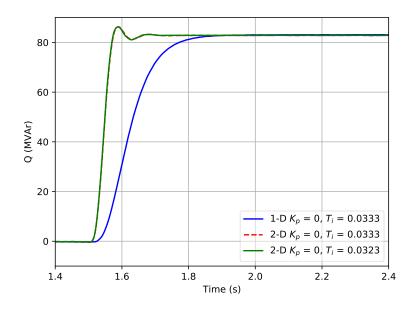

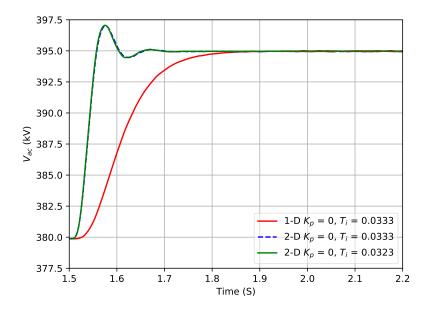

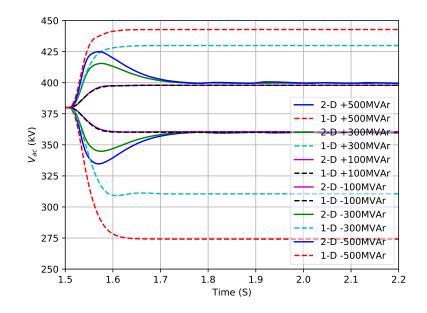

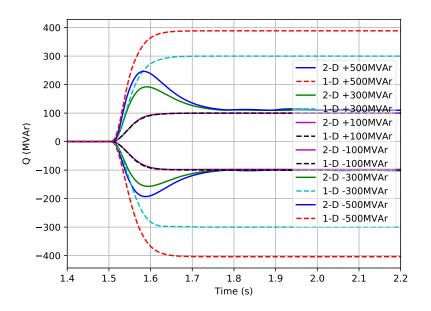

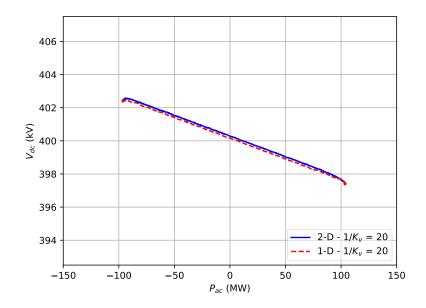

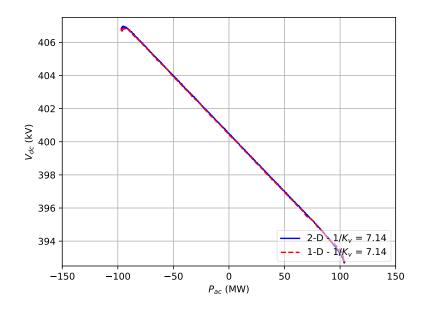

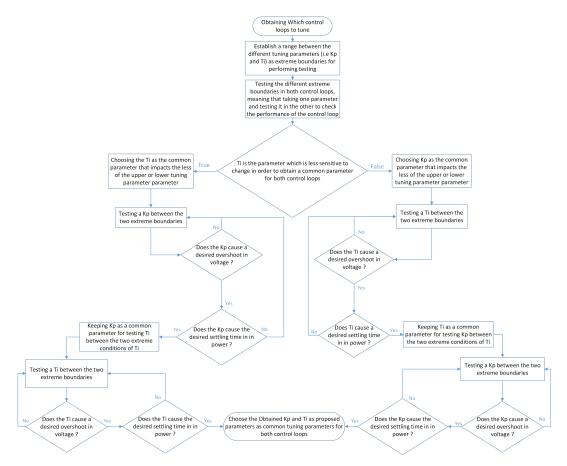

#### 3.4.2 DC Voltage Droop Control