# SDR Implementation of a OFDM-MIMO Receiver

MASTER THESIS 10<sup>TH</sup> SEMESTER 2008 PROJECT, AAU APPLIED SIGNAL PROCESSING AND IMPLEMENTATION (ASPI)

> Group 1046 Morris Filippi

#### Institute for Electronic Systems

Fredrik Bajers Vej 7B Telefon 96 35 98 36 Fax 98 15 36 62 http://www.esn.aau.dk

#### Title: SDR Implementation of a OFDM-MIMO Receiver

Theme:

OFDM - MIMO Algorithms and Architectures, Optimal VLSI Signal Processing

Project period: P10, spring semester 2009 01/02/09 - 30/06/09

Project group: ASPI 09gr1046

Group member: Morris Filippi morris@es.aau.dk

Supervisors: Yannick Le Moullec (AAU) Andrea Fabio Cattoni (AAU, Nokia-Siemens)

Copies: 4 + 4 CD-ROM

Number of pages in Report:

Number of words:

Finished: 03/06/09

#### Abstract:

The word diversity, in telecommunication, means MIMO systems, that is transmitting the signals through multiple antennas (Multiple Input Multiple Output), and it can be performed in various domains, such as space and time. Thanks to MIMOs (i.e. Spatial Multiplexing, Space-Time Coding) is possible to increase the bit-rate maintaining the same implementation constraints, as transitting power and bandwidth availability. These diversity techniques exploit the redundant transmission of data on the various antennas, allowing the decoding at the receiption by precise algorithms. The purpose of this project was to identify which type of algorithmic improvements can be used to increase the spectral efficiency of an OFDM/MIMO receiver, while maintaining its HW feasibility. In this report, the designer propose a possible solution to the problem statement. This is the identification of two new techniques, which are conceived to solve the central problem of the MIMO with more than two transmitting antennas: the quasi-orthogonality of product between channel matrix and its Hermitian. This report contains the implementation steps in order to converge to a feasible hardware solution, starting from the initial problem

to the final simulations and SW/HW cosimulation.

## Preface

This report serves as documentation for the 10<sup>th</sup> semester project in "Applied Signal Processing and Implementation" (ASPI) at the Institute of Electronic Systems of Aalborg University (AAU). The project is a "Software Defined Radio Implementation of a MIMO Receiver with two switchable modes", made by the group 1046. The work is co-supervised by the Software Defined Radio Center (CSDR) division of Aalborg University.

The report consists in three main parts:

Analysis, that treats the methodology Rugby Meta-Model, the OFDM, MIMO and SDR theory;

**Design**, which contains the development steps of the receiver's implementation;

**Evaluations**, which explains the results obtained, the possible future implementations and the conclusions.

The software used are: MatLab, Simulink, System Generator.

(signature) Morris Filippi

# Contents

| PART I: Analysis                             |    |

|----------------------------------------------|----|

| 1. Introduction                              | 11 |

| 1.1. Context                                 | 11 |

| 1.2. Problem definition.                     |    |

| 1.3. Report structure                        | 11 |

| 2. Models and Methodologies.                 |    |

| 2.1. A <sup>3</sup> Model                    | 13 |

| 2.2. Y-Chart                                 | 15 |

| 2.3. Attack methodology                      | 17 |

| 2.4. Rugby Meta-Model.                       | 19 |

| 2.5. HW and SW implementation.               | 22 |

| 2.6. Comparison and discussion.              | 23 |

| 3. OFDM & MIMO theory                        | 25 |

| 3.1. OFDM systems.                           | 25 |

| 3.1.1. Introduction                          | 25 |

| 3.1.2. Multicarrier transmission             | 25 |

| 3.1.3. Cyclic prefix as guard interval       | 30 |

| 3.2.MIMO systems                             |    |

| 3.2.1. Introduction                          | 32 |

| 3.2.2. The concept of diversity              | 33 |

| 3.2.3. Spatial Multiplexing                  |    |

| 3.2.4. Alamouti STBC                         |    |

| 3.2.5. Alamouti STBC 4x1 with feedback       |    |

| 3.3. WMAN IEEE 802.16                        | 41 |

| PART II: Design                              |    |

| 4. Idea.                                     | 47 |

| 4.1. The problem                             |    |

| 4.2. Proposed solution.                      |    |

| 5. Constraints and Requirements.             |    |

| 5.1. Cost function.                          |    |

| 5.2. Assumptions.                            |    |

| 5.3. Matlab, Simulink and System Generator   |    |

| 6. System analysis and modeling              |    |

| 6.1. Global description.                     |    |

| 6.2. Algorithm Analysis                      |    |

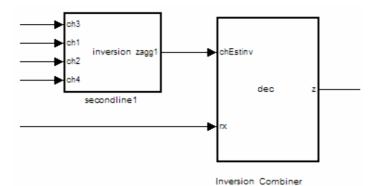

| 6.2.1. Channel inversion combiner 4x1        |    |

| 6.2.2. Subtractive combiner 4x1              | 58 |

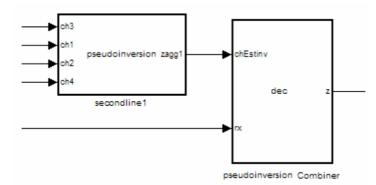

| 6.2.3. Channel pseudo-inversion combiner 4x4 |    |

| 6.2.4. Subtractive combiner 4x4              |    |

| 7. Simulink implementation.                  |    |

| 7.1. WMAN system and settings.               |    |

| 7.2. MIMO 2x2.                               |    |

| 7.3. MISO 4x1 and MIMO 4x4                   |    |

| 7.4. Simulation and discussion               |    |

# Part I

# Analysis

# **1. Introduction**

#### 1.1. Context

In the last twenty years the concept of distance has changed in many fields, talking about depth perception and not in the physical sense, of course. That can mean how far the people feel in term of humanistic relationship and in this field the communication is one of the main factors. The technology provided the media to realize this improvement, through new structures which allowed to communicate almost anywhere, at everytime and with anyone [1]. More precisely these technical supports can be classified as wireless communication.

Today, the wireless communications support many applications, such as satellites, intercontinental, middle-frequency and local connections. Focusing on the last, the local communication, it is well note that the wireless is applied capillarly, at the end of the network. This because the wireless channel is more restrictive respect to the cable connection [13], so shorter the distance between antennas, higher the data-rate allowed. In this direction have been developed local and metropolitan wireless systems, WLAN and WMAN respectively. These networks provide high bit-rate in order to satisfy the functionalities of the lastgeneration devices, where the key word is convergence of services: cellular phone, GPS, TV and computer.

A technique largely used in the wireless communication is the OFDM (Orthogonal Frequency Division Multiplexing), which supports the WLAN IEEE 802.11a, g, n, HIPERLAN, DVB-T, DVB-H, UMTS generation, WiMAX IEEE 802.16 and many others. These examples show that the OFDM is employed in most of the last telecommunication systems, explored and improved in all its parts. That is the why the actual research tries to mix other technique with the OFDM, to speed up the two main requirements of high bit-rate and low probability of errors.

In this direction, applying the diversity principles to the OFDM digital multi-carrier modulation is certanly one of the future perspective. The word diversity, in telecommunication, means MIMO systems, that is transmitting the signals through multiple antennas (Multiple Input Multiple Output), and it can be performed in various domains, such as space and time. Thanks to MIMOs (i.e. Spatial Multiplexing, Space-Time Coding) is possible to increase the bit-rate maintaining the same implementation constraints, as transitting power and bandwidth availability. These diversity techniques exploit the redundant transmission of data on the various antennas, allowing the decoding at the receiption by precise algorithms.

## **1.2. Problem definition**

Considering the already existing MIMO applications:

"what type of algorithmic improvements can be used to increase the spectral efficiency of an OFDM/MIMO receiver, while maintaining its HW feasibility?"

#### **1.3. Report structure**

The report is organized in three main parts, identified by Analysis, Design and Evaluation. The first part starts with the introduction chapter, that contains this project context, and it focuses on the problem statement. It follows the chapter concerning the methodologies and methods. In this, a comparison between various methodologies is reported, with the final choise for Rugby Meta-Model [4], [6]. The third chapter consists in the theoretical overview related to this project, with sub-sections on OFDM and MIMOs.

The second part is the Design and is divided in steps following Rugby Meta-Model. The initial idea presents the proposed solution for this project. Chapter 5 indicates the cost function and the other constraints. The sixth chapter contains the system analysis and proposes two new algorithms for QO-MIMO receivers. The following chapter illustrates the Simulink implementation of the proposed techniques. Chapter 8 focuses on one of these techniques reporting the development of the System Generation implementation. Finally, Chapter 9 treats the hardware implementation by a co-simulation point of view.

The last part, Evaluation, starts with the Results chapter. It contains the presentation and the discussion on the partial and final simulations. Moreover it treats the SW/HW cosimulation using the target FPGA. Chapter 11 is the conclusion and the proposed future implementation starting from the work done in this project.

# 2. Models and Methodologies

In this chapter a short description of some models and methodologies is done. This because developing a project by following a certain structure is useful, when it is multitasking and complex. Dividing the work in activities and sub-task allows a better organization during the implementation and gives an indication on the eventual delays in the project. Moreover, through various domains, it is possible to describe and classify the implementation steps.

The first part of this chapter treats the A<sup>3</sup> Model [2] and the fitting to this project. The second part reports some methodologies with a final comparison and following choice for this application.

## **2.1.** *A*<sup>3</sup> Model

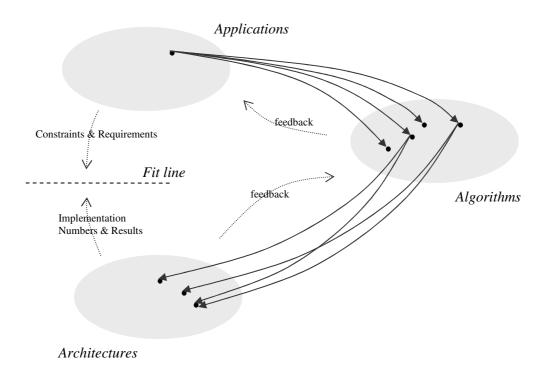

The  $A^3$  Model is a paradigm conceived at Aalborg University [2], developed for electronic system design. The main purpose of the  $A^3$  model is to give a first structure and a trajectory to the project that is going to be implemented, by the classification in three domains of the requirements and the developing environment. As shown in Figure 2.1 for a generic diagram, these three domains are *Applications*, *Algorithms* and *Architectures*, which give the name  $A^3$  to this paradigm.

Figure 2.1: A generic sheme of A<sup>3</sup> paradigm, composed by the three domains: Applications, Algorithms and Architectures. The relations between them converge to a Fit line, inspired by the figure in slide 3 [2].

Starting from the application that has to be implemented, the model allows to connect it to one or more algorithms by applying linear or non-linear signal processing [2]. The second step is to modify the applications in relation to eventually troubles or unfeasibility, that could

mean adding some constraints. After that, the model shows possible architectural solutions for the algorithms, which can be more than one as for the first case, so finally it can lead to a large design space [2]. This phase is processed by HW-SW codesign and architecture exploration [2]. Analyzing the various point in the *Architectures* domain, there is a feedback to the previous *Algorithms* for the validation.

After the implementation, verifying the results is necessary, so as seen in Figure 2.1, the  $A^3$  Model inspects if the final tests respect the initial constraints and satisfy the requirements. This take place on the *Fit line*.

Note that the various  $A^3$  domains can be subdivided in sets which are defined by the target constraints, such as hardware platforms, in case of *Architectures*, or recursive functions for *Algorithms* (this concept is better shown in Figure 2.2).

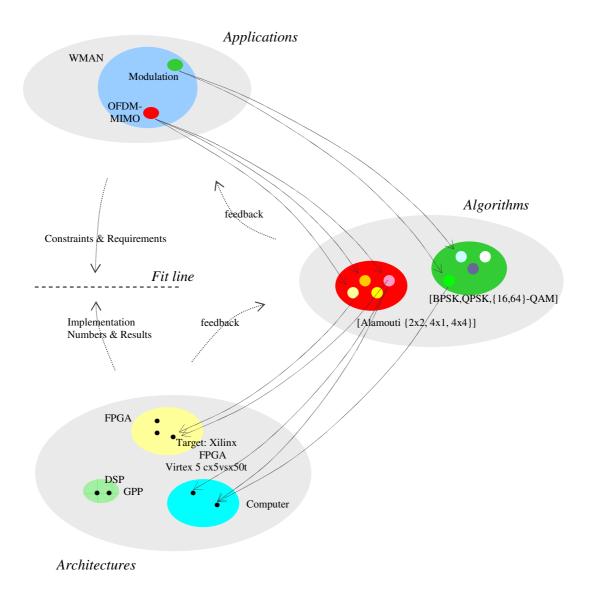

Applying the  $A^3$  Model to this project, the scheme in Figure 2.2 is obtained. The initial idea is to implement a wireless system based on the IEEE 802.16 standard, a Wireless Metropolitan Area Network (WMAN), the Worldwide Interoperability for Microwave Access (WiMAX). In particular the project focuses on the physical link, by the insertion of a MIMO system in the original OFDM scheme in order to speed up the bit-rate and to reduce the probability of errors.

Figure 2.2: A<sup>3</sup> Paradigm applied to this project. The scheme shows the relations between the three domains and the high level possible solutions.

The second domain, *Algorithms*, shows the different modulations that the physical link must support and on the other hand the types of MIMO that should be implemented. Note that the transmitting Alamouti mode is an initial constraint. The algorithms MISO 2x1 (with two transmitting and one receiving antennas) is provided as basis by [24] and [26], and the purpose of the project is to implement other, more advanced, MIMO modes such as the 2x2 and the so-called extended-MIMOs 4x1 and 4x4.

The *Architectures* domain points out the possible hardware solutions, with the constraint target Xilinx Virtex 5 FPGA cx5vsx50t, but note that the scheme indicates other possible HW devices. This because doing a high level estimation on the computational complexity, results impossible to implement all the WiMAX and MIMO physical layer on the FPGA indicated, which features are well-known. At this initial phase of the project, the purpose is to start by implementing just the MIMO algorithm on FPGA and study the feasibility to add other parts. Eventually replace the target FPGA with a DSP more powerful.

#### 2.2. Y-Chart Methodology

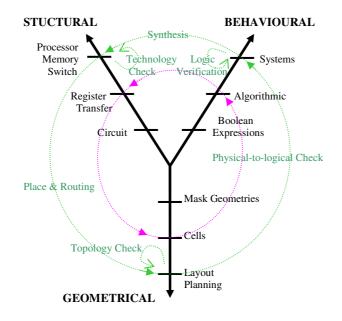

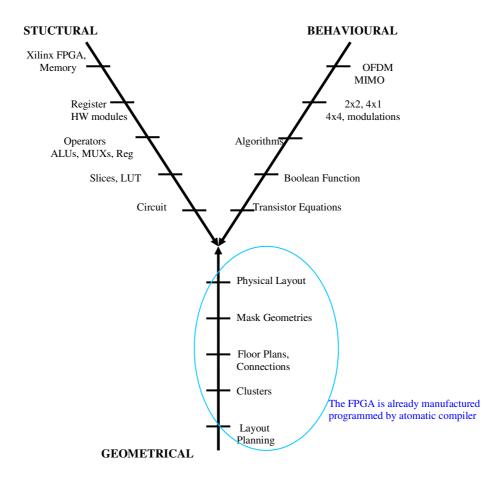

The *Y*-Chart Methodology [3] and [4] has been developed in the 80's, when the numbers of transistors in electronic design, began to be too large to be managed enterly by humans. It gives a top-down guidelines for the VLSI design by a *Y*-shaped structure, as shown in Figure 2.3. The Y-Chart is divided in three domains which are represented by three respective axes, functional, structural and geometrical. Each one is divided in sub-levels.

- *Functional*, is at the highest abstraction level and defines the mathematical expressions in boolean format. This domain does not specify any physical aspect such as computational devices or connections. Note that the *Functional* representation is also called *Behavioural*. This second definition is chosen.

- Structural, is the middle domain which consists in a graphic representation of the expressions defined on the Behavioural axis. By mapping this functions, a group of connected components is obtained. The synthesis is done by considering a cost function, that can contain area, execution time, energy consumption, etc.

- Geometrical, is the lowest level of the methodology, which specifies the physical design considering various constraints as dimension of the electronic components and the wires between them.

Figure 2.3: Y-Chart Methodology, generic representation of the three domains and the respective possible levels. Inspired by Figure 2 [3].

The activity starts from the extreme of the *Behavioural* axis, the designer translates the expressions by using hand or automatic synthesis, obtaining the first step of the *Structural* domain. These actions by connecting archs is represented, creating a circular trend around the *Y*-Chart. Note that at the end of every synthesis, a verification is done, as shown in Figure 2.3.

The *Y*-Chart can be fitted to this project identifying the possible steps on the three domains. The result is the scheme in Figure 2.4, where the various synthesis archs have been omitted for graphical reasons.

Figure 2.4: Y-Chart Methodology adapted to this projec, with the various levels. Inspired by Figure 2 [3] and Figure 1 [4].

The adapted *Y*-*Chart* shown in Figure 2.4 has additional levels on its axes, necessary to split in variouos implementation steps. The first level of the *Behavioural* domain indicates the OFDM-MIMO functionalities, followed by the modulations and the multiple antennas systems, the algorithms which describes the whole system and the lower boolean functions. Finally the transistor physical equations.

The *Structural* domain reports the components at various abstraction levels with the functional connections. Note that the number of unities considered increases towards the center of the Y.

The *Geometrical* representation reports the physical connections at the respectives level of components considered. From the highest level there are Layout Planning, Clusters, Floor Plans, Mask Geometries and Physical Layout. But note that in this project the FPGA is already manufactured and it is programmed through automatic mapping, place & route and bit-stream generation.

## 2.3. ATtACk Methodology

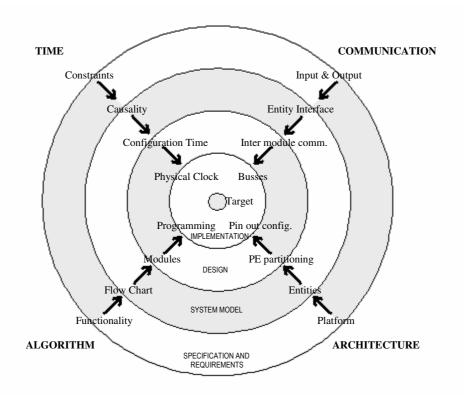

Attack [5] is a methodology based on the Rugby Meta-Model [6], discussed in 2.4, conceived to extend this model to dynamic partially reconfigurable systems on FPGA. The name ATtACk derives from the four domains which compose the methodology: Algorithm, Time, Architecture and Communication. A second flow specifies the four phases, common for each domain: Specification and Requirements, System Model, Design and Implementation. Figure 2.5 shows the methodology graph, with an overview of the domain levels.

Figure 2.5: ATtACk Methodology, a generic case of implementation, with the four domains and four phases. Inspired by Figure 2 [5].

The four domains which compose the Attack methodology are now described.

- Algorithm, specifies the various mathematical expressions and correlations. Note that for the partial reconfiguration these algorithms must be two or more. The first step is to analyze the documentations and background in order to identify the subjects, second translate them to Control Data Flow Graphs (CDFGs) to list the execution steps. By examining the CDFGs it is possible to identify the two modules, static and dynamic, for the partial reconfiguration.

- Architecture, defines the hardware platform where the algorithms have to execute. At first it is necessary to identify the possible device analyzing the various features, as i.e. the FPGA chip, the In/Out ports, memory and interface devices (i.e. ADC/DAC, audio ports, etc.). The second phase is to identify the parts of the platform which compute the algorithms. Third, the FPGA can be divided in static and dynamic areas to perform the eventual partial reconfiguration, so it is necessary to use special tools provided by the FPGA producers, such as PR flow from Xilinx [36].

- *Communication*, treats every signal that transfers data, address and control information, considering the connections and the data format. This domain allows

to identify the links on the platform, inputs and outputs. Second step is to connect the functional blocks having a look on the static and dynamic areas. Finally the platform has to be linked to the testing environment, that could be a tool for cosimulation running on a computer.

• *Time*, treats all the information regarding the execution time of the system at the various abstraction levels. Initially there are generic constraints only, the next level expresses causality between the steps of the CDFG. At the third level the operators and the connections can introduce delays that have to be considered. Finally the delays of the physical components and wires, but also the reconfiguration time to change between dynamic blocks are expressed.

The Attack methodology has been conceived for dynamic partial reconfiguration, but can be adapted to this project, considering that this FPGA's functionality is not used. Figure 2.6 shows a possible fit for this project.

Figure 2.6: ATtACk Methodology applied to this project, with the four domains and an additional phase (Xilinx design) in the design step. Inspired by Figure 2 [5].

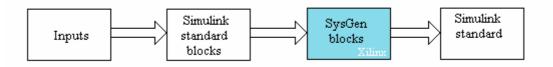

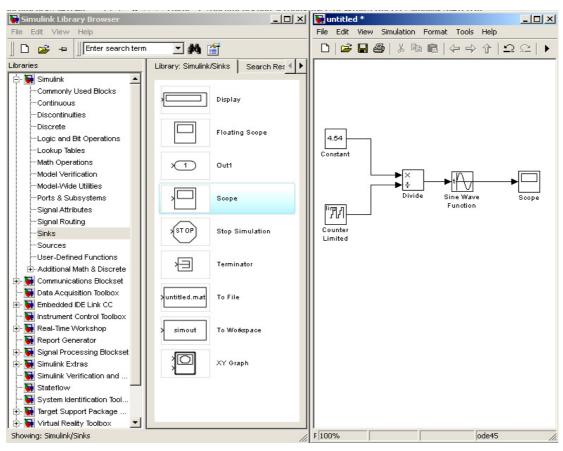

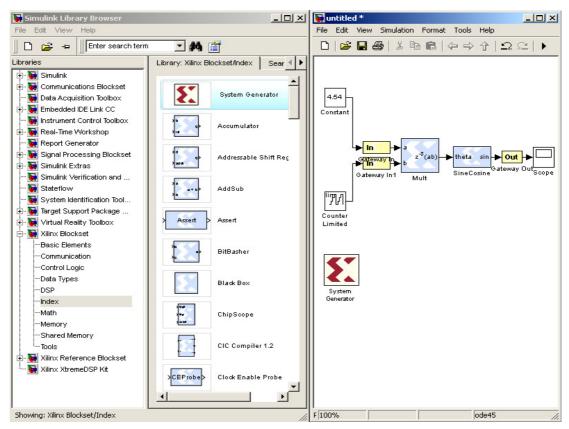

Some part of the scheme shown in Figure 2.5, for this customized version are maintained. As already reported, adapting the Attack methodology to this project requires a modification of the design phase. Figure 2.6 shows that the third phase has been split in two phases, in Figure 2.5, Matlab Simulink design and Xilinx System Generator (SysGen) oriented design. In fact, even if the development environment is the same, Matlab Simulink, the libraries changes, and that means the operators change. In the Simulink Design phase the operators are standard blocks, S-functions and Matlab-functions, and for the following phase the components are Xilinx blocks at lower abstraction level. So, some part of the project scheme have to be translated manually using basic operators.

In Figure 2.6 for the two design phases, the same level on the four domains is shown, but note that both of them can have different Operators, Inter module communications, and Sample Times. On the other hands, the Operations must remain the same.

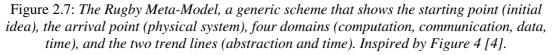

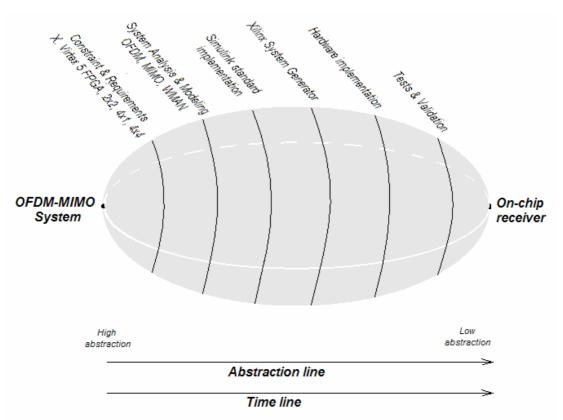

## 2.4. Rugby Meta-Model

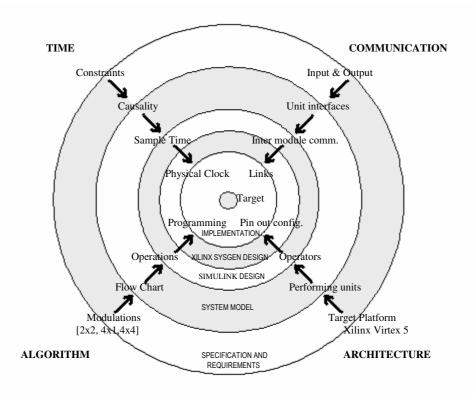

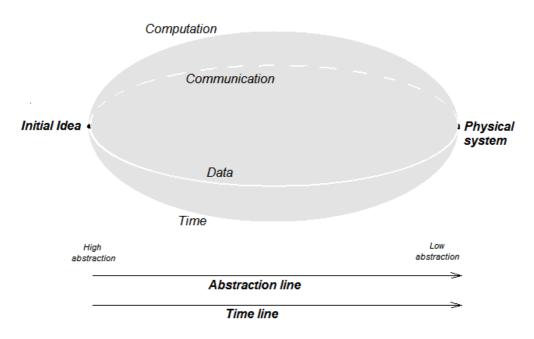

The *Rugby Meta-Model* [4] and [6] is a methodology for electronic system design based on the *Y-Chart* [3] and [4], but it extends the domains in order to manage more complex systems, as those which present hardware and software implementation. Rugby is divided by four domains, Computation, Communication, Data and Time, each split into phases. These phases correspond to different levels of abstraction. The Rugby methodology can consider split or mixed HW/SW implementation, in this report, only the mixed version is explained.

An important comparison between two similar concepts are treated:

- *Hierarchy*, which is the subdivision of the design models in steps. Each step indicates the amount of information used to describe the system, while other details are hidden.

- *Abstraction*, which specifies the models and the semantics used in a project at various steps. These models represent the behaviour of the components used to describe the system, and at each level information are respectively detailed.

While the abstraction levels are pre-defined for every HW/SW implementation, the hierarchy is a designer choice, for instance each abstraction level and domain can represent a hierarchical step. Because of this general concept, *Hierarchy* is not explicitly specified in the *Rugby Meta-Model*.

As already mentioned, Rugby is based on the Y-chart, but is extended in the domains. In fact in this methodology the domains are four instead of three, and treat different fields:

*Computation*, which indicates the mathematical expressions and relations between data inputs and outputs. For each abstraction level, these computations assume different descriptions, which are related to the considered component. For instance at physical level, as the interactions between transistors, resistors, capacities, the computations are differential equations that indicate the behaviour of the electric current in relation to the voltage. Another example, at high abstraction level, is the algorithm that a block can perform considering analog or digital components, as amplifiers or modulators, etc.

- *Communication*, which specifies the links between the various components of the design. These connections can be a functional link between main blocks or, for instance, physical wires from a resistence to the gate of a silicon transistor, considering a very low abstraction level. Moreover, these connections can support various types of information, as controls, data, addresses.

- Data, which reports the types of data and the quantities that are computed. At an intermediate abstraction level, the data can be real or imaginary numbers, defined in time or frequency domain. Considering logical level, data are boolean values, and at transistor level are real numbers which indicate the voltage or other physical quantities.

- *Time*, which indicates the time-relation between components and, as in the others domains, for the various abstraction levels is defined. In fact, every component needs its computation time and every connection its delay, so these behaviours have to be considered in the design. Note that at software level, the causality relation only is treated.

The Rugby Meta-Model can be adapted to this project as for the previously considered methodologies (Attack, Y-Chart). As already indicated, the Rugby mixed HW/SW only is treated, because this project has not split implementation but a sequential software-hardware flow.

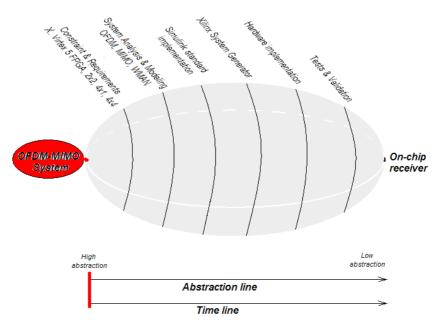

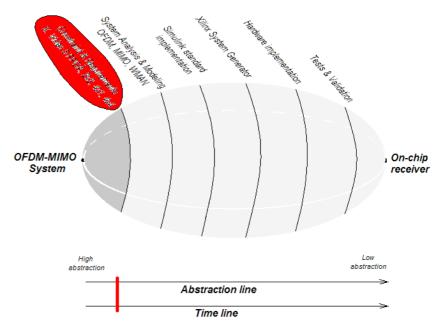

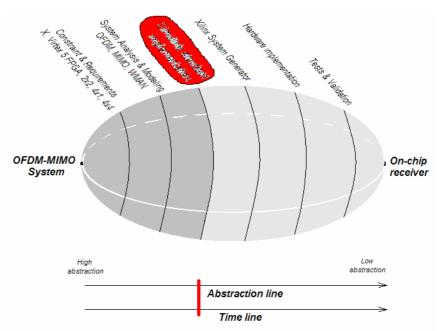

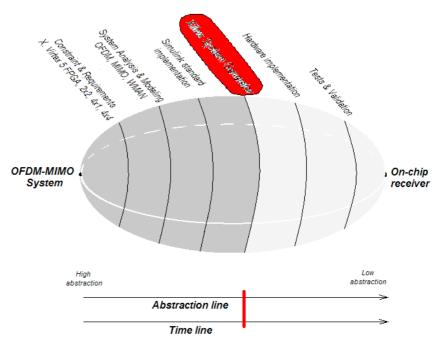

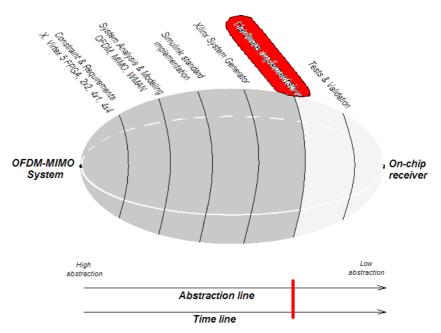

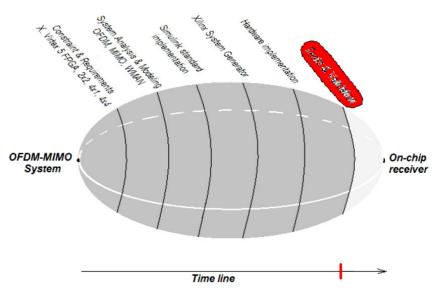

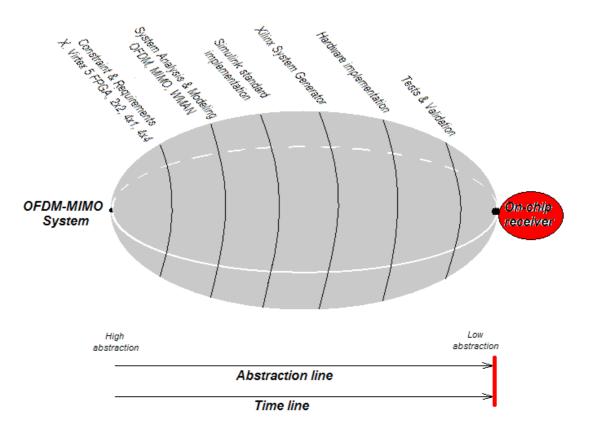

Figure 2.8: Rugby Meta-Model, the scheme adapted for this application. The Abstraction line has been divided in eight levels. Inspired by Figure 4 [4].

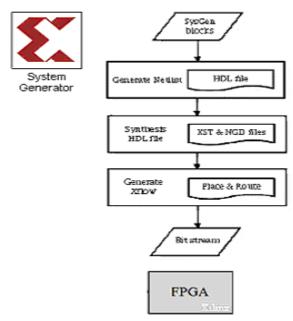

Figure 2.8 represents the scheme of *Rugby* fitted to this project. There is a sub-division of the abstraction line in eight steps, starting from the initial idea to the physical implementation. In *Constraints & Requirements* there is an indication about the main contents, the target Xilinx FPGA and the various SIMO/MIMO schemes. The same goes for *System Analysis & Modeling*, where the main parts of the system are shown. The fourth step consists in the implementation of the system by using the development program Matlab and the grafic tool *Simulink*, with the standard libraries provided by Mathworks. This step has been split from

the following abstraction level called System Generator, because even if the environment used is Simulink, the libraries are provided by Xilinx. Moreover, this second software implementation, has been separated because the components provided are hardwarededicated, meaning that they are operators at a lower abstraction level. By these Xilinx System Generator's blocks it is possible to translate directly the Simulink scheme in VHDL code, so thanks to this powerful compiler, the intermediate steps to the FPGA implementation are automated. Note that the Xilinx System Generator blocks are used just for some parts of the system, in particular on the SIMO/MIMO receiver. Hardware implementation is the step where the system is implemented on the target Xilinx Virtex 5 FPGA, with the simulation environment building for the tests. Before the last On-chip receiver, there is Tests & Validation, which consists in several simulations (or HW/SW co-simulations) to verify the correct behaviour of the hardware system. Moreover, it is possible to compare the delays and the approximation errors due to the difference between software and hardware. In fact very often, a HW implementation requests the use of fixed point operations and bit-limited solutions. Note that in Figure 2.8 the four typical domains of *Rugby* have been omitted for graphic reasons, but they are actually considered in this project.

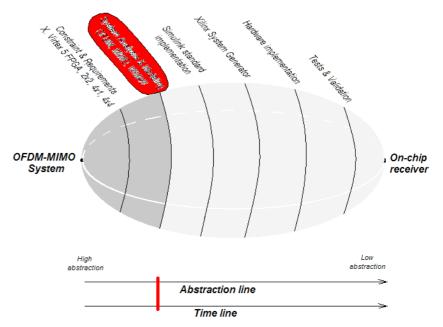

Analyzing in detail the *Rugby* scheme of this project, it is possible to define various steps for the four domains, as done for the *Y*-*Chart* and the *Attack* methodologies. Figure 2.9 represents these intermediate levels on separated lines, in order to extend the Rugby shape, applied to this project.

Figure 2.9: The Rugby Meta-Model's domains fitted to this application. The various steps indicate the details corresponding to the abstraction levels. Inspired by Figure 5 [4].

The four domains defined by the lines in Figure 2.9, report the details considered for the various abstraction levels. Note that the Communication and Data axes indicate main groups, because the number of objects to consider are often very large. This kind of representation on linear axes is simply adaptable in case of HW/SW co-simulations, where the arrow can be split in two parallel lines, to indicate the parallel execution of the implementations.

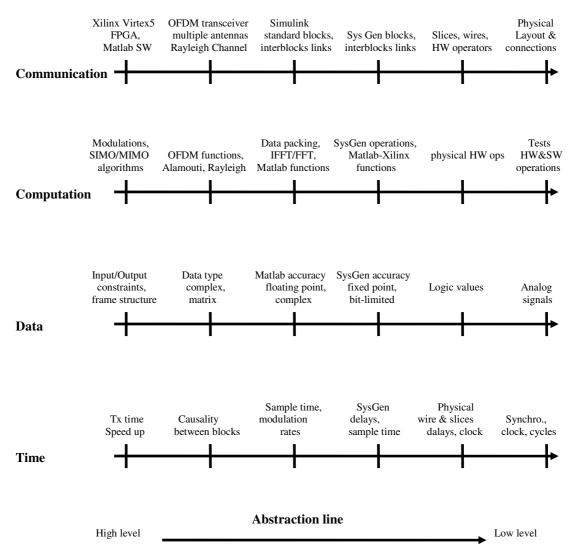

## 2.5. HW and SW Implementations

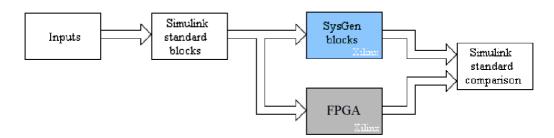

During the development of the project, there are some activities of the methodology that can be extended in sub-tasks, in particular the phases of software and hardware implementation. Figure 2.10 shows a possible strategy for these design steps.

Figure 2.10: The implementation flow graph. Starting from some input data, this strategy allows to implement a system, designing step by step relatively small parts, by checking the results. The final outputs are guaranteed by the last test and the validation. Inspired by [7].

The flow graph in Figure 2.10 represents a possible strategy for the development of the software and hardware steps. The scheme proposed starts with an *Input* tab, which indicates the data that the system must process. An additional phase is also considered, which contains the environment where the implementation must be developed, and the requirements that

characterize the system. The first action is the *Setting* of this developing environment in order to have the easiest implementation flow, which means optimize the project-time. The following step is to build a part of the system, chosen by the designer depending on the application, and then simulate (or test) that. If the result is right, is possible to continue with the eventually other parts of the system, or if the test is wrong the action is the *Errors* correction. Every time the results are right, it is possible to save the implemented part.

The final action is the *Final Test and Validation* of the results considering the initial requirements and constraints. Note that a perfect result of the final test is supposed, because the checking has already done after the last implementation. This is a test just to collect the results for the validation.

#### 2.6. Comparison and discussion

In this chapter three methodologies have been analized and fitted to the development of this project, *Y*-Chart, AttACk and Rugby. In order to choose one of them, a comparison of the main features is performed.

First of all, it is useful to notice that the *Y*-Chart has been conceived in 1983, when the technology had just entered in the computers-era. It means that in these years there was not efficient hardware oriented computer tools as today, so the VLSI design was limited by the technology of that period, the circuits manageable were not too much complicated, as compared to those implemented nowadays. Due to these aspects, the standard *Y*-Chart has been extended for this project in the three typical domains.

However this methodology does not fully satisfy some aspects of the development, as the implementation-trend from software to hardware, but it focuses just on the latter aspect. Moreover, the three domains do not help to represent all the characteristics of a complex system. The conception of Rugby is also due to these reasons [4].

Comparing the various domains, it is possible to denote that the *Behavioural* axis of the *Y-Chart* has similarities with the lower abstraction levels of the *Rugby's Computation* axis, but it also specifies some aspect related to the *Time* domain. The *Structural* axis can be associated to the topology of the design, so to one of the *Communication* steps. Finally, the *Geometrical* axis is very close to the physical layout, located also in *Communication*.

The *Y*-Chart misses an important domain, that is supported by *Rugby*, the *Data* axis, which indicates the structures of the numbers and signals used at the various abstraction levels.

The *ATtACk* methodology is a new concept [5] and it extends *Rugby* to a dynamic partial reconfiguration target; it uses a similar structure but a different shape. Two of the domains have been maintained, *Time* and *Computation* (this just recalled *Algorithm*), but the *Communication* axis of *Rugby* has been split in two: *Communication* and *Architecture*. Note that in *ATtACk*, the *Data* axis can be related to the *Algorithm* domain.

The *ATtACk* methodology could be a good solution for this project, but since the project does not make use of DPR (for which Attack was devised), Rugby has been selected.

Moreover, *Rugby* allow to simply modify the development scheme for a HW/SW vertical co-simulation, that can be considered at the end of this project.

# 3. OFDM & MIMO theory

### 3.1. OFDM systems

#### **3.1.1 Introduction**

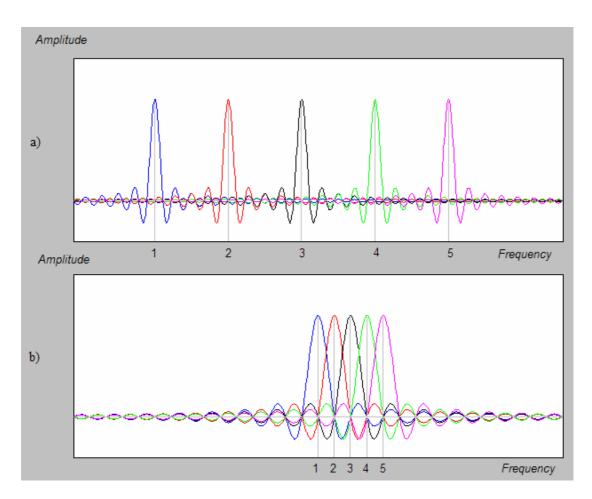

The *Frequency Division Multiplexing* (FDM) [8] is a technique based on the transmission of multiple signals at the same time, over a certain channel, which can be either cable or wireless. As shown in Figure 3.1 a), every signal consists in a modulation of the data with a defined bandwidth range, located at the carrier frequency.

The Orthogonal Frequency Division Multiplexing (OFDM) [8] is a technique based on the spread spectrum concept, which consists in the transmission of the data using a large number of carriers that have precise frequencies. These carriers, in fact, are opportunely spaced to provide orthogonality, as represented in Figure 3.1 b), that means it is possible to demodulate the single components ideally without interferences.

The OFDM is used in many telecommunication applications because its high spectral efficiency, robustness to interference and to the distorsion due to the multipath in case of wireless channel. Some examples of OFDM system are, from [13]:

- DAB-OFDM, which is the technique at the base of the Digital Audio Broadcasting (DAB), a standard for European radio communication.

- ADSL-OFDM, which supports the global Asymmetric Digital Subscriber Line standard, for the fast-Internet connection.

- DVB, Digital Video Broadcasting, which support the various digital television systems.

- 3G cellular phone technology.

- WLAN, Wireless Local Area Networks based on the IEEE 802.11 standard.

- WMAN, Wireless Metropolitan Area Networks, and WiMAX, Worldwide Interoperability for Microwave Access, which are supported by the IEEE 802.16 standard.

- WOFDM, Wideband OFDM, which exploits the bandwidth between channels to erase the frequency errors of the transmission chain.

- Flash OFDM, which uses the concept of fast frequency-hopping spread spectrum.

- MIMO-OFDM, which uses a combination of this technique with multiple antennas systems, as the Broadband Wireless Access (BWA) tipically used in Non-Line-Of-Sight (NLOS) environments.

#### 3.1.2 Multicarrier transmission

The digital linear modulations, such as M-PSK or M-QAM, are typically based on the transmission over a single carrier transmission. Considering a system transmitting data by one of these techniques, on a certain wireless channel, the condition to have no interference between symbols (ISI) is [9]:

$$\tau_m \ll T_s \tag{3.1}$$

where  $\tau_m$  is the delay spread of the channel considered, and  $T_s$  is the duration of the symbol transmitted. In other words, the condition expressed in Formula 3.1 means that the bit rate  $R_b$  of that linear modulation system is limited by the delay spread of the channel.

Figure 3.1: a) *Example of a FDM spectrum with five possible carriers, separated by guard*bands. b) *Example of an OFDM spectrum with the same number of carriers, but disposed respecting the orthogonality.(The group has plotted by Matlab).*

The conception of OFDM derives from this limitation expressed in Formula 3.1. In fact, maintaining the same channel, it is possible to avoid this limit by splitting the data stream in various sub-streams and transmitting them on sub-carriers. Considering K sub-carriers, the duration of the symbol is increased by K, so a bit rate raising of the same factor K is possible. However the number of sub-carriers is limited because the time coherency of the channel must be respected, so the symbol duration must be smaller than the inverse of the maximum Doppler frequency  $v_{max}$  [9]:

$$T_{S} \ll \frac{1}{\nu_{\max}} \tag{3.2}$$

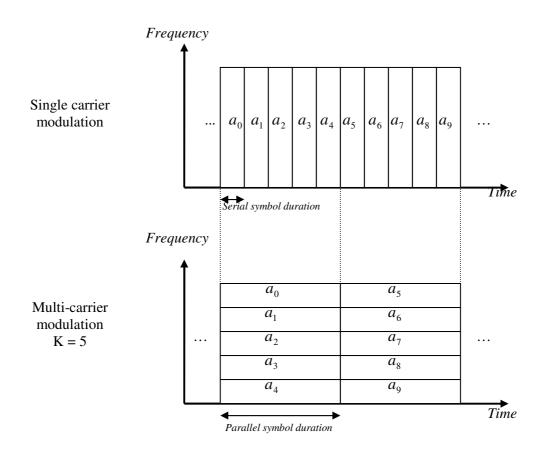

The single carrier transmission can be represented in the time domain as a serial series of sub-streams, while using sub-carriers, a second dimension is treated, the frequency. This relationship is shown in Figure 3.2, for a number of sub-carriers K = 5, where the various serial symbols  $a_i$  are spread on a period of K time  $T_s$ .

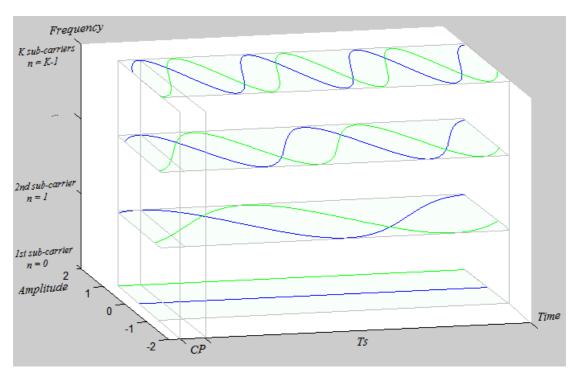

Considering the multi-carrier (OFDM) transmission [10], the symbol is composed by K complex values multiplied by the respective K sub-carriers, which are shown in Figure 3.3. Note that the duration of the symbol is  $T_s$  and CP is the cyclic prefix, a repetition of the signal added to improve the transmission, which is explained in the sub-section 3.1.3.

Figure 3.2: Example of a single carrier and a multiple carrier transission for a K factor = 5. Inspired by Figure 4.1 [9].

Figure 3.3: Example of a baseband OFDM symbol processing for a generic number of subcarries K, where the blue cosine is the real part and the green sine is the imaginary. The symbol is defined in three dimensions, Time, Frequency and Amplitude (normalized to one). Inspired by [10].

Figure 3.3 shows the multiple structure of a baseband OFDM symbol processing, represented in the three dimensions Time, Frequency and Normalized Amplitude. The blue cosine waves are the real part, while the green one is the imaginary part, for the various frequency indicated.

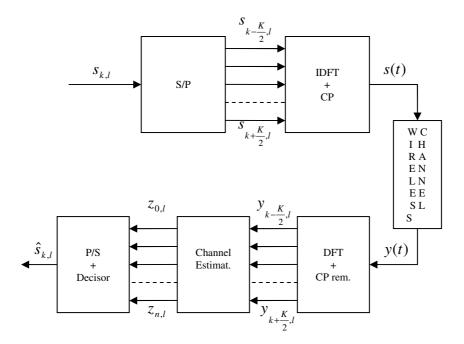

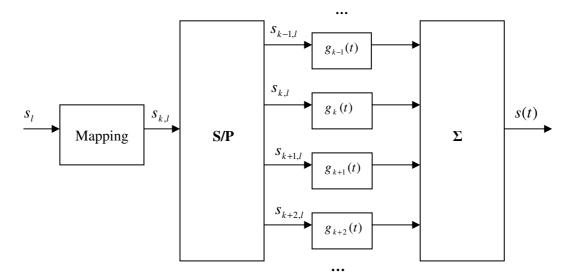

The OFDM system can be represented by the main blocks shown in Figure 3.4. A wireless channel and an arbitrary modulation are assumed.

Figure 3.4: Scheme of a multi-carrier system, the channel is assumed wireless. Inspired by [10] and [11].

The scheme shown in Figure 3.4 is a basic multi-carrier system, where the initial data stream is mapped by an certain arbitrary modulation and then parallelized on *K* sub-channels. These signals are anti-transformed by an *Inverse Discrete Fourier Transform* (IDFT) block, and after that provided by the cyclic prefix. Note that the scheme proposed has not radio-frequency blocks, also because in this report the the baseband equivalent signal is considered.

The channel is assumed a generic wireless, which introduce white Gaussian noise on the signal. At the receiver the cyclic prefix is removed from the signal, which is then transformed by the DFT block in K sub-channels. These partial signals are processed by the channel estimator to allow the decision at the next block, by an algorithm that can be both ideal or not-perfect. The n sub-channels in output from the channel estimator are equal to K plus the number of the channel estimated. Next steps are the serialization and the decision, finally the demapping, which outs the estimated data stream.

Focusing on the transmitting part, there are two modes to implement a multi-carrier transmitter, one which uses K equals filters following by a parallel modulation by carriers with K different frequencies, the second which needs just adjacent bandpass filters connected in parallel. In this report the second solution only is proposed, because this in the real systems is tipically used [9].

The initial data stream is mapped using an arbitrary type of modulation, and then split from serial to parallel by a specific block, as shown in Figure 3.5. Then each sub-channel  $s_{k-i,l}$  (with i = -K/2, ..., K/2) are filtered by a series of bandpass filters with adjacent frequencies. This parallel action is equivalent to perform a Discrete Fourier Transformation, so the signals considered from these blocks are processed in the time domain. The various filters have the following expressions 3.3 [9, page 148],

$$g_k(t) = e^{j2\pi f_k t} g(t)$$

(3.3)

where the base transmit pulse g(t) is shifted in frequency by the esponential function. The pulses obtained  $g_k(t)$  must be orthogonal in frequency (for this scheme) [9] to ensure the recovery of the simbols without ISI,

$$\langle g_{k,l}, g_{k',l'} \rangle = \delta_{kk'} \delta_{ll'}.$$

(3.4)

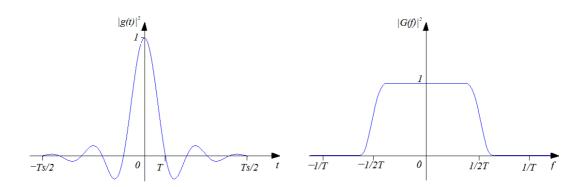

In this case, the shape g(t) has been chosen time limited, then orthogonal in frequency, and the various shifted filters, are called base OFDM pulses. This shapes have  $|g(t)|^2$  equal to a rise-cosine function, with roll-off  $\alpha$ , as indicated in Figure 3.6, with the corresponding transformed.

Figure 3.5: Scheme of a multi-carrier transmitter with a bank of k bandpass filter and mapping by an arbitrary modulation. Inspired by Figure 4.3 [9].

Figure 3.6: Shape of the OFDM pulse, raised-cosine in time domain, and its representation in frequency.

Before the transmission on the channel, the sub-streams are added by obtaining a single baseband signal composed by the K components, as expressed in Formula 3.5 [9].

$$s(t) = \sum_{l} \sum_{k} s_{k,l} g_{k} (t - lT_{s})$$

(3.5)

where the final signal s(t) is a double-addition, in time l and frequency k, of the data streams by the OFDM pulses.

#### **3.1.3 Cyclic prefix as guard interval**

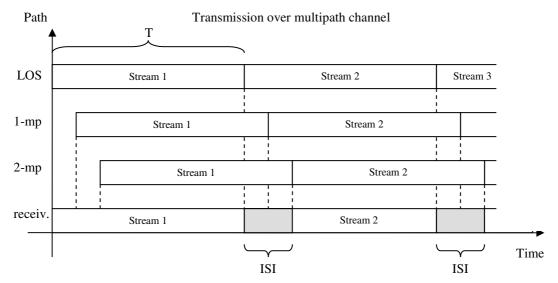

In the scheme of the OFDM system in Figure 3.4, a generic wireless channel has been indicated. If this channel is time dispersive, when a symbol is sent, the communication can be affected by inter-symbol interference (ISI), which is defined as a crosstalk between signals that cover different paths and then present different delays. Considering a multipath fading channel, which is selective in frequency, echo components affect the system as shown in Figure 3.7.

Figure 3.7: Effects of the multipath fading channel over the OFDM transmission, the received signal presents a crossing of paths delayed that introduce ISI.

Figure 3.7 shows the reception of three different paths (indicated on the vertical axis) in the time domain. The first, line-of-sight (LOS) path, allows the reception at a certain time, but the others two paths are longer and they arrive late. The problem is that on the receiving antenna those delays cause the crossing and a part of the symbol is lost.

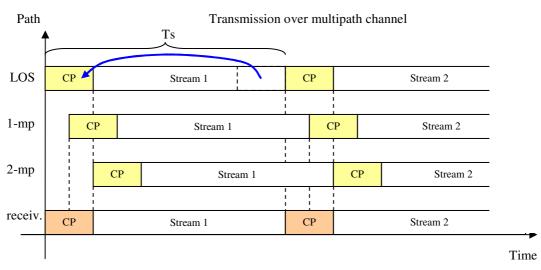

To preserve the synchronization, reduce the effects of the ISI, and then maintain the orthogonality, the idea is to introduce a guard interval to the symbol in the time domain called *cyclic prefix*. This technique consists to reply the last part of the symbol at the beginning. The part replied is usually a fraction of the initial symbol, as for instance 1/4, 1/8, 1/16 or smaller. The benefit of the cyclic prefix introduction is shown in Figure 3.8, where the transmitted streams can be clearly recognized, while the crossing interval is discarded by the post-processing phase. So, after the introduction of guard intervals the symbol received has no crossing between streams, that means no ISI. Note that this approach introduce another benefit, because the cyclic prefix introduces a ciclic convolution, instead of linear, between the transmitted symbol and the channel impulse response. This means to have a scalar multiplication in the frequency domain and the orthogonality is preserved [12].

Anyway, the cyclic prefix introduces the drawback of the reduction of the spectral efficiency, because the symbol is longer than the original, in terms of timing. Note that the bit-rate remains the same.

Figure 3.8: Introduction of the cyclic prefix in the OFDM symbol, these guard intervals prevent the ISI phenomenon.

## 3.2. MIMO systems

#### **3.2.1 Introduction**

In this section an overview of the Multiple Input Multiple Output (MIMO) systems is introduced. Starting from a generic description of those systems and the state of the art, the section continues with an illustration of this project related schemes and algorithms. Note that these mathematical parts.

A MIMO system, where inputs and outputs are referred to the channel, is a particular configuration for wireless communication with the main feature of a transmission over multiple antennas, at both the transmitter and the receiver. The purpose of these systems is to improve the performance, in terms of throughput and link covering, but keeping constant the bandwidth and the transmitting power [13], by applying the concept of diversity, treated ahead in this section. In a few words the diversity exploits the transmission over multiple channels to speed up the reliability when fading is present. The final result is an improvement of the spectral efficiency (bit/sec/Hz) [14].

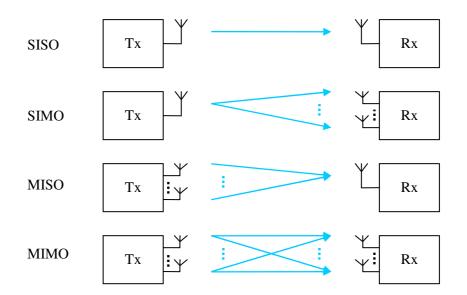

Figure 3.9 shows the four possible combinations with various number of antennas installed on a system with just one transmitter and one receiver.

Since the first prototype of MIMO system using the spatial multiplexing (SM) mode, by the Bell Labs in the 1998, these technology has been exploited in many applications, especially combined with OFDM or OFDMA (Orthogonal Frequency Division Multiple Access). The main standards which use these combinations are IEEE 802.11n WiFi, IEEE 802.16e WiMAX (Worldwide Interoperability for Microwave Access) and the application in the third generation of cellular phones (3GPP) and 3GPP2 [13].

Mainly, there are three modes to implement a MIMO system:

*Precoding*, which is used in case of knowledge of the channel at the receiver, by applying weighted gains to the signal sent.

- *Spatial multiplexing*, which transmit the data split on the multiple antennas, it does not uses any channel knowledge at the transmitter.

- *Diversity Coding*, which does not have any knowledge about the channel at the transmitter, send the data with redundancy in various time and with alternate phases.

In this report, the blind techniques only are considered, focusing on the spatial multiplexing's channel matrix inversion and the space-time block coding.

#### **3.2.2** The concept of diversity

Diversity is a technique to improving the throughput by transmiting data through two or more channels with different features [16]. This multiple channel allows to avoid the degradations introduced by the multipath fading, by transmitting the data streams with repetition, but different phases, so at the receiver is possible to combine these correlated informations. The main types of diversity schemes are [17]:

- *Time diversity*, which consists in the transmitting the same signals at different time consecutively, but with different features (i.e. changing the phase). Note that the concept of time diversity does not include the MIMO.

- *Frequency diversity*, which transmits the signal using various carrier frequencies in order to exploit various channel frequency-slots, or spreading the whole spectrum. A typical example is the OFDM modulation with interleaving and error correction.

- *Space diversity*, which is the transmission of the same data stream on various antennas, then through different channels, and it is strictly related to the MIMO schemes (or multiple-cable connections). Moreover, there are two definition of space diversity depending on the distance of the antennas at the transmitter, which can be pleced on different base-stations or at one wavelength, respectively called macro or microdiversity.

- *Polarization diversity*, which transmits at the same time various versions of the signal on multiple antennas, which are polarized in different mode.

- Multiuser diversity, which transmits the data from a user selected as the best between a certain number of receivers, called opportunistic user. This technique needs a channel estimation at the transmitter, or alternatively at the receiver with a feedback communication.

- *Cooperative diversity*, which sends gained signals depending on the information coming from the distributed antennas which can cooperate to improve the throughput.

Note that in this report the first three types of diversity are considered, in particular relatively to the Space-time block coding MIMO mode, which joins the time and space diversity, and to the OFDM modulation concerning the frequency diversity. In the next sections the MIMO techniques related to this project are expleined, those that, as explained in the chapter "problem analysis", have simpler algorithms in order to reduce the computational load at the receiver.

#### 3.2.3 Spatial multiplexing

In this section an description of a space diversity technique is explained, the spatial multiplexing (SM) [16] and [18]. Note that this modality join the concept of diversity with those of multiple antennas, but just the case of MIMO is treated. This because the basic case of a MISO-SM differs from the MIMO-SM (with the same number of transmitting antennas)

just at the receiver. The peculiarity of the SM mode is the an inversion of the channel matrix to decode the signal, and this computation [16] and [18], is used for the algorithms explained in the implementation.

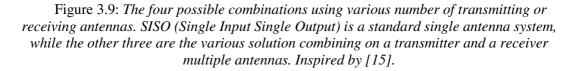

The scheme presented in this section is those shown in Figure 3.10, with two antennas at both the transmitter and the receiver.

Figure 3.10: The scheme of a MIMO system with two antennas at both the transmitter and the receiver, and additional white noise. The stream transmitted are split in two following the Spatial Multiplexing technique.

Figure 3.10 shows a semplified scheme of the system, where the input is a sequence of complex symbols, indicated with X(t), which on the two antennas is split.  $x_i$  and  $x_2$  indicate the two symbols transmitted at the same time interval, while  $y_i$  and  $y_2$  those received. A white Gaussian noise is assumed,  $n_i$  and  $n_2$ ; the channels are noted as  $h_{ij}$ , also complex quantities, where *i* is related to the number of the receiving antenna and *j* the transmitting antenna. The output signal  $\hat{X}(t)$  is an estimation of the transmitted series.

The signals received on the two antennas are a mixture of the transmitted symbols, weighted on the different paths of the channel, added to the noise components. (Some of the following equations for SM mode have been obtained in the algorithm analysis of the first semester project [19]).

$$y_1 = h_{11}x_1 + h_{12}x_2 + n_1$$

$$y_2 = h_{21}x_1 + h_{22}x_2 + n_2$$

(3.9)

where the received symbols  $y_i$  are composed by the addition of the multiplication between the transmitted symbols  $x_j$  and the channel features  $h_{ij}$ , and the nise components  $n_i$ . Moreover, every component of these equations are defined in the complex domain. Assuming that the channel follows a Rayleigh distribution and the noise a Gaussian behaviour, the relative domains are defined as:

$$h_{ij} \mapsto C, \mathcal{N}(0, \sigma_h^2)$$

$n_i \mapsto C, \mathcal{N}(0, \sigma_n^2)$  (3.10)

where *C* means complex domain, and N indicates the normal distribution with mean zero and variance  $\sigma_h^2$  and  $\sigma_n^2$ .

Formula 3.9 can be expressed in matrix notation, compact and extended respectively:

$$Y = H \times X + N \tag{3.11}$$

$$\begin{bmatrix} y_1 \\ y_2 \end{bmatrix} = \begin{bmatrix} h_{11} & h_{12} \\ h_{21} & h_{22} \end{bmatrix} \times \begin{bmatrix} x_1 \\ x_2 \end{bmatrix} + \begin{bmatrix} n_1 \\ n_2 \end{bmatrix}$$

(3.12)

This configuration allows to obtain an estimation of the transmitted symbols, through an inversion of the channel matrix and then to every quantities, as indicated in Formula 3.13:

$$H^{-1}Y = H^{-1}H \times X + H^{-1}N = I \times X + H^{-1}N = X + H^{-1}N$$

(3.13)

The receiver performs these operations obtaining an estimation of the transmitted signal. In fact it is not possible to recover exactly the same number, cause the noise, which is assumed unknown at the receiver.

The decoded values  $(H^{-1}Y)$ , can be represented as  $\tilde{X}$ , because  $\hat{X}$  is the final estimation after the symbol detector, which provides given values respect to the inputs received depending on predefined decision regions [11]:

$$\tilde{X} = X + H^{-1}N = H^{-1}Y \tag{3.14}$$

The channel inversion is defined as in Formula 3.15:

$$H = \begin{bmatrix} h_{11} & h_{12} \\ h_{21} & h_{22} \end{bmatrix} \longrightarrow H^{-1} = \begin{bmatrix} \frac{h_{22}}{\det H} & -\frac{h_{12}}{\det H} \\ -\frac{h_{21}}{\det H} & \frac{h_{11}}{\det H} \end{bmatrix}$$

(3.15)

Substituting Formula 3.15 in 3.14 the result is:

$$\begin{bmatrix} \tilde{x}_1 \\ \tilde{x}_2 \end{bmatrix} = \begin{bmatrix} \frac{h_{22}}{\det H} & -\frac{h_{12}}{\det H} \\ -\frac{h_{21}}{\det H} & \frac{h_{11}}{\det H} \end{bmatrix} \times \begin{bmatrix} y_1 \\ y_2 \end{bmatrix} = \frac{1}{\det H} \begin{bmatrix} h_{22} & -h_{12} \\ -h_{21} & h_{11} \end{bmatrix} \times \begin{bmatrix} y_1 \\ y_2 \end{bmatrix}$$

(3.16)

The decoded Spatial Multiplexing symbols for every time interval are expressed in Formula 3.17:

$$\widetilde{x}_{1} = \frac{1}{h_{11}h_{22} - h_{12}h_{21}} (h_{22}y_{1} - h_{12}y_{2})$$

$$\widetilde{x}_{2} = \frac{1}{h_{11}h_{22} - h_{12}h_{21}} (-h_{21}y_{1} + h_{11}y_{2})$$

(3.17)

#### 3.2.4 Alamouti space-time block coding

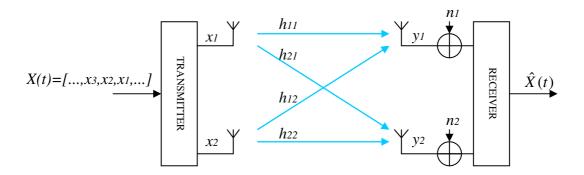

This section is based on the space-time block coding (STBC) technique conceived by Alamouti [20], for the case with two antennas at both the transmitter and the receiver (2x2), in order to make a direct comparison between SM and this MIMO mode.

The STBC is a matching of the time and space diversity concepts, because the symbols are transmitted by splitting the data flow onto the various antennas and repeated at different time instants, but with different versions.

Figure 3.11: The scheme of a MIMO system two by two antennas (2x2), and additional white Gaussian noise. The data in input X(t) are split in two with repetition, but alterning and complex conjugating respect to the first time instant.

The scheme of Figure 3.11 shows the 2x2 MIMO system with STBC mode, where the data in input are split onto two antennas. Note that this block scheme is the semplified version, as for the SM, that does not specify the mapping and demapping of the symbols. The system exploit two time intervals to transmit an information redoundant sequence, because at the first step the top antenna sends  $x_1$  and the bottom antenna  $x_2$ , while at the second time interval the complex conjugated  $-x_2^*$  and  $x_1^*$  respectively. The signals cross the multiple channel *hij*, where *i* receiving antennas and *j* transmitting antennas, and the received sequence is *yin*, where *t* is the time interval. As in the SM scheme, the shown system by a white Gaussian noise on the receiving antennas *nu* is affected, and the estimated information after the symbol detection is  $\hat{X}$ .

The received signals are the combination of the complex products expressed in Formula 3.18 for the two time intervals. (Note that the following equations for the STBC have been taken or inspired by [19], as for the SM case).

$$y_{11} = h_{11}x_1 + h_{12}x_2 + n_{11}$$

$$y_{12} = -h_{11}x_2^* + h_{12}x_1^* + n_{12}$$

$$y_{21} = h_{21}x_1 + h_{22}x_2 + n_{21}$$

$$y_{22} = -h_{21}x_2^* + h_{22}x_1^* + n_{22}$$

(3.18)

where  $y_{ii}$  are the received signals on antenna *i* at the two time intervals and the other quantities are those defined for Figure 3.11. As for the SM case the generic expression in matrix notation is those indicated in Equation 3.19, but the extended version needs a complex conjugation of the lines 2 and 4 of Formula 3.18, so this expression alrady contains these modifications. In fact, to obtain the extended matrix notation, the expressions related to the second time instant must be those shown in Formula 3.20.

$$Y = H \times X + N \tag{3.19}$$

$$y_{12}^{*} = -h_{11}^{*}x_{2} + h_{12}^{*}x_{1} + n_{12}^{*}$$

$$y_{22}^{*} = -h_{21}^{*}x_{2} + h_{22}^{*}x_{1} + n_{22}^{*}$$

(3.20)

In this way, the received signals can be represented in extended matrix notation, in Formula 3.21.

$$\begin{bmatrix} y_{11} \\ y_{12} \\ y_{21} \\ y_{22} \end{bmatrix} = \begin{bmatrix} h_{11} & h_{12} \\ h_{12}^* & -h_{11}^* \\ h_{21} & h_{22} \\ h_{22}^* & -h_{21}^* \end{bmatrix} \times \begin{bmatrix} x_1 \\ x_2 \end{bmatrix} + \begin{bmatrix} n_{11} \\ n_{12} \\ n_{21} \\ n_{22} \end{bmatrix}$$

(3.21)

The decoding system in the STBC technique, instead of an inversion of the channel matrix H, needs a Hermitian transposition, indicated with the symbol  $^{H}$ . It is equivalent to transpose and do a complex conjugation of the matrix, the computation is shown in Formula 3.22.

$$H^{H} = \begin{bmatrix} h_{11} & h_{12} \\ h_{12}^{*} & -h_{11}^{*} \\ h_{21} & h_{22} \\ h_{22}^{*} & -h_{21}^{*} \end{bmatrix}^{H} = \begin{bmatrix} h_{11}^{*} & h_{12} & h_{21}^{*} & h_{22} \\ h_{12}^{*} & -h_{11} & h_{22}^{*} & -h_{21} \end{bmatrix}$$

(3.22)

where the matrix obtained is a 2x4. This operation is performed because it is well note that multiplying a Hermitian of a matrix by the original matrix (Formula 3.23), it is possible to obtain an identity matrix, except a multiplicative constant as indicated in Equation 3.24.

$$H^{H} \times H = \begin{bmatrix} h_{11}^{*} & h_{12} & h_{21}^{*} & h_{22} \\ h_{12}^{*} & -h_{11} & h_{22}^{*} & -h_{21} \end{bmatrix} \times \begin{bmatrix} h_{11}^{*} & h_{12} \\ h_{12}^{*} & -h_{11}^{*} \\ h_{21}^{*} & h_{22} \\ h_{22}^{*} & -h_{21}^{*} \end{bmatrix} = \begin{bmatrix} \left| h_{11} \right|^{2} + \left| h_{12} \right|^{2} + \left| h_{21} \right|^{2} + \left| h_{22} \right|^{2} & 0 \\ 0 & \left| h_{11} \right|^{2} + \left| h_{12} \right|^{2} + \left| h_{22} \right|^{2} \end{bmatrix}$$

(3.23)

assuming  $\alpha = |h_{11}|^2 + |h_{12}|^2 + |h_{21}|^2 + |h_{22}|^2$ ,

$$\frac{1}{\alpha} \cdot \begin{bmatrix} \alpha & 0 \\ 0 & \alpha \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix} = I$$

(3.24)

In this way is possible to split the channel values from the transmitted symbols X, by multipling both sides of Formula 3.19 with the Hermitian channel matrix and the constant  $\alpha$ , as expressed in Equation 3.25:

$$Y = H \times X + N \qquad \Rightarrow \qquad \frac{1}{\alpha} H^{H} Y = \frac{1}{\alpha} H^{H} H X + \frac{1}{\alpha} H^{H} N = X + \frac{1}{\alpha} H^{H} N = \tilde{X}$$

(3.25)

Formula 3.25 gives the decoded values which can be expressed as in Equation 3.26.

$$\widetilde{x}_{1} = \frac{1}{|h_{11}|^{2} + |h_{12}|^{2} + |h_{21}|^{2} + |h_{22}|^{2}} \left(h_{11}^{*}y_{11} + h_{12}y_{12} + h_{21}^{*}y_{21} + h_{22}y_{22}\right)$$

$$\widetilde{x}_{2} = \frac{1}{|h_{11}|^{2} + |h_{12}|^{2} + |h_{21}|^{2} + |h_{22}|^{2}} \left(h_{12}^{*}y_{11} - h_{11}y_{12} + h_{22}^{*}y_{21} - h_{21}y_{22}\right)$$

(3.26)

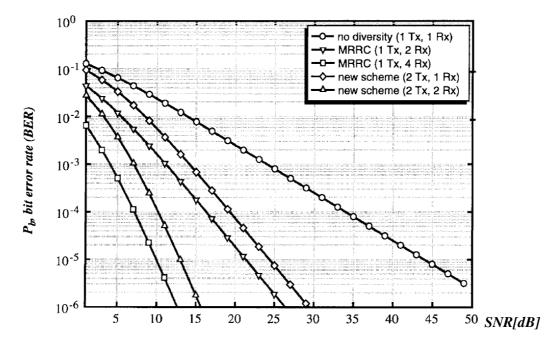

In [20] the Alamouti's STBC mode has been tested and compared with the SISO scheme and the Maximal-Ratio Receive Combining technique (MRRC) [20], which consists in a single transmitting antenna and multiple receiving antennas.

Figure 3.12 shows the benefits of the STBC assuming Rayleigh fading channel transmission and BPSK modulation.

Figure 3.12: The bit error rate (BER) behaviour for various possible values of signal to noise ratio (SNR). Comparison between single and multiple antennas systems transmitting with a coherent BPSK through a Rayleigh fading channel, from [20].

Note that the comparison in Figure 3.12 is done assuming [20] fixed transmission power, Rayleigh fading with mutually uncorrelated amplitudes and ideal channel estimation, which means a perfect knowledge of the channel features at the receiver.

Comparing the various technique it is possible to appreciate the benefit of multiple antennas systems and in particular it is demonstrated that increasing the number of elements (antennas) has a proportional improvement of the channel capacity [13, ch.7]. The Alamouti 2x2 is worse than the MRRC 1x4, but from a practical point of view it is better to have as less antennas on a mobile device as possible, both if the system is composed by transmitter and receiver or by two transceivers.

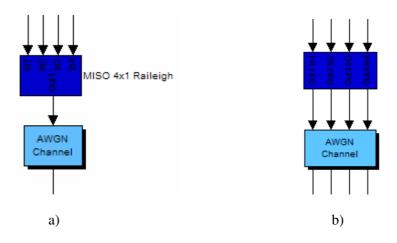

#### 3.2.5 Alamouti STBC 4x1 with Feedback

This section contains the Alamouti STBC technique applied to system with four transmitting antennas, and an antenna at the receiver. The focus is on the transmitting scheme, complicated because a non-orthogonality in the channel matrix calculation. The technique analyzed in [21], [22] and [23] uses a feedback to limit the effects of this non-orthogonality. Note that this branch of the MIMO research has been chosen because very actual and it is the extension of the Alamouti STBC technique which, as indicated in the previous section, is computationally light respect to the benefits it apports to a telecommunication system [20]. This means that can by a possible way to limit the cost function (area, speed, energy, price) in the real applications of mobile systems. Note also that the cases of multiple receiving antennas the computation is the same, except for the channel matrix, moreover the reception aspect of these cases, in the second part called "Design" is treated.

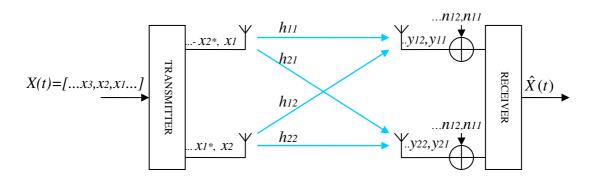

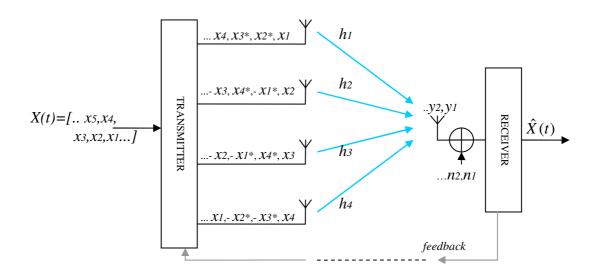

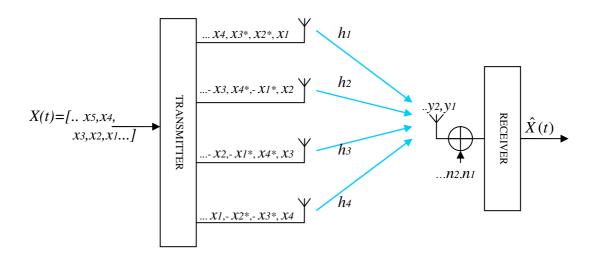

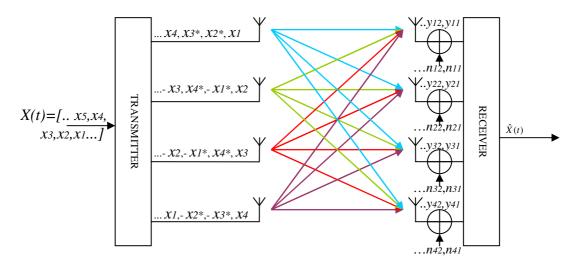

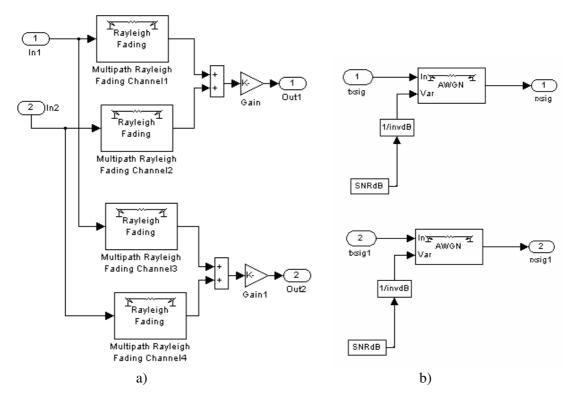

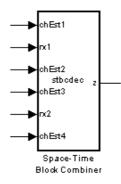

The scheme considered is a STBC-MIMO as those in Figure 3.11, but with four transmitting antennas, so four symbols are transmitted with repetition alternatively on the antennas, with different versions at four time intervals, as shown in Figure 3.13.

Figure 3.13: The scheme of a MIMO 4x1, transmitting in Alamouti mode in four time intervals and feedback. The kind of back transmission is not treated.

As indicated in Figure 3.13, the symbols are transmitted in different versions as in Formula 3.27. Note that this section's formulas are given and inspired by [22].

$$X = \begin{bmatrix} x_1 & x_2 & x_3 & x_4 \\ x_2^* & -x_1^* & x_4^* & -x_3^* \\ x_3^* & x_4^* & -x_1^* & -x_2^* \\ x_4 & -x_3 & -x_2 & x_1 \end{bmatrix}$$

(3.27)

where the columns indicate the symbols transmitted on the antennas, and the rows the time instants. The signal received is those expressed in Formula 3.28, where Y is the matrix with the second and the third rows already complex conjugated.

$$y_{1} = h_{1}x_{1} + h_{2}x_{2} + h_{3}x_{3} + h_{4}x_{4} + n_{1}$$

$$y_{2}^{*} = -h_{2}^{*}x_{1} + h_{1}^{*}x_{2} - h_{4}^{*}x_{3} + h_{3}^{*}x_{4} + n_{2}^{*}$$

$$y_{3}^{*} = -h_{3}^{*}x_{1} - h_{4}^{*}x_{2} + h_{1}^{*}x_{3} + h_{2}^{*}x_{4} + n_{3}^{*}$$

$$y_{4} = h_{4}x_{1} - h_{3}x_{2} - h_{2}x_{3} + h_{1}x_{4} + n_{4}$$

(3.28)

which in matrix notation is those in Formula 3.29.

$$Y = H \times X + N$$

$$\begin{vmatrix} y_{1} \\ y_{2}^{*} \\ y_{3}^{*} \\ y_{4} \end{vmatrix} = \begin{bmatrix} h_{1} & h_{2} & h_{3} & h_{4} \\ -h_{2}^{*} & h_{1}^{*} & -h_{4}^{*} & h_{3}^{*} \\ -h_{3}^{*} & -h_{4}^{*} & h_{1}^{*} & h_{2}^{*} \\ h_{4} & -h_{3} & -h_{2} & h_{1} \end{bmatrix} \times \begin{bmatrix} x_{1} \\ x_{2} \\ x_{3} \\ x_{4} \end{bmatrix} + \begin{bmatrix} n_{1} \\ n_{2}^{*} \\ n_{3}^{*} \\ n_{4} \end{bmatrix}$$

(3.29)

The STBC decoding computes a Hermitian transposition at the receiver, so Expression 3.30 shows this complex conjugation of the transposition of the channel matrix.

$$H^{H} = \begin{bmatrix} h_{1} & h_{2} & h_{3} & h_{4} \\ -h_{2}^{*} & h_{1}^{*} & -h_{4}^{*} & h_{3}^{*} \\ -h_{3}^{*} & -h_{4}^{*} & h_{1}^{*} & h_{2}^{*} \\ h_{4} & -h_{3} & -h_{2} & h_{1} \end{bmatrix}^{H} = \begin{bmatrix} h_{1}^{*} & -h_{2} & -h_{3} & h_{4}^{*} \\ h_{2}^{*} & h_{1} & -h_{4} & -h_{3}^{*} \\ h_{3}^{*} & -h_{4} & h_{1} & -h_{2}^{*} \\ h_{4}^{*} & h_{3} & h_{2} & h_{1}^{*} \end{bmatrix}$$

(3.30)

The purpose of the hermitian channel matrix is to obtain an identity if multiplied by the original H, except a multiplicative factor, but in the cases of MIMO/MISO with thre or more transmitting antennas this multiplication does not give a pure identity, as indicated in Formula 3.31 and 3.32.

$$H^{H} \times H = \begin{bmatrix} h_{1}^{*} & -h_{2} & -h_{3} & h_{4}^{*} \\ h_{2}^{*} & h_{1} & -h_{4} & -h_{3}^{*} \\ h_{3}^{*} & -h_{4} & h_{1} & -h_{2}^{*} \\ h_{4}^{*} & h_{3} & h_{2} & h_{1}^{*} \end{bmatrix} \times \begin{bmatrix} h_{1} & h_{2} & h_{3} & h_{4} \\ -h_{2}^{*} & h_{1}^{*} & -h_{4}^{*} & h_{3}^{*} \\ -h_{3}^{*} & -h_{4}^{*} & h_{1}^{*} & h_{2}^{*} \\ h_{4} & -h_{3} & -h_{2} & h_{1} \end{bmatrix} = \begin{bmatrix} \alpha & 0 & 0 & \beta \\ 0 & \alpha & -\beta & 0 \\ 0 & -\beta & \alpha & 0 \\ \beta & 0 & 0 & \alpha \end{bmatrix}$$

(3.31)

assuming  $\alpha = |h_1|^2 + |h_2|^2 + |h_3|^2 + |h_4|^2$  and  $\beta = 2 \cdot \operatorname{Re}(h_1^* h_4 - h_2 h_3^*)$ .

$$\frac{1}{\alpha}H^{H}H = \begin{bmatrix} 1 & 0 & 0 & \beta/\alpha \\ 0 & 1 & -\beta/\alpha & 0 \\ 0 & -\beta/\alpha & 1 & 0 \\ \beta/\alpha & 0 & 0 & 1 \end{bmatrix} = \tilde{I} \neq I$$

(3.32)

So the decoding processing, by the quantity  $\beta/\alpha$  is affected, and the values are defined in Expression 3.33.

$$\widetilde{X} = \frac{1}{\alpha} H^{H} Y = \frac{1}{\alpha} H^{H} H X + \frac{1}{\alpha} H^{H} N = \widetilde{I} \cdot X + \frac{1}{\alpha} H^{H} N$$

(3.33)

In order to reduce this factor  $\beta/\alpha$ , the technique proposed in [22] provide a calculation of  $\gamma$ , a factor similar to  $\beta$  but with a difference in a sign, in Expression 3.34.

$$\gamma = 2 \cdot \text{Re} \left( -h_1 h_4^* - h_2 h_3^* \right)$$

(3.34)

so comparing the factors  $\beta$  with  $\gamma$ , the smaller value determinates the feedback to send at the transmitter:

- if  $\beta < \gamma$ , the transmitter sends the symbols *X* indicated in Formula 3.27;

- if  $\beta > \gamma$ , the symbols are transmitted in a different version, called  $\underline{X}$  and defined in Formula 3.35.

$$\underline{\underline{X}} = \begin{bmatrix} -x_1 & x_2 & x_3 & x_4 \\ -x_2^* & -x_1^* & x_4^* & -x_3^* \\ -x_3^* & x_4^* & -x_1^* & -x_2^* \\ -x_4 & -x_3 & -x_2 & x_1 \end{bmatrix}$$

(3.35)

The second modality of transmission indicated in Formula 3.35 differs only on the first column respect to *X*, corresponding to the first antenna.

Transmitting one bit in feedback is possible to reduce the interference due to the non othogonality of the channel matrix product, then this technique in the quasi-orthogonal STBC (QO-STBC) is classified [21], [22] and [23].

#### 3.3. WMAN IEEE 802.16

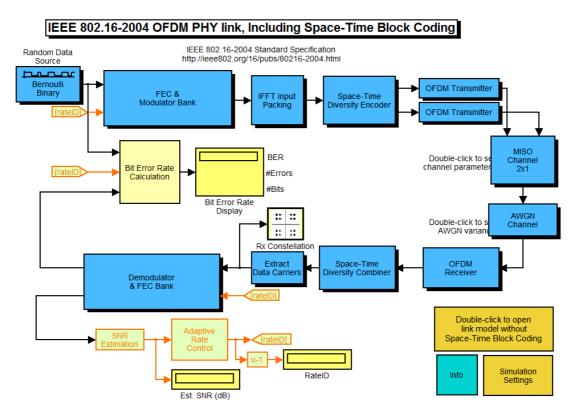

In this section a short description of the physical layer of the IEEE 802.16 with MIMO STBC is given, considering a Matlab Demo implementation [24] and [26].

The IEEE 802.16 is the telecommunication standard on which the Worldwide Interoperability for Microwave Access (WiMAX) [24] and the Wireless Metropolitan Area Network (WMAN) [25], [27] are based. They are wireless technologies which provides high bit rate [24] to the system. In particular this report on the IEEE 802.16d-2004 is focused, even if there are other versions later, as the last IEEE802.16i [25] which is more advanced. This choice because those versions treat the multiple access (OFDMA), not considered in this project.

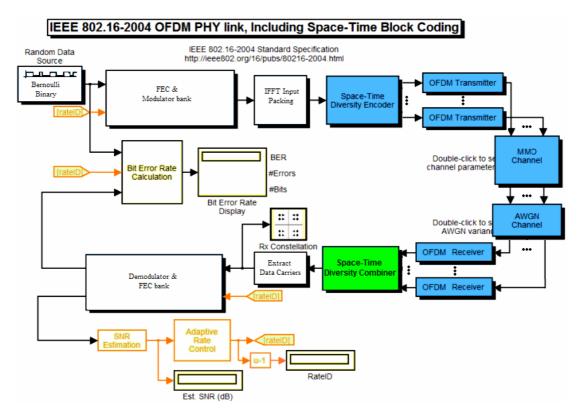

Figure 3.14 shows the scheme of the Simulink implementation of the Standard IEEE 802.16d [24] and [26], which transmit using an OFDM modulation and a MISO 2x1 system. Note that the work proposed in the next chapters, is based on this scheme, in particular focusing on the multiple antenna section.

Figure 3.14: The Simulink scheme of the IEEE 802.16d Standard with STBC-MISO 2x1. On the top in blue the input data source and the transmitter blocks are shown, on the right the multiple channel (MISO) affected by Additive White Gaussian Noise (AWGN); on the bottom the receiver. Image from [24] and [26].

Figure 3.14 shows the WMAN Physical Layer Simulink implementation for the standard IEEE 802.16d [24] and [26], where the blue blocks represent the architecture of the transmission system, the light green the system to manage the modulations and the Forward Error Correction (FEC). In yellow the displays (SNR, BER, number of errors and transmitted bits) and in brown the setting blocks. On the top there are the data source and the transmitter, on the right the channel MISO model with an Additive White Gaussian Noise AWGN, finally on the bottom the receiver. Note that in this model the communication works with the equivalent baseband, because the Radio Frequency (RF) implementation needs more powerful test environments than Matlab Simulink.

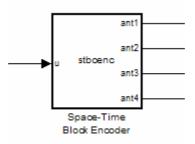

The transmission chain is composed by:

- Random Data Source, which provide random bit in input that simulate the downlink of the WMAN system. It generates bursts consisting of a certain number of OFDM symbols.

- *Forward Error Correction (FEC)*, which is developed by a convolutional code (CC) inside a Reed-Solomon code (RS).

- Data interleaver, which associates the coding to a certain number of subcarriers.

- Modulation bank, which by BPSK, QPSK, 16-QAM and 64-QAM modulations schemes is composed.

- *OFDM transmission*, using 192 sub-carriers, 8 pilots signals, 256-point Fast Fourier Transforms and cyclic prefix that can be changed in the length.

- Space-Time Block Coding, which uses the Alamouti transmission scheme.

- *Burst preamble*, which is composed by a preamble long a single OFDM symbol. This symbol preamble is trasmitted from both the antennas.

- MISO fading channel, which follows a Rice behaviour and with AWGN. In this way it is possible to decode by STBC.

- *Diversity combiner*, at the receiver allows the OFDM demodulation and the channel estiamtion by using the preambles.

• STBC demodulator, deinterleaver, Viterbi and Reed-Solomon decoders.

The scheme provides an estimation SNR implemented by an adaptive rate control, which can vary dynamically the modulation depending on the condition of the channel. The various possible modulations are those indicated in Table 3.1.

| RateID | Modulation and RS-CC rate |

|--------|---------------------------|

| 0      | BPSK 1/2                  |

| 1      | QPSK 1/2                  |

| 2      | QPSK 3/4                  |

| 3      | 16-QAM 1/2                |

| 4      | 16-QAM 3/4                |

| 5      | 64-QAM 2/3                |

| 6      | 64-QAM 3/4                |

Table 3.1: The modulations and RS-CC rates possible, with the relative RateID, from [24]and [26].

## Part II

# Design

Figure 4.0: The Rugby Meta-model adapted to this report, the inital idea.

## 4. Initial Idea

In this chapter the initial point of the project is explained. The idea, in fact, is the first step emphasized on the Rugby methodology scheme shown in Figure 4.0, and it consists in a mixing between OFDM and MIMO systems. The four domains are defined as:

- *Computation:* algorithms of MIMO modes, FFT and OFDM calculations.

- *Communication*: Matlab and hardware implementation.

- *Data*: transmission of OFDM symbols on multiple channel.

- Time: not specified.

Note that the list is not detailed because the initial idea does not require specific information about the system to implement, especially in the time domain.

The idea is at the beginning of the Time and Abstraction lines as indicated in Figure 4.0, that means the first step of the project working on the highest abstraction level.

Chapter 4 contains two sections, the initial problem, which indicates a short comment about the state of the art with the question at the base of the project, and second the solution proposed to answer at this request.

#### 4.1. The problem

The lasts WiMAX systems are already based on multiple antennas communication, and in particular using the Spatial Multiplexing mode, as indicated in section 3.3. Starting from these real systems and from the prototypes implemented in the last years, the researchers try to propose new solutions which can improve the features, in particular speed up the throughput. The purpose of the project described in this report is to propose a new architecture combining existing technique, studing the feasibility and analizing the partial results in order to obtain a hardware implementation. So the development flow must answer to a question:

"what type of algorithmic improvements can be used to increase the spectral efficiency of an OFDM/MIMO receiver, while maintaining its HW feasibility?"

#### 4.2. Proposed solution

The solution proposed is a combination of OFDM and MIMO systems. Note that this is the first domain of the  $A^3$  model shown in section 2.1. In particular the idea is to use the Alamouti's STBC [20] and the Spatial Multiplexing modes in order to extend these theory to real applications. The work can be divided in two sub-parts :

- Algorithms, where these MIMO and so called extended-MIMO techniques are analyzed, improved and implemented by software. The analysis includes the mathematical computations maintaing various architectural solutions, in order to compare the results obtained by the software simulations and chose the best for the hardware implementation.

- *Architecture*, where the best algorithmic solution chosen is developed, first through software simulators and finally on hardware. The last step is to test and verify the system implemented.

Note that all the precise information about the solution proposed in this section and the developing environment, in the next chapter 5 "Constraints and Requirements" are explained.

Figure 5.0: The Rugby Meta-model adapted to this report, Constraints and Requirements.

## 5. Constraints and Requirements

This chapter contains the starting constraints and requirements of the project. This step consists in the specification of the main limitations and targets as those shown in Figure 5.0, the Xilinx FPGA series Virtex 5 and MISO/MIMO systems 2x2, 4x1 and 4x4. The domains of the Rugby Meta-Model are defined as:

- Computation: algorithms of Alamouti and Spatial Multiplexing and equivalent baseband signals considered. Simulink blocks and Matlab operations are performed.

- Communication: architecture of the system defined as one transmitter and one receiver, with a wireless Rayleigh channel. The main internal blocks of the transmitter are the mapper (for the modulation bank) the MISO/MIMO combinator and the OFDM modulator. The receiver contains the OFDM demodulator, the channel estimator and MISO/MIMO decoder, and the demapping block. The operators are provided by the simulation environment, which is composed by the computer softwares Matlab, Simulink and System Generator for DSP, and the operators/interfaces of the co-simulation test environment, which remain the same but includes the FPGA board.

- Data: transmission by the BPSK, QPSK, 16-QAM and 64-QAM modulations, redoundancy in the transmission provided by the MISO/MIMO modes. The transmitted data are affected by Rayleigh fading and white Gaussian noise. Moreover, at the receiver, there is an error introduced by the channel estimation, which provides not ideal values. Note that there are no indications about the data path of the system.

- *Time*: causality, minimizing the execution time. The transmitter and the receiver are perfectly synchronized.

Note that the list indicated is more detailed but still generic, because at this point it is not possible to define precisely any technical features of the system. Anyway this chapter gives a

global description of the main components, indicating the the abstraction level is step by step reducing as shown in Figure 5.0.

Chapter 5 is divided by three sections. The first contains the cost function, which is an indication on the design trend in terms of metrics, while the second section lists the initial assumptions, adding more details for the system implementation. Finally a short description of the tools used in the project for developing and simulating, after a sub-section about the hardware platform and at the end of the chapter a generic overview on the environment used for the final tests.

#### **5.1.** Cost function

The development of every project must satisfy a number of constraints in order to characterize the design flow and justify the choice during the implementation. Very often, in the field of signal processing, there are many trade-off that force the designer to make choices. In this way, the cost function must be minimized and the constraints fullfilled, a trend that must be followed to obtain a consistent project.

This project case the metrics considered for the cost function are:

- *Execution time*, which indicates the time needed by the system to process its computation. This metric is related to the longest path of the implementation and the working frequency of the hardware platform. The execution time is considered because in a telecomunication system the reactivity is fundamental, especially if the channel features change very often;

- *Area*, which consists in the resources occupation of the system on the hardware. Minimize this parameter is necessary because the hardware components are limited.

$$C = f(t, A) \tag{5.1}$$

In Formula 5.1 the cost function for this project is shown, where *t* is the execution time and *A* is the area. Note that these two metrics are often in a trade-off, so in these cases a choice must be taken. For example, the implementation of an algorithm using an hardware embedded processor can limit the number of resources, because the flow of sequential instructions by the memory-ALU-register architecture, but on the other hand the time needed to perform the computation is high comparing to a parallel execution. This is the case of a FPGA implementation, where the operations can be executed in less time and in parallel, but employing a higher number of resources.

There are also others metrics that can be considered, as price, energy consumption, easiness, that are not directly treated in this project, even if sometimes the choices implicitly include them. So in the report these aspect are discussed.

#### 5.2. Assumptions

A telecommunication wireless system working in a real environment, is affected by noise, multipath fading, and many other degradations with different entity. These imply the engineering method of the environment modeling, which consists in a mathematical semplification of the communication.

In this project the assumptions defined are:

- *OFDM-MISO/MIMO*, which indicates the generic delimitation that the system must include the orthogonal modulation by applying multiple antennas system.

- BPSK, QPSK, 16-QAM, 64-QAM, are the modulations that must be implemented for the pre-mapping of the data, which can be singularly selected depending on

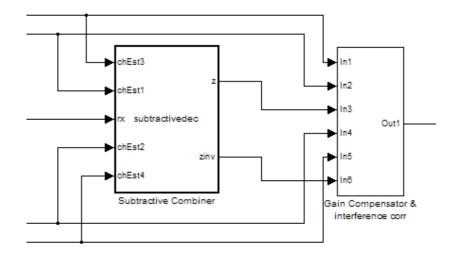

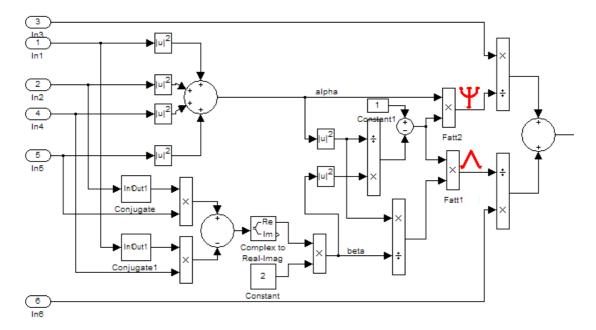

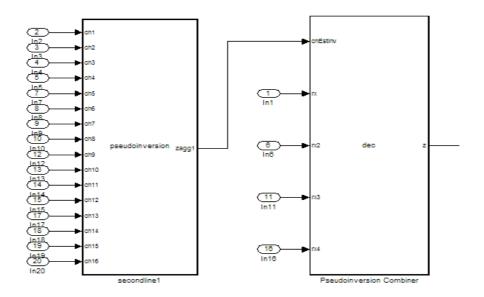

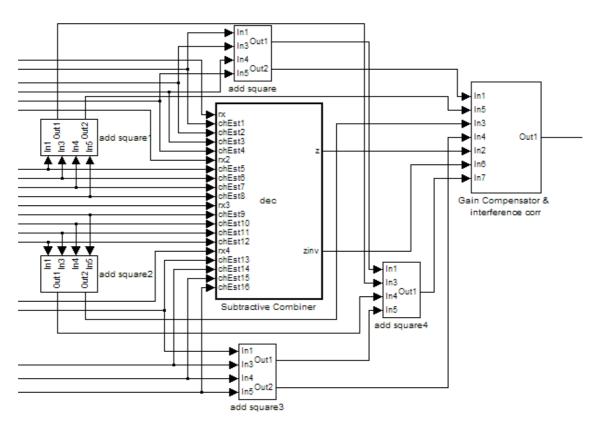

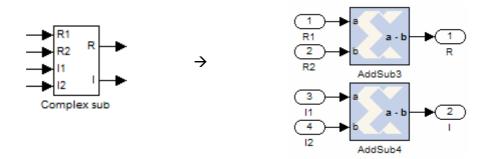

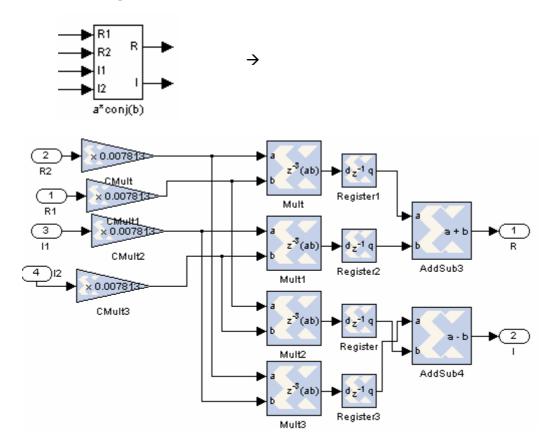

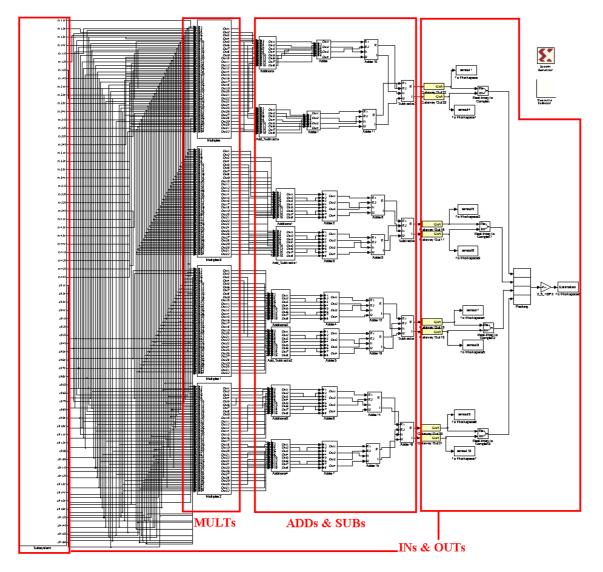

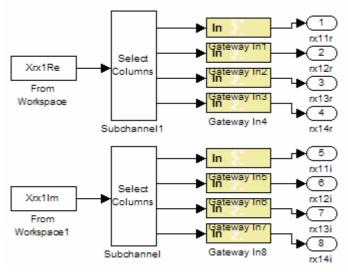

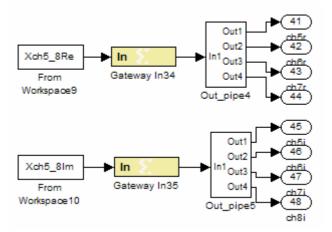

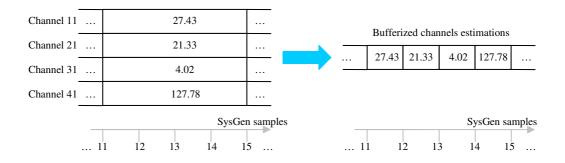

the transmission features (SNR, channel behaviour). In particular the convolutional codes that can be selected for the various modulations are: BPSK  $\frac{1}{2}$ , QPSK  $\frac{1}{2}$ , QPSK  $\frac{3}{4}$ , 16-QAM  $\frac{1}{2}$ , 16-QAM  $\frac{3}{4}$ , 64-QAM  $\frac{2}{3}$ , 64-QAM  $\frac{3}{4}$ .