## INSTITUTE OF ENERGY TECHNOLOGY

# A THREE-LEVEL SPACE VECTOR MODULATION STRATEGY FOR TWO-LEVEL PARALLEL INVERTERS

Conducted by group PED4 1034 Spring Semester, 2009

Title:Control of parallel invertersSemester:10th semseter - Spring 2008Semester theme:Master ThesisProject period:04.02.09 to 03.06.09ECTS:30Supervisor:Stig Munk-Nielsen, Paul Bach ThøgersenProject group:PED4 - 1034

Miłosz Miśkiewicz

Arnstein Johannesen

## SYNOPSIS:

This master thesis presents a threelevel Space Vector Modulation (SVM) for two parallel connected two-level inverters having the dc supply connected through a dc-link. The proposed three-level strategy is compared to two other exsisting modulation strategies for parallel converters; synchronized pulses and interleaved pulses, and to a three-level SVM for the Neutral Point Clamped (NPC) inverter. A down scaled converter setup is realized in the laboratory. Test results from the setup is compared with simulation results and discussed in the report.

Copies:5Pages, total:99Appendix:21Supplements:CD-ROM

By signing this document, both members of the group confirms that they participated in the project work and thereby both members are collectively liable for the content of the report.

ii

#### SUMMARY

This project is continuation of 9th semester project "Control of parallel inverters". In 9th semester project the laboratory test setup has been built, and basic issues connected with system of parallel inverters has been studied.

The main focus of 10th semester project "A THREE-LEVEL SPACE VECTOR MODU-LATION STRATEGY FOR TWO-LEVEL PARALLEL INVERTERS" is put in different kinds of modulation (pulses synchronized, interleaved pulses and proposed three-level SVM) for the system of parallel connected inverters. The project is divided into five chapter. First - Analytical Study presents the mathematical model of the system together with two-level space vector modulation, three-level space vector modulation and threelevel space vector modulation for system of two parallel connected inverters. In this chapter the descripton of three-level NPC inverter is also presented. In next chapter - Simulations, the Matlab/Simulink-PLECS models of the system and NPC inverter are presented. Several measurements have been taken like phase, line-to-line voltages; individual and load currents; dc-link voltage and current. To verify simulation results, the same measurements have been taken in the laboratory. The test setup has been built during 9th semester, and it has been upgraded with new protections (software and hardware) during 10th semester. The DSP program for proposed method has been developed. All the laboratory work is presented in chapter Laboratory experiments. The last chapter - Conclusion contain summary of all gathered data from simulations and laboratory experiments.

The simulation results shows very good performance of proposed modulation method. The Total Harmonic Distortion (THD) of the load current has the smallest value compared to other modulation techniques. Furthermore the voltages are created from the highest number of levels for the proposed method. The laboratory results confirm simulations result only regarding to voltage levels. The THD is the highest value among all methods. This phenomenon can be referred to problem in implementation and hardware.

iv

## Preface

This Master thesis is conducted at The Institute of Energy Technology. It is written by group PED4-1034 during the period from  $2^{st}$  of February to  $03^{th}$  of June 2009. The thesis is a continued 9th semester project, which had the title *Control of parallel inverters*.

The purpose of the Master thesis is to contribute to students' documentation of his/her obtained skills and the level at which he/she is able to exploit these skills in solving a specified task.

## **Reading Instructions**

The bibliography is on page 99. Figures are numbered continuously in their respective chapters. For example Fig.2.3 is the third figure in chapter 2. Equations are numbered in the same way as figures - but they are shown in brackets. Appendices, source codes and documents are attached on a CD-ROM. The contents of the CD-ROM is shown in Appendix H.

This report has been written using the LATEX typesetting system.

#### Acknowledgements

We would like to thank our supervisor Stig Munk-Nielsen, Associate professor at AAU, and co-supervisor Paul Bach Thøgersen, Manager R&D at KK-Electronics, for their cooperation, kindness, patience and time spent with us. We greatly appreciate their help in guiding us in the right direction for continuing the 9th semester project. We would like to thank our fellow students for the time we have spent together in the University. A special thanks goes out to Anca Julean, who started the project with us in 9th semester. Finally we would like send our greatest thanks to our families for their support and patience with us in this very busy period.

The report is conducted by:

Miłosz Miśkiewicz

Arnstein Johannesen

vi

# Contents

| 1 | Intr | oduction                                   | 1  |

|---|------|--------------------------------------------|----|

|   | 1.1  | Background                                 | 1  |

|   | 1.2  | Project motivation                         | 2  |

|   | 1.3  | Project limitation                         | 3  |

|   | 1.4  | Problem formulation                        | 4  |

|   | 1.5  | Overview                                   | 4  |

| 2 | Ana  | lytical study                              | 7  |

|   | 2.1  | Two-level inverter                         | 7  |

|   | 2.2  | Two-level inverters in parallel            | 16 |

|   | 2.3  | Three-level Neutral Point Clamped inverter | 34 |

|   | 2.4  | Conclusion                                 | 37 |

| 3 | Sim  | ulations                                   | 39 |

|   | 3.1  | Simulation constraints and parameters      | 39 |

|   | 3.2  | Simulation models                          | 40 |

|   | 3.3  | Simulation results                         | 49 |

|   | 3.4  | Conclusion                                 | 58 |

| 4 | Lab  | oratory experiments                        | 59 |

|   | 4.1  | Laboratory setup                           | 59 |

|   | 4.2  | Laboratory protections                     | 61 |

|   | 4.3  | Laboratory measurements                    | 63 |

#### **CONTENTS**

|   | 4.4 Conclusion                                        | 71 |

|---|-------------------------------------------------------|----|

| 5 | Conclusions                                           | 73 |

|   | 5.1 Future work                                       | 74 |

| Α | Nomenclature                                          | 77 |

| B | Acronyms                                              | 79 |

| С | Switching Sequence sector I-VI                        | 81 |

| D | Switching states for two parallel two-level inverters | 83 |

| Е | Matlab/Simulink Model Description                     | 85 |

| F | Transformations                                       | 93 |

| G | Thermal description of IGBT                           | 95 |

| Н | Contents of the CD-ROM                                | 99 |

# **List of Figures**

| 1.1  | A Wind Power system with area of interest marked                                                   | 2  |

|------|----------------------------------------------------------------------------------------------------|----|

| 1.2  | The two different topologies                                                                       | 3  |

| 2.1  | Two-level inverter                                                                                 | 7  |

| 2.2  | Waveforms from two-level inverter. $f_{SW}$ =1000Hz $V_{DC}$ =540V $V_{ref}$ =180V                 | 9  |

| 2.3  | Waveforms from two-level inverter. $f_{SW}$ =1000Hz $V_{DC}$ =540V $V_{ref}$ =180V                 | 10 |

| 2.4  | Waveforms from two-level inverter. $f_{SW}$ =1000Hz $V_{DC}$ =540V $V_{ref}$ =180V                 | 11 |

| 2.5  | Different switching states of two level inverter                                                   | 12 |

| 2.6  | Space vector diagram of two level SVM                                                              | 13 |

| 2.7  | $\vec{V_{ref}}$ representation in sector I                                                         | 14 |

| 2.8  | Switching pattern when $\vec{V_{ref}}$ is placed in sector I                                       | 15 |

| 2.9  | Two-level inverters in parallel operation                                                          | 16 |

| 2.10 | Pulses shifted $180^{\circ}$ by shifting carrier waves (Discretised model)                         | 20 |

| 2.11 | $f_{SW}$ =1000Hz $V_{DC}$ =540V $V_{ref}$ =180V $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 22 |

| 2.12 | Three-level representation of two parallel two-level inverters                                     | 23 |

| 2.13 | Phase leg A for state H1                                                                           | 24 |

| 2.14 | Small vector $\vec{V_1}(HOO)$ representation in $\alpha\beta$ plane                                | 26 |

| 2.15 | Medium vector $\vec{V_8}(HPO)$ representation in $\alpha\beta$ plane                               | 26 |

| 2.16 | Large vector $\vec{V_{13}}(POO)$ representation in $\alpha\beta$ plane                             | 27 |

| 2.17 | Space Vector Diagram.                                                                              | 28 |

| 2.18 | $\vec{V_{ref}}$ transition between two sectors                                                     | 28 |

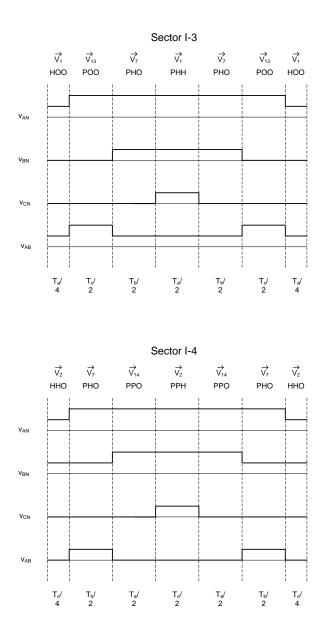

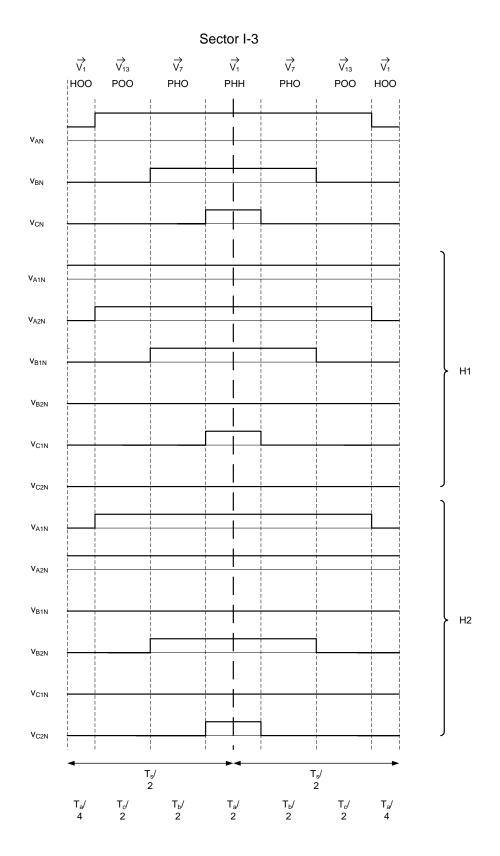

| 2.19 | Switching pattern when $\vec{V_{ref}}$ is placed in sector I region three and four                 | 31 |

#### LIST OF FIGURES

| 2.20 | Switching pattern separated for implementation in system of parallel connected inverters when $\vec{V_{ref}}$ is placed in sector I region three and four. | 33 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.21 | Duty cycles $(D_{B1} \text{ and } D_{B2})$ for system of parallel inverters obtained from duty cycle $(D_B)$ for NPC inverter                              | 34 |

| 2.22 | Three-phase NPC inverter                                                                                                                                   | 35 |

| 2.23 | Waveforms of the NPC inverter. $f_{SW}$ =1000Hz $V_{DC}$ =540V $V_{ref}$ =180V                                                                             | 36 |

| 3.1  | Specification of measurements for the parallel inverter system                                                                                             | 40 |

| 3.2  | Block diagram of two-level SVM                                                                                                                             | 41 |

| 3.3  | Block diagram of three-level SVM                                                                                                                           | 42 |

| 3.4  | Three-level SVM using only H1 state                                                                                                                        | 42 |

| 3.5  | Individual inerters and load A-phase current                                                                                                               | 43 |

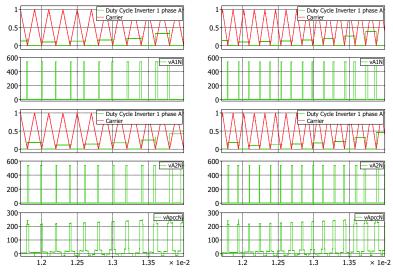

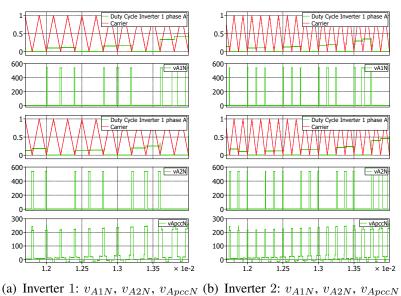

| 3.6  | Three-level SVM with H1 and H2 swapping each other every sampling period; a) $f_{carrier} = 5[kHz]$ , b) $f_{carrier} = 6.7[kHz]$ .                        | 44 |

| 3.7  | Three-level SVM with H1 and H2 swapping each other every two sampling periods; a) $f_{carrier} = 5[kHz]$ , b) $f_{carrier} = 8[kHz]$ .                     | 45 |

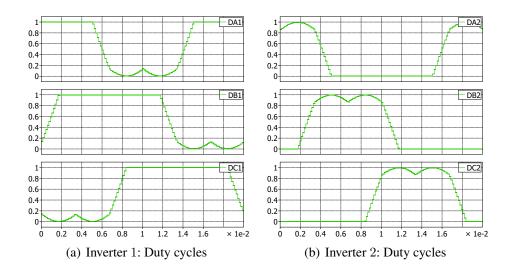

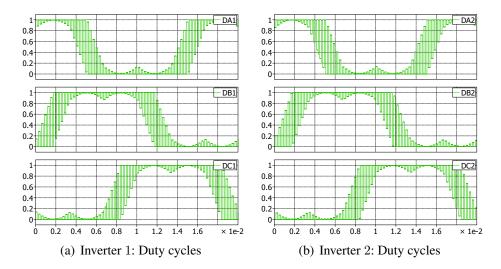

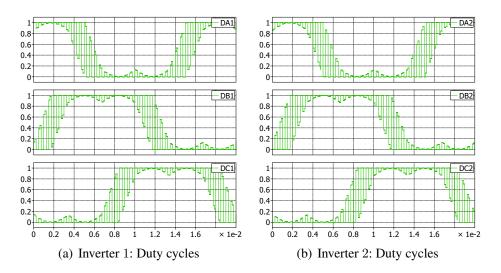

| 3.8  | Duty cycles of modulation technique where only H1 state is utilized for a) inverter 1, b) inverter 2.                                                      | 45 |

| 3.9  | Duty cycles of modulation technique where H1, H2 are swapping every one sampling period for a) inverter 1, b) inverter 2.                                  | 46 |

| 3.10 | Duty cycles of modulation technique where H1, H2 are swapping every two sampling periods for a) inverter 1, b) inverter 2                                  | 46 |

| 3.11 | Modulation for three-level SVM for NPC inverter                                                                                                            | 48 |

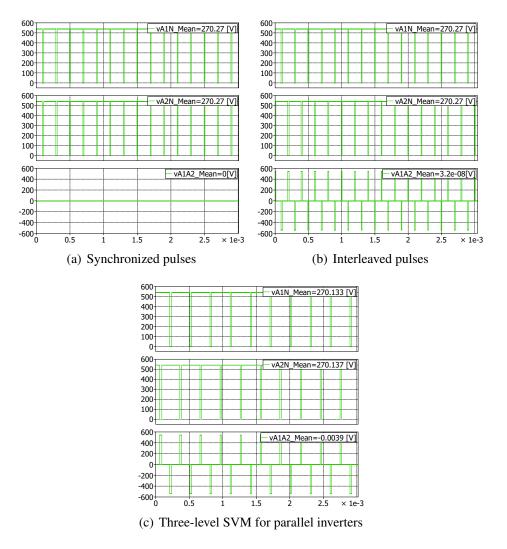

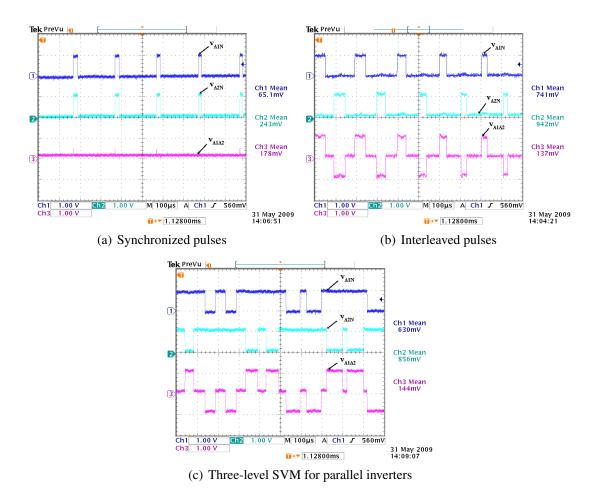

| 3.12 | Comparison of $v_{A1N}$ , $v_{A2N}$ and $v_{A1A2}$                                                                                                         | 49 |

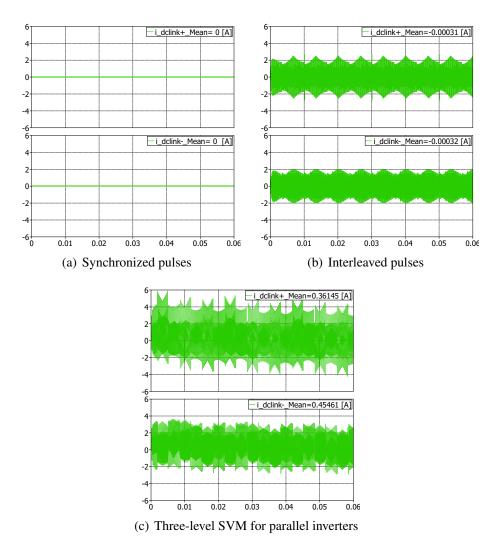

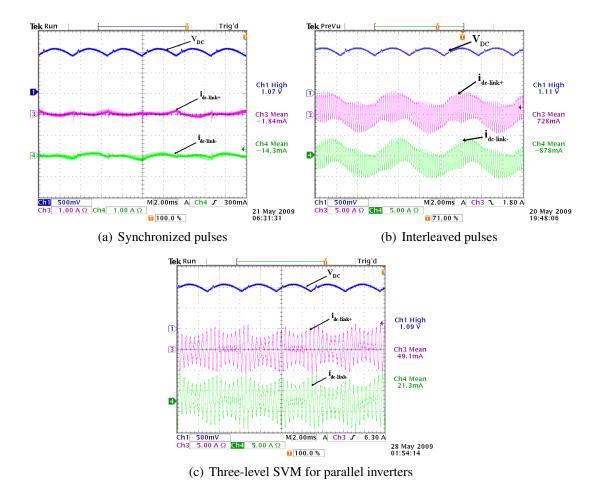

| 3.13 | Comparison of the currents in the dc-link                                                                                                                  | 50 |

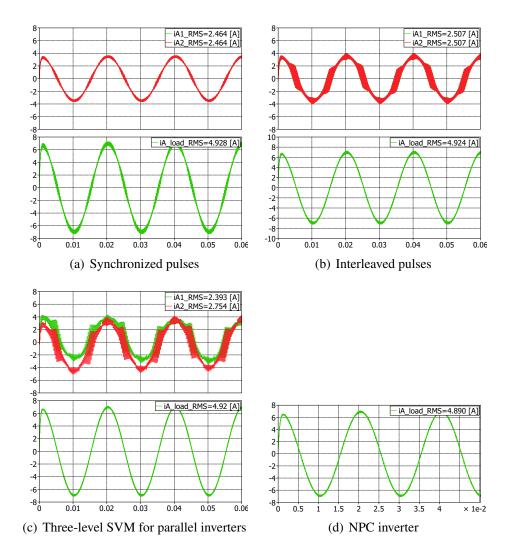

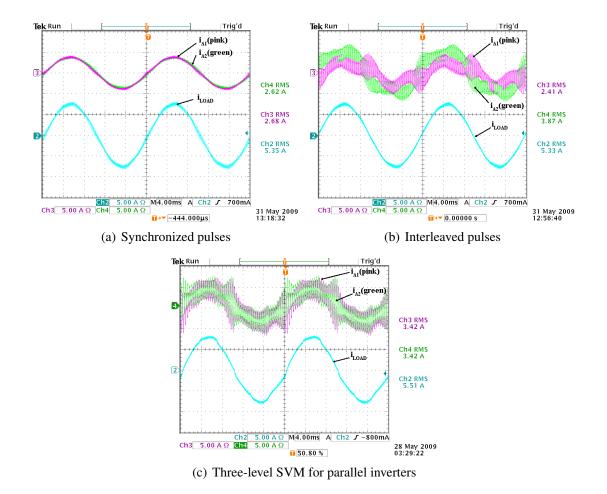

| 3.14 | Comparison of the currents in each inverter and the load current                                                                                           | 51 |

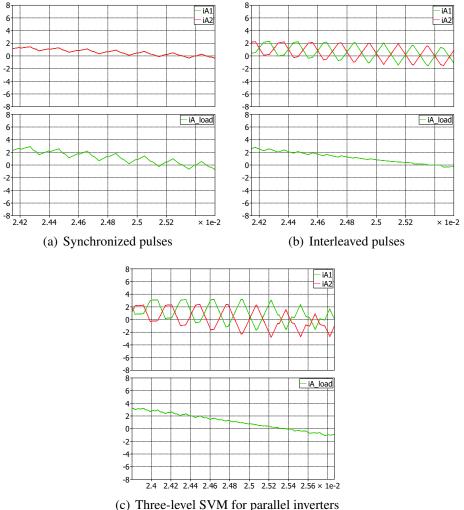

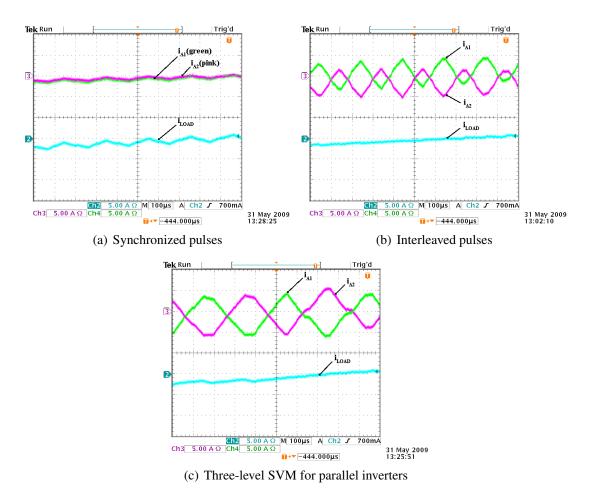

| 3.15 | Zoom of the currents in each inverter and the load current                                                                                                 | 52 |

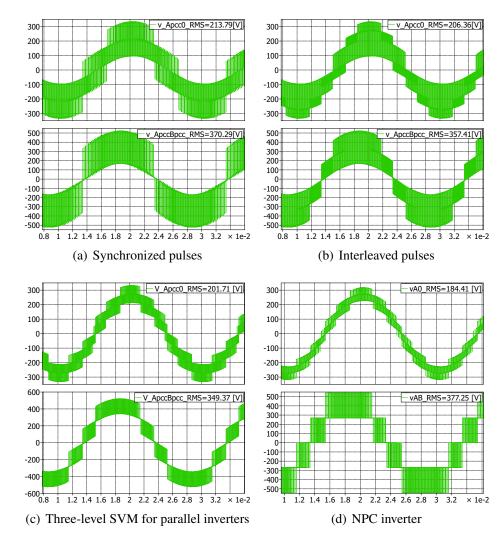

| 3.16 | Comparison of $v_{Apcc0}$ and $v_{ApccBpcc}$                                                                                                               | 53 |

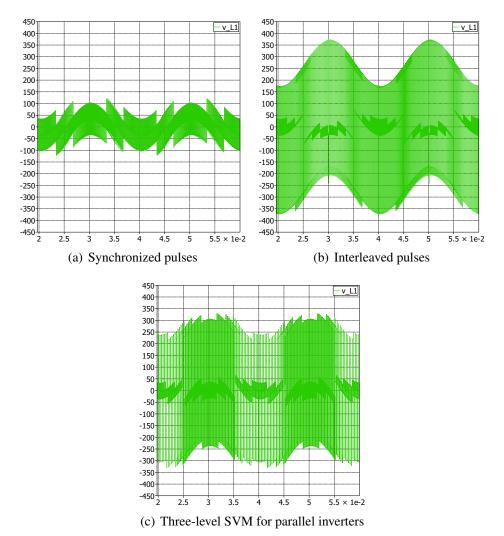

| 3.17 | Comparison of the stresses for sharing reactor L1                                                                                                          | 54 |

| 3.18 | The two different topologies                                                                                                                               | 55 |

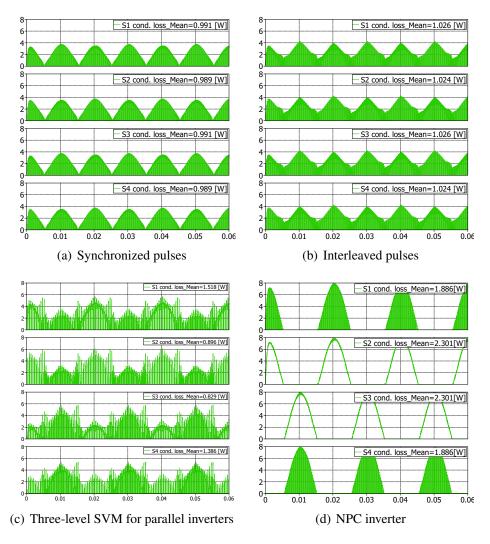

| 3.19 | Conduction losses for the different strategies Leg A                                                                                                       | 56 |

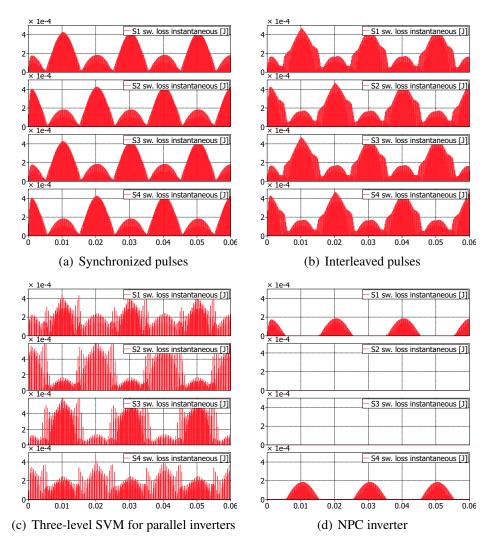

| 3.20 | Switching losses for the different strategies Leg A                                                                                                        | 57 |

#### LIST OF FIGURES

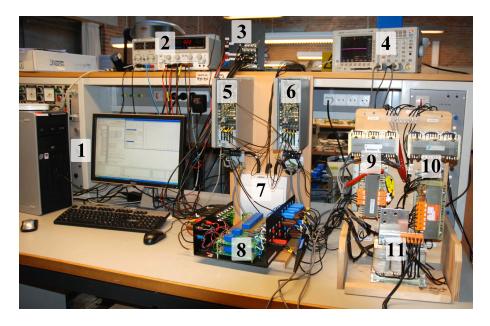

| 4.1  | Picture of test setup in the laboratory                              | 59 |

|------|----------------------------------------------------------------------|----|

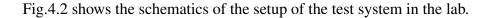

| 4.2  | Schematics of the test setup in the laboratory                       | 60 |

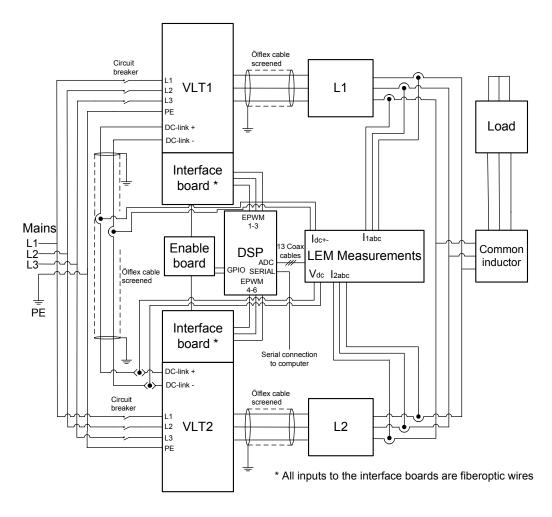

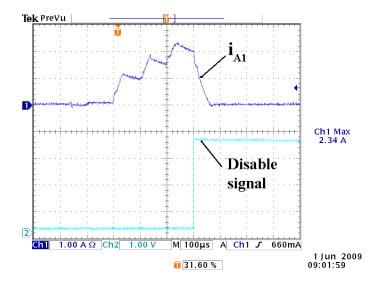

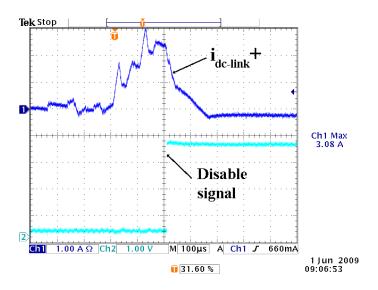

| 4.3  | Overcurrent in individual inverter currents                          | 62 |

| 4.4  | Overcurrent protection in dc-link                                    | 62 |

| 4.5  | Comparison of $v_{A1N}$ , $v_{A2N}$ and $v_{A1A2}$                   | 64 |

| 4.6  | Comparison of the currents in the dc-link and dc-voltage             | 65 |

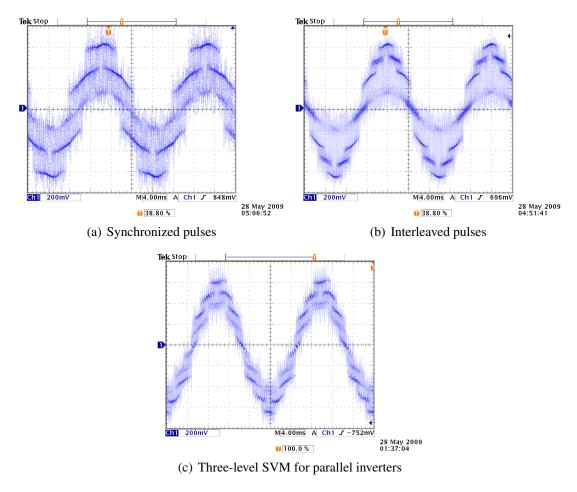

| 4.7  | Comparison of the currents in each inverter and the load current     | 66 |

| 4.8  | Comparison of the currents in each inverter and the load current     | 67 |

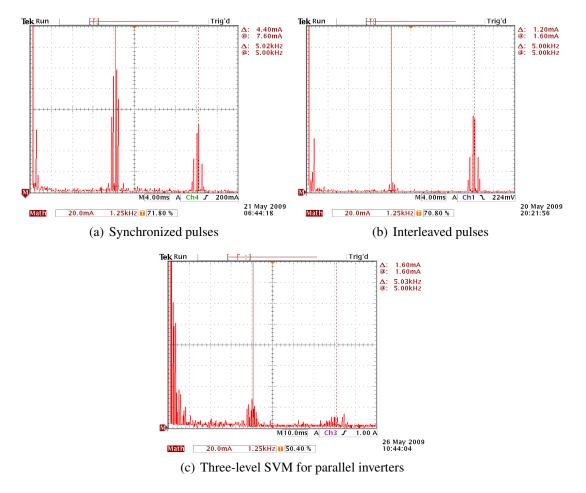

| 4.9  | Harmonic spectrum for different kind of modulation                   | 68 |

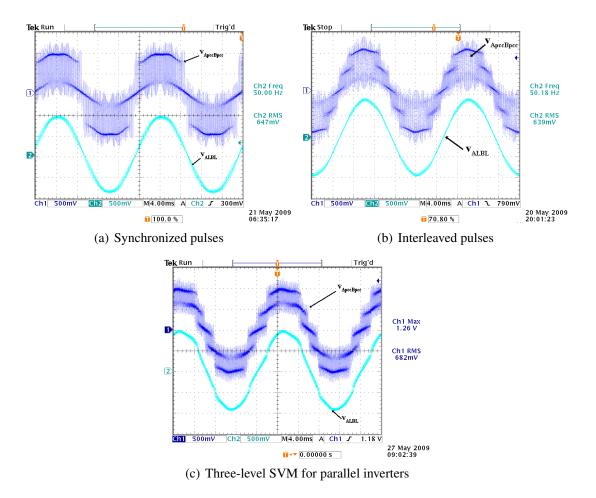

| 4.10 | Comparison of the A-phase voltages on the RL-load                    | 69 |

| 4.11 | Comparison of the line-to-line voltages before and after load filter | 70 |

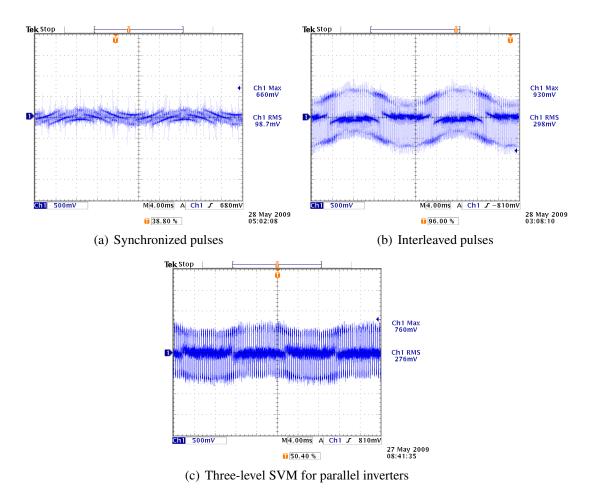

| 4.12 | Comparison of stress on inverter one A-phase inductor                | 71 |

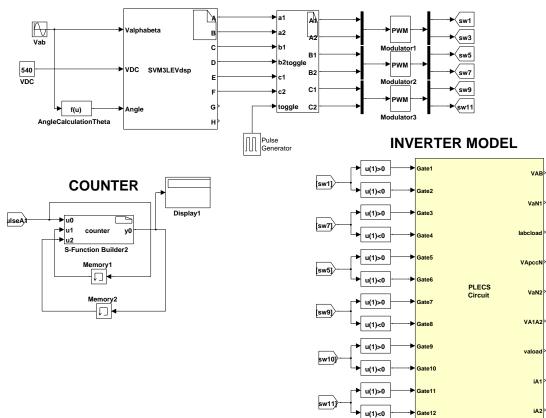

| E.1  | Simulink model of the system.                                        | 85 |

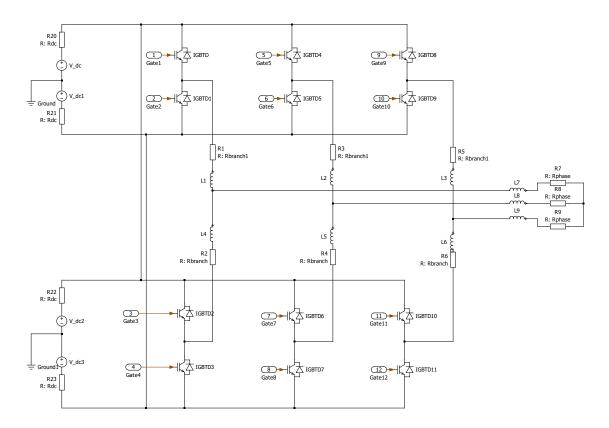

| E.2  | PLECS model of two parallel connected inverters                      | 86 |

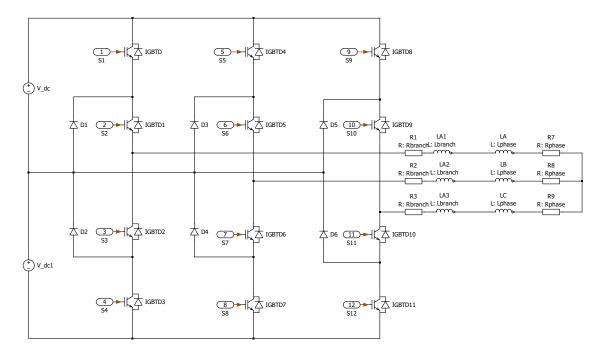

| E.3  | PLECS model of NPC inverter.                                         | 87 |

| E.4  | Region determination in Sector I                                     | 92 |

| F.1  | Coordinate system transformations.                                   | 93 |

This chapter serves as an introduction to the report. The background for the project is explained along with the motivation and constraints for the report. The overall system is presented and the different chapters of the report are described.

## 1.1 Background

The last decades growth in the production of electric energy from renewable energy sources has led to an increased focus on power electronics. Renewable energy sources like photovoltaic, wind and wave energy are relying on power converters in order to exchange power with the grid. Anyone who wants to produce power for the grid has to make sure that their facilities are complying with national grid codes. The grid codes has strict regulations when it comes to the voltage quality, including limits for rapid voltage variations, flicker and harmonic distortion[1]. Rapid voltage variations and flicker are matters of control of the inverter system, but harmonic distortion is created by the pulse width modulated switching of the converter. Different filters topologies can be used in order to reduce the harmonics generated by the switching action in the converter. However, filters for high power converters can be of substantial size and weight and therefore also of great cost since they are made of several expensive metals. Therefore, a lot of effort is made in order to improve the converter system so that the filter can be reduced while the crid codes and system specifications are still met. There are mainly two ways of reducing the harmonic distortion. One way is to optimize the switching sequence, with harmonics as the most important constraint. Another way is to use several levels to build the fundamental voltage i.e. converters with three levels or more. An example of a multilevel inverter is the Neutral Point Clamped (NPC) inverter. Some of the most favorable benefits from using more levels to build the voltage is: lower du/dt and harmonic distortion, lower common mode voltage and lower switching frequency [2]. Some of the drawbacks of adding more levels to the inverter are increased complexity and the need to balance the voltage in the neutral point of the inverter (NPC). It is important to remember that optimizing for harmonics might very well influence other parameters for the converter, such as switching losses and switching frequency in a negative way. It is always a drawback/benefit issue when optimization is performed on a system.

The current limit for high power IGBT switches is today around 2400A. Demands for inverters with higher current capability and also higher reliability has given interest in parallel converters[3]. The benefit of paralleling inverters are not only increased current and reliability, it also gives the designer the possibility to use interaction between the parallel inverters for reducing the Total Harmonic Distortion (THD). An example of this is interleaving as mentioned in [4][5]. A drawback of having converters connected in

parallel is that the interactions between the converters creates circulating currents[6][7][8] if the dc-link is shared between the inverters. Other drawbacks are: the need for a more advanced control system with additional drive circuits, paralleled converters will have a larger volume than one single converter with the same power rating and must have sharing reactors between the inverters. However, in [4] it is reported that the total inductor volume can be decreased when interleaving is used. Unlike for the NPC inverter there is no need to balance the voltage in the neutral point in the parallel inverters, since this point is not used for two-level inverters. However, there is the need to balance the current in each inverter.

## **1.2 Project motivation**

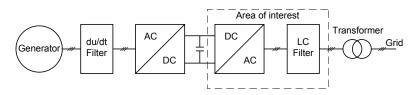

Fig. 1.1 shows the electrical scheme for a wind turbine power plant, which is the system considered in this project. The power level of the system is 1 to 6 MW. KK-electronics is a company manufacturing power electronics and filters needed for wind power plants. As one of few manufacturers, they are using parallel inverters in the AC-AC converter. Four to six inverters are used in parallel operation. The inverters are mounted next to each other, in contrast to other systems where the distance between the inverters can be several hundred meters, e.g. PV power plants. Usually, all wind turbines over 500 KW have their own transformer, and are connected together by a cable grid. This provides an effective filter against common mode voltages, so only switching frequencies have to be delt with in the LC filter. On the generator side, a du/dt filter is applied. At startup for the generator, the windings have to be magnetized. This is done by supplying the generator from the grid via the inverter. The du/dt filter protects the windings against the PWM voltages from the inverter.

Figure 1.1: A Wind Power system with area of interest marked.

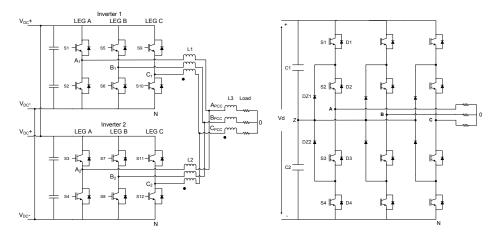

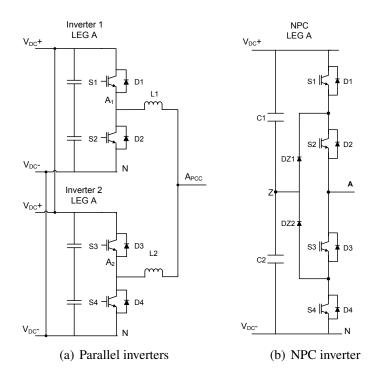

Two inverter topologies will be studied in this report, namely parallel connected twolevel inverters with shared dc-link and the Neutral Point Clamped inverter (NPC). The first topology will be the main focus, and the NPC will serve as comparison for some simulations and measurements.

The two inverter topologies can be seen in Fig.1.2(a) and Fig.1.2(b).

(a) Two parallel connected two-level inverters (b) Neutral Point Clamped inverter. with shared dc-link.

Figure 1.2: The two different topologies

The NPC depicted is a three-level inverter. This report will investegate the possibility to treat the parallel connected two-level inverters as one three-level inverter.

## **1.3 Project limitation**

In Fig.1.1 the area of interest is marked. Only the inverter (DC-AC) and part of the filter will be dealt with, and the grid will be simplified by a load. The project will not deal with the problems of grid connection. The aim of the project is on the comparison of the produced harmonics from the different inverter topologies. The same filter will be used for all experiments, in order to make a valid comparison. Therefore the filter will not be optimal for some of the inverter topologies, but this will help in distiguishing the different performance of the modulation strategies.

It was not possible to work at the mega watt power level for this project, therefore the project has been downscaled to two 2.2 KW inverters with all the simplifications that this implies. The inverters used in the project have a full bridge diode rectifier to create the DC voltage and a three leg two level IGBT inverter for generating the AC voltage. This means that the power flow can only go in one direction, in contrast to back-to-back inverters which are used in a real size system.

The current in the dc-link between the parallel connected inverters will be measured, but not the current in the capacitors for each inverter or the current in the dc supply for each inverter. This is because the inverters from Danfoss gives no possibility to measure the two latter, since the connections for the capacitors and the dc supply are enclosed in the casing and cannot be accessed without dissasembling the inverter. This report will only deal with Space Vector Pulse Width Modulation (SVPWM) as modulation strategy. There will be no comparison between sine-triangle based modulation strategy or sine-triangle modulation with third harmonic injection strategy. If the reader is interested in the mentioned comparison, an article written by Mr. Fei Wang is recommended [9]. The SVPWM is chosen because of its benefits regarding control, graphical representation of voltage vectors, and the authors previous experience in digital implementation of this strategy.

All models presented and used in this report are discretised. This is done either with setting the sample time for source blocks equal to the period time for the carrier wave or by using the zero-order-hold block. Using discrete models gives a better simulation of the real system which is implemented on a DSP based setup.

## **1.4 Problem formulation**

The problem definition for this master thesis is to study the parallel two-level inverter system and to realize a three level modulation strategy for this system. The realized modulation strategy will be compared to two-level SVM with synchronized pulses, with two-level interleaved SVM and to a three level Neutral Point Clamped (NPC) inverter.

To achieve this, the following goals are stated:

- Study the parallel two level system.

- Modify the three-level Space Vector Modulation strategy so it fits to the parallel two level system.

- Implement the strategy on a DSP in a laboratory setup.

- Compare the proposed system with a three-level NPC inverter in simulation.

- Compare the proposed system with synchronized pulses modulation strategy and interleaved modulation strategy in experiments in the laboratory.

## 1.5 Overview

The report contains 5 main chapters. It begins with an introduction chapter which describes the background for the project as well as the motivation, formulation and limitations. Chapter 2 presents a review of the two-level inverter and then proceeds with a study of the parallel inverter topology. Two-level and three-level space vector modulation will be derived. The NPC inverter will also be briefly explained together with the drawbacks and benefits of this inverter. In chapter 3 the simulation for the different modulation strategies will be explained and the results from the different strategies will be

compared to each other. Chapter 4 contains a description of the setup in the laboratory and the comparison for the measurements taken in the laboratory for the different strategies. The conclusion for the report can be found in chapter 5 together with the suggestions for future work. The report ends with Appendix, A to H.

This chapter begins with a quick review of the three phase two-level inverter, before explaining a system of two parallel two-level inverters. Interleaving of the two inverters and a three-level modulation strategy is explained. The two-level and three-level Space Vector Modulation (SVM) is derived together with the switching sequences and the calculation of the dwell times. The Neutral Point Clamped (NPC) inverter is presented with its benefits and drawbacks for comparison with the proposed parallel system. The chapter is ended with a conclusion.

## 2.1 Two-level inverter

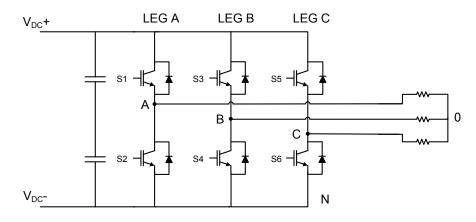

The diagram of a three-phase two-level voltage source inverter is depicted in Fig.2.1.

Figure 2.1: Two-level inverter

The switches in each inverter leg can have two different states P and O, where P is the upper switch turned on and O is the lower switch turned on. The same state syntax is also used in [10]. The different states for each leg can be seen in table 2.1, and in table 2.2 a more graphical representation of the states is shown.

|       | Leg A      |    | Leg B      |    | Leg C |            |

|-------|------------|----|------------|----|-------|------------|

| State | <b>S</b> 1 | S2 | <b>S</b> 3 | S4 | S5    | <b>S</b> 6 |

| Р     | 1          | 0  | 1          | 0  | 1     | 0          |

| 0     | 0          | 1  | 0          | 1  | 0     | 1          |

Table 2.1: Switching states for a three-phase two-level inverter

The output of each leg,  $v_{AN}$   $v_{BN}$   $v_{CN}$ , depends only on  $V_{DC}$  and the switch status. The switches are assumed ideal, meaning that blanking time (also called dead-time) which

| States       | Р     |       | 0     |       |       |       |

|--------------|-------|-------|-------|-------|-------|-------|

|              | Leg A | Leg B | Leg C | Leg A | Leg B | Leg C |

| Upper Switch | 1     | 1     | 1     | 0     | 0     | 0     |

| Lower Switch | 0     | 0     | 0     | 1     | 1     | 1     |

Table 2.2: State P and O representation

is implemented in practical circuits is neglected. This leads to the conclusion that the output voltage is independent of the load current since one of the switches in one leg is always on. [11] Assuming balanced operation, the instantaneous line-to-line voltages can be expressed as in equation 2.1.

$$v_{AB} = v_{AN} - v_{BN}$$

$$v_{BC} = v_{BN} - v_{CN}$$

$$v_{CA} = v_{CN} - v_{AN}$$

(2.1)

where N is the negative dc bus.

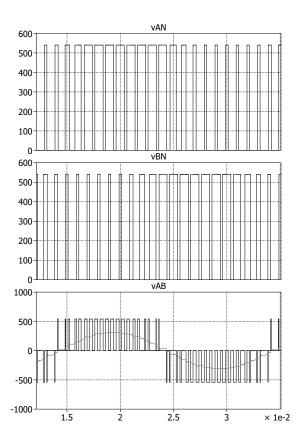

Fig.2.2 shows a graphical view of equation 2.1. It can be observed that  $v_{AN}$  and  $v_{AB}$  will only have two levels,  $V_{DC}$  or 0, but the line-to-line voltage,  $v_{AB}$  will have three levels,  $+V_{DC}$ ,  $-V_{DC}$  and 0.

**Figure 2.2:** Waveforms from two-level inverter.  $f_{SW}=1000Hz V_{DC}=540V V_{ref}=180V$

In Fig.2.2 the average value is plotted together with the voltage  $v_{AB}$ .

Still assuming balanced operation, the inverter phase output voltages can be expressed as in equation 2.2.

$$v_{A0} = v_{AN} - v_{0N}$$

$$v_{B0} = v_{BN} - v_{0N}$$

$$v_{C0} = v_{CN} - v_{0N}$$

(2.2)

Where 0 is the star point of the load.

In Fig.2.3 the relationship between  $v_{AN}$ ,  $v_{0N}$  and  $v_{A0}$  in Eq.2.2 is presented. It can be observed that the phase voltage  $v_{A0}$  will have a maximum amplitude of 2/3  $V_{DC}$ . Looking at  $v_{A0}$  it can be seen that there will be 5 different levels present on the phase voltage, namely  $\pm 2/3V_{DC}$ ,  $\pm 1/3V_{DC}$  and zero.

In a three phase, three wire system

$$i_A + i_B + i_C = 0 (2.3)$$

Figure 2.3: Waveforms from two-level inverter.  $f_{SW}$  = 1000Hz  $V_{DC}$  = 540V  $V_{ref}$  = 180V

and

$$v_{A0} + v_{B0} + v_{C0} = 0 \tag{2.4}$$

Eq.2.4 is presented in Fig.2.4.

**Figure 2.4:** Waveforms from two-level inverter.  $f_{SW}=1000Hz V_{DC}=540V V_{ref}=180V$

Using Eq.2.2 in Eq.2.4 gives

$$(v_{AN} - v_{0N}) + (v_{BN} - v_{0N}) + (v_{CN} - v_{0N}) = 0$$

(2.5)

This can be simplified to

$$v_{0N} = \frac{v_{AN} + v_{BN} + v_{CN}}{3} \tag{2.6}$$

$v_{0N}$  is generally refered to as the common-mode voltage, and is the voltage that is "common" in all three phases at the specific time.

If Eq.2.6 is used in Eq.2.2 it will give Eq.2.7, an expression of the phase voltage for phase A. Similar equations can be found for phase B and C.

$$v_{A0} = \frac{2}{3}v_{AN} - \frac{1}{3}(v_{BN} + v_{CN})$$

(2.7)

Two-level three-phase inverters are commonly used in applications such as ac motor drives and uninterruptible ac power supplies [11]. However, at high power levels (MW) power quality is an important factor, because the ac filter needed to reduce harmonics will

be of substantial size and therefore a big part of the cost for the whole inverter system. If the harmonics can be reduced by using a different inverter topology, then the filter can also be reduced. Therefore a lot of effort is being made on multilevel inverters that has three or more levels such as the three level Neutral Point Clamped (NPC) inverter. The level count refers to the levels present on  $v_{xN}$  where x = A,B and C. By increasing the levels on  $v_{xN}$  it is possible to build a fundamental voltage that contains less harmonics.

#### 2.1.1 Space Vector Modulation for two-level Inverter

The parallel converter system contains two two-levels inverters. This allows the use of two-level Space Vector Modulation strategy to each of them. Taking into consideration one of the inverters, the voltage between phase to neutral can have two levels:  $P = V_{DC}$ , and O = 0.

A property of the Space Vector Modulation (SVM) is the fact that it makes sure that the pulses for all three phases are always centered. In other words, the middle point of the pulses for all three phases are the same for one switching period.

#### **Stationary Space Vectors**

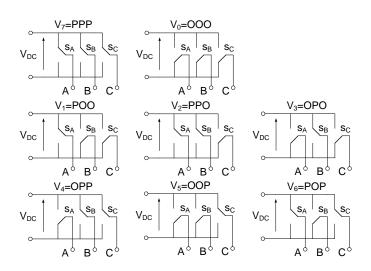

There are eight different possibilities for switching states, because of the three phase system, Fig. 2.5. The vector representation of the voltages created by switching states is depicted on the Fig. 2.6

Figure 2.5: Different switching states of two level inverter.

Figure 2.6: Space vector diagram of two level SVM.

As it can be observed on the Fig. 2.5 and 2.6 there are six active vectors  $\vec{V_1} - \vec{V_6}$  and two zero vectors  $\vec{V_0}$  and  $\vec{V_7}$  (phase voltage and line-to-line will be zero during their activity[12]).

| Space Vector | Switching State | Vector Classification | Vector Magnitude    |  |

|--------------|-----------------|-----------------------|---------------------|--|

| $\vec{V_0}$  | [000]           | Zero Vector           | 0                   |  |

| $\vec{V_1}$  | [POO]           |                       |                     |  |

| $\vec{V_2}$  | [PPO]           |                       |                     |  |

| $\vec{V_3}$  | [OPO]           | Active Vectors        | $\frac{2}{3}V_{DC}$ |  |

| $\vec{V_4}$  | [OPP]           |                       |                     |  |

| $\vec{V_5}$  | [OOP]           |                       |                     |  |

| $\vec{V_6}$  | [POP]           |                       |                     |  |

| $\vec{V_7}$  | [PPP]           | Zero Vector           | 0                   |  |

Table 2.3: Voltage vectors created from different combination of the switches

The active vectors divides the plane into six sectors. The combination of vectors which should be used to synthetize  $V_{ref}$  is based on position of  $V_{ref}$ .

#### **Dwell Times**

The dwell times are the times for which each of the state space vectors is utilized.

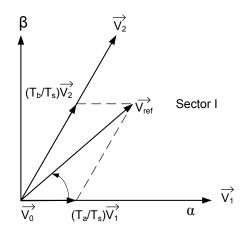

Figure 2.7:  $\vec{V_{ref}}$  representation in sector I.

The dwell times calculation is based on 'the volt-second balancing' principle[10][12], which says that the product of the reference vector and sampling period is equal to the sum of the three nearest space vectors, each multiplied by the period of their extend. E.g:  $\vec{V_1}$ ,  $\vec{V_2}$  and  $\vec{V_0}$  are used when  $\vec{V_{ref}}$  is in sector I:

$$\vec{V_1}T_a + \vec{V_2}T_b + \vec{V_0}T_0 = \vec{V_{ref}}T_s$$

(2.8)

where:

$$\vec{V}_1 = \frac{2}{3} V_{DC};$$

$\vec{V}_2 = \frac{2}{3} V_{DC} e^{j\frac{\pi}{3}};$   $\vec{V}_0 = 0$  (2.9)

Using 2.9 in 2.8 and splitting into real and imaginary parts:

• Real

$$\frac{2}{3}T_a + \frac{1}{3}T_b = \frac{V_{ref}}{V_{DC}}\cos(\theta)T_s$$

(2.10)

• Imaginary

$$\frac{1}{\sqrt{3}}T_b = \frac{V_{ref}}{V_{DC}}sin(\theta)T_s \tag{2.11}$$

Together with:

$$T_a + T_b + T_0 = T_s (2.12)$$

set of equations (2.10, 2.11 and 2.12) can be created to calculate dwell times:  $T_a$ ,  $T_b$ ,  $T_0$ :

$$T_a = \frac{\sqrt{3}T_s V_{ref}}{V_{DC}} \sin(\frac{\pi}{3} - \theta)$$

(2.13)

$$T_b = \frac{\sqrt{3}T_s V_{ref}}{V_{DC}} sin(\theta) \tag{2.14}$$

$$T_0 = T_s - T_a - T_b (2.15)$$

#### **Switching Sequence**

By choosing the three nearest vectors to create  $V_{ref}^{\vec{}}$  it is possible to minimize the harmonic content of the switched waveforms. The main problem is how to put them in collation during switching period to minimize switching transitions and optimize the harmonic profile of the output voltage[13][14]. For two and three level inverters, Space Vector Modulation with seven-segment switching sequence is widely used. There are two main requirements when designing switching sequence according to [15][10][12]:

- Zero or minimum changes in switching are desirable when the reference vector  $\vec{V_{ref}}$  is passing from one sector to another.

- Only two switches in the same leg are involved when passing from one switching state to another in order to reduce device switching frequency.

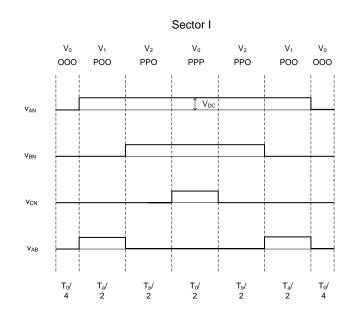

**Figure 2.8:** Switching pattern when  $V_{ref}$  is placed in sector I.

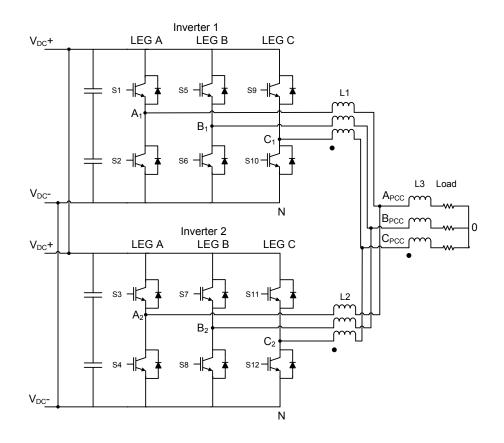

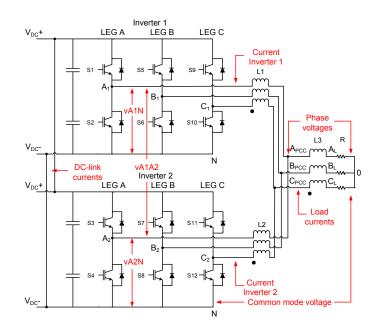

### 2.2 **Two-level inverters in parallel**

The demand for inverters with high current capability and also high reliability has given interest in parallel inverters[3]. Two two-level inverters connected in parallel can be represented as in Fig.2.9. If the two inverters together with L1 and L2 are concidered ideal and are recieving identical PWM signals containing only O and P state then

$$v_{A1N} = v_{A2N}, v_{B1N} = v_{B2N}, v_{C1N} = v_{C2N}$$

(2.16)

Thus

$$v_{A10} = v_{A20}, v_{B10} = v_{B20}, v_{C10} = v_{C20}$$

(2.17)

Eq.2.1 and Eq.2.2 are still valid since they will be the same as if only one inverter were used, and can be represented as in Eq.2.18 and Eq.2.19. With the introduction of an inverter in parallel, there are now three reference points: 1, 2 and *pcc*. The topology for parallel inverters with reference points used in Eq.2.18 and Eq.2.19 is shown in Fig.2.9.

Figure 2.9: Two-level inverters in parallel operation

$$v_{AkB} = v_{AkN} - v_{BkN}$$

$$v_{BkC} = v_{BkN} - v_{CkN}$$

$$v_{CkA} = v_{CkN} - v_{AkN}$$

$$v_{Ak0} = v_{AkN} - v_{0N}$$

$$v_{Bk0} = v_{BkN} - v_{0N}$$

$$v_{Ck0} = v_{CkN} - v_{0N}$$

$$(k = 1, 2, pcc)$$

(2.19)

If the two inverters are recieving synchronized (identical) PWM signals, the current capability for the system is increased compared to one inverter. However, the harmonics and current ripple are the same as having one inverter with the same current capability as the parallel system.

A drawback of paralleling inverters is the interaction that will occur between the inverters and create a current that will circulate from one inverter to the other through the dc-link [4]. The circulating current is also called zero-sequence current [7] since it occurs because of the opposite zero vectors used ( $V_0$  and  $V_7$ ) in the switching sequence. In theory one can say that if the impedance for both inverter branches are equal and the duty cycles for both inverters were identical, there would be no interactions between the inverters and thus no circulating currents. However, there will always be a slight difference in the impedance, and if the inverters have separate current controllers the duty cycles can have a small difference. This will allow a current to circulate in the circuit. For high power applications the impedance in the circuit is very low, since the current can reach several thousand amps and any impedance will result in losses in the circuit as a function of the current. Thus a difference in impedance or in pulse width for a high power system will give a bigger circulating current than a system for low power applications.

The low frequency component of the circulating current can be eliminated by a controller located on the zero-axis, as proposed by several articles [6][7][8]. However, it is not possible to reduce the high frequency component of the circulating current with a current controller since the frequency is given by the switching frequency[4]. Since the high frequency component will increase the peak value of the current in each inverter, it will reduce the maximum output current for the parallel inverter system and therefore it will reduce the systems total efficiency. In order to reduce the high frequency component, the impedance between the two inverters is increased by inserting inductors before the inverter's output are connected together. The inductors can be seen in Fig.2.9 as L1 and L2.

The case with circulating currents is only true if the dc-link is shared between the inverters. If the dc-link is not shared, no circulating currents will flow in the system. Having the dc supply separate for each inverter module will eliminate the circulating currents, but then a reduction of ripple in the dc current and in the capacitor will not be possible. So by having the dc-link shared, one must accept a high frequency cirulating current in the system, but the dc capacitor can be reduced and will experience lower stresses[4].

The parasitic resistance of an inductor will be constant for all frequencies, but the reactance will increase with increasing frequency. This means that the impedance of the inductor will be higher for higher frequencies. The equation for reactance in an inductor is shown in equation 2.20.

$$X_L = \omega \cdot L = 2 \cdot \pi \cdot f \cdot L \tag{2.20}$$

It can be observed in Eq.2.20 that the reactance  $X_L$  changes according to the change of f. This makes an inductor suited for reducing the high frequency components in the current but allow low frequency components to pass.

The parallel inverter system inherits the possibility for achieving better performance for the system trough different modulation strategies. This is done solely in the software for the controller and no hardware changes are required from the initial parallel setup shown in Fig.2.9. An interleaved modulation strategy is described in subsection 2.2.1, and a three-level strategy is explained in subsection 2.2.2

#### 2.2.1 Two interleaved two-level inverters

Interleaving inverters has shown that line inductors can be reduced with up to 60% compared to a single two-level inverter, and if the topology is used for reactive power compensation the dc-capacitor can be reduced by 25% [4]. It should be noted that the interleaved inverters will have one three-phase inductor each, while the single two-level inverter circuit will use only one three-phase inductor. Therefore it should be calculated for each case if it is economically viable to use interleaved inverters with respect to cost for the inductors. In [4] it is reported that the total weight and size for two inductors of 3% rated 300 Amps is less than the weight and size for one inductor of 5% rated 600 Amps. In the same article it is also reported that the use of common-mode coils shows promising results with respect to reducing the common-mode signals. Interleaving of inverters is also refered to as pulse shifting or phase shifted gate signals.

When the term of percentage value is used for a inductor, it refers to the percent of voltage drop the inductor will experience compared to the rated voltage when the rated current is passed through the component. For an inverter rated 10 Amps and 230 phase voltage, an inductor of 10mH will give:

$$X_L = \omega \cdot L = 2\pi f \cdot L = 2\pi \cdot 50Hz \cdot 10mH = 3.14\Omega \tag{2.21}$$

The voltage drop

$$V_{DROP} = X_L \cdot I_{RATED} \cdot 100 = 3.14\Omega \cdot 10A \cdot 100 = 31.4V$$

(2.22)

This means that the inductor will have a percentage value of:

$$\frac{V_{DROP}}{V_{RATED}} = \frac{31.4V}{230V} = 13.7\%$$

(2.23)

By using the percentage value it is easier to relate the size of the inductor to different power levels.

As mentioned in subsection 2.2 the main drawback of paralleling inverters, and especially if they are interleaved, is the problem with circulating currents. When the inverters are interleaved, a conduction path is purposely formed from the output of both inverters through the dc-link.

The general idea of interleaved inverters, is to have the ripple in the current from inverter 2 shifted 180 degrees from the ripple in the current from inverter 1. Since the current on the output is formed by the current from both inverters, the two ripple currents will cancel each other out to a certain amount giving a reduction in the output current ripple. This is shown in Fig.2.10. In [5] it is reported that the cancellation will only be total when the duty cycle is 50%. If the duty cycle has a different value, the ripple will remain in the output current but with a reduced amplitude. Another benefit from interleaving is that the switching frequency seen from the output of the parallel system appears as twice the switching frequency of each inverter. This gives a reduction in the harmonics. On the other side, interleaving will give an increase in the peak current for each inverter and thus lower the total output current. It is therefore a desicion to make between system efficiency and harmonics.

Figure 2.10: Pulses shifted 180° by shifting carrier waves (Discretised model).

The inverters can be interleaved by simply shifting the carrier waves for the PWM for each inverter, so that inverter 2 has carrier waves that are 180° shifted compared to the carrier waves for inverter 1. The source signal for both PWM can be the same or it can come from seperate controllers giving an almost identical source signal. As seen in Fig.2.10, the source signal is sampled during the on time for the gate signal for inverter 1. This will lead to a smaller pulse width for inverter 1 than for inverter 2 when the source signal is descending, and opposite when the source signal is ascending. The sampling can be done in a different time or with a different frequency, but there will always be a difference in the pulses for inverter 1 compared to inverter 2 during one carrier period if the source signal is varying. For one period of the source signal this pulse difference will be equalized if the source signal is a uniform signal (identical half waves but with different polarity).

When the pulses to inverter 1 and inverter 2 are not identical, the voltages can be expressed as:

$$v_{ApccN} = \frac{v_{A1N} + v_{A2N}}{2}$$

(2.24)

And

$$v_{ApccBpcc} = v_{ApccN} - v_{BpccN} \tag{2.25}$$

Combining Eq.2.24 with Eq.2.25 gives Eq.2.26, which is an expression for  $v_{ApccBpcc}$  by the use of vA1N, vA2N, vB1N and vB2N.

$$v_{ApccBpcc} = \left(\frac{v_{A1N} + v_{A2N}}{2}\right) - \left(\frac{v_{B1N} + v_{B2N}}{2}\right)$$

(2.26)

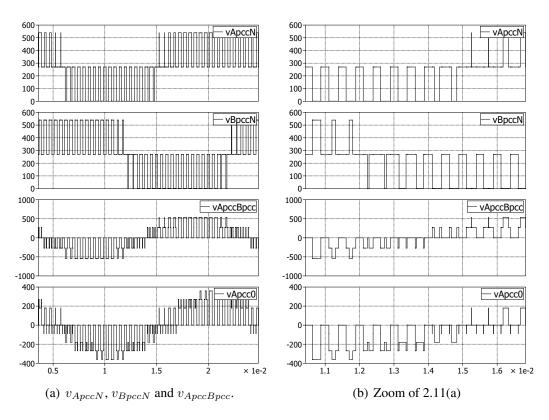

Since  $v_{A1N}$  and  $v_{A2N}$  can only have the value  $V_{DC}$  or 0, there are three possible results from Eq.2.24:  $V_{DC}$ ,  $1/2V_{DC}$  and 0. This proves that there will be three levels on the phase voltages  $v_{ApccN} v_{BpccN} v_{CpccN}$ , which is also confirmed in Fig.2.11

The interleaved modulation strategy gives 5 levels on the line-to-line voltage  $v_{ApccBpcc}$  and 8 levels on the phase voltage  $v_{Apcc0}$ . This gives a better representation of the fundamental voltage, but as it can be seen in Fig.2.11 all levels reach zero at half the switching frequency and can therefore not be seen as "real"levels. Since the inverters are interleaved, the frequency of the pulses in the voltages after *pcc* is twice of the individual invertes switching frequency. The "real"levels generated from the three-level modulation strategy used in the proposed three-level strategy for parallel inverters and in the NPC inverter are presented in the next sections in this chapter.

For it to be easy to distinguish the different levels all inductance in the circuit in Fig.2.9 have been removed and replaced with only resistors. This is solely done for explanation purposes for the different voltage levels, and will not represent the system later in the report or in the laboratory.

The reason for the levels in the line-to-line or phase voltage reaching zero is because of the nature of the interleaved strategy. Having Eq.2.25 in mind, it can be seen in Fig.2.11 that the voltages  $v_{ApccN}$  and  $v_{BpccN}$  will have the same value two times every switching period. This will lead to  $v_{ApccBpcc}$  beeing zero. This means that the load will experience the highest du/dt stresses when the voltage is at its peak value. Using the interleaved strategy it is not possible to raise or lower the middle value of the voltage, like it is in a three-level inverter.

**Figure 2.11:**  $f_{SW}$ =1000Hz  $V_{DC}$ =540V  $V_{ref}$ =180V

The effect interleaving has on the circulating current and on the THD will be investigated in simulations and in experiments in the laboratory.

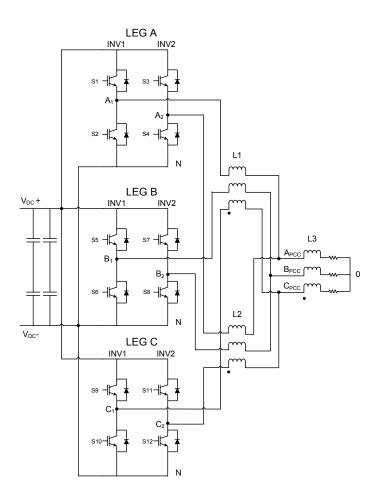

#### 2.2.2 Two parallel two-level inverters used as one three-level inverter

When two inverters are paralleled, it is possible to increase the number of states for each phase leg. A phase leg consists of all the paralleled legs for one phase. In fact, it is possible to represent the paralleled two level inverters as one three-level inverter if *pcc* is used as reference point. A three-level representation of Fig.2.9 is depicted in Fig.2.12. Notice that no connections has been changed, only the way the circuit is drawn. Taking the phase leg A as an example, one can observe that the legs individually can only have two states, O and P. By combining these two states it is possible to get a third state H. However, the third state H will only appear at *pcc* and not on the individual legs of the inverter. This phenomenon is also observable for the interleaved modulation strategy in section 2.2.1, but not actively utilized. Tab.2.4 presents the different states and how they are created for phase leg A. The procedure is the same for phase leg B and C. H is created by using different states on inverter 1 and 2, therefore there will be two ways of creating H. The deciding factors when chosing which one of H1 or H2 to use to represent H, are switching loss reduction and equal load sharing of the switches.

Figure 2.12: Three-level representation of two parallel two-level inverters

|            | Switching States |    |    |   |  |  |  |

|------------|------------------|----|----|---|--|--|--|

| Leg A      | 0                | H1 | H2 | P |  |  |  |

| <b>S</b> 1 | 0                | 1  | 0  | 1 |  |  |  |

| S2         | 1                | 0  | 1  | 0 |  |  |  |

| <b>S</b> 3 | 0                | 0  | 1  | 1 |  |  |  |

| S4         | 1                | 1  | 0  | 0 |  |  |  |

Table 2.4: Switchingstates for Leg A

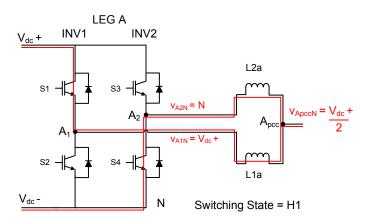

When the state H is used, a current path from one phase of  $V_{DC}$ , through leg A on both inverters and back to the opposite phase of  $V_{DC}$  is created. This is also the case for leg B and leg C. The current path for H1 is drawn in Fig.2.13. It can be seen in Fig.2.13 that the inductors will act as a voltage dividers in the H state. This explains why there will be three levels when looking at  $v_{ApccN}$ , and only two levels when looking at  $v_{A1N}$  or  $v_{A2N}$ . It should be noted that the inductors in Fig.2.12 and in Fig.2.13 are the same, three-phase inductors with common core, but for explanation purposes the drawing is simplified in Fig.2.13.

| States       | (      | )      | H1     |        | H2     |        | Р      |        |

|--------------|--------|--------|--------|--------|--------|--------|--------|--------|

|              | Leg A1 | Leg A2 |

| Upper switch | 0      | 0      | 1      | 0      | 0      | 1      | 1      | 1      |

| Lower switch | 1      | 1      | 0      | 1      | 1      | 0      | 0      | 0      |

Table 2.5: Representation of the different states for phase leg A

Figure 2.13: Phase leg A for state H1

Looking at the line-to-line voltage  $v_{ApccBpcc}$ , it can be observed that there will be three levels on  $v_{ApccN}$  and three levels on  $v_{BpccN}$ . Combining 3 by 3 levels gives a total of nine possible combinations. This is shown in Tab.2.6.

| Levels for $v_{ApccBpcc}$ |             |             |                |  |  |  |  |

|---------------------------|-------------|-------------|----------------|--|--|--|--|

| State                     | $v_{ApccN}$ | $v_{BpccN}$ | $v_{ApccBpcc}$ |  |  |  |  |

| 00                        | 0           | 0           | 0              |  |  |  |  |

| OH                        | 0           | 1/2         | -1/2           |  |  |  |  |

| OP                        | 0           | 1           | -1             |  |  |  |  |

| HO                        | 1/2         | 0           | 1/2            |  |  |  |  |

| HH                        | 1           | 1           | 0              |  |  |  |  |

| HP                        | 1           | 1/2         | 1/2            |  |  |  |  |

| PO                        | 1           | 0           | 1              |  |  |  |  |

| PH                        | 1           | 1/2         | 1/2            |  |  |  |  |

| PP                        | 1           | 1           | 0              |  |  |  |  |

Table 2.6: Possible levels for two parallel two-level inverters on the line-to-line voltage

Even if there are nine combinations for the states for phase leg A and B, there are only five combinations that will give different levels, thus there will be five levels on the line-to-line voltage. See Eq.2.25 for the calculation of  $v_{ApccBpcc}$ . In comparison, a two-level inverter has two levels on phase voltage and three levels on line-to-line voltage.

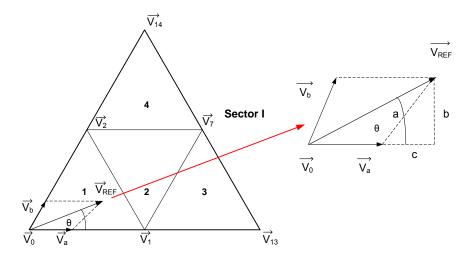

### 2.2.3 Space Vector Modulation for 3 level Inverter

One of the features of two parallel connected inverters is the ability to obtain three levels of voltage (phase to neutral)  $P = V_{DC}$ ,  $H = \frac{1}{2}V_{DC}$  and O = 0. Describing system in the

meaning of three voltage levels provides similarity to Three-Level Neutral Point Clamped Inverter. This similarity allows to approach Space Vector Modulation in the same way like for Neutral Point Clamped Inverter [10].

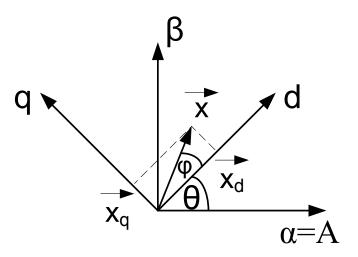

### **Stationary Space Vectors**

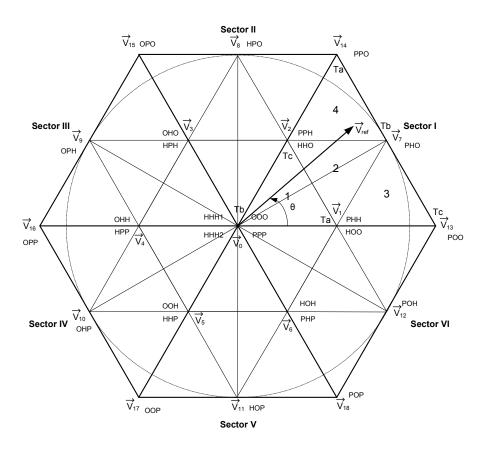

There are twenty seven different possibilities for switching states, because of the three phase system. Additionaly, the H-state can be created in two ways. The nineteen vectors can be obtained from this switching states which are presented in Table 2.7 and depicted in the Fig. [2.17]

| Space Vector                                              | Switching State     | Vector Classification | Vector Magnitude           |

|-----------------------------------------------------------|---------------------|-----------------------|----------------------------|

| $\vec{V_0}$                                               | [OOO], [HHH], [PPP] | Zero Vector           | 0                          |

| $\vec{V_1}$                                               | [HOO] and [PHH]     |                       |                            |

| $ec{V_2}$                                                 | [HHO] and [PPH]     |                       |                            |

| $\vec{V_3}$                                               | [OHO] and [HPH]     | Small Vector          | $\frac{1}{3}V_{DC}$        |

| $\vec{V_4}$                                               | [OHH] and [HPP]     |                       |                            |

| $\vec{V_5}$                                               | [OOH] and [HHP]     |                       |                            |

|                                                           | [HOH] and [PHP]     |                       |                            |

| $\vec{V_7}$                                               | [PHO]               |                       |                            |

| $\vec{V_8}$                                               | [HPO]               |                       |                            |

| $\vec{V_9}$                                               | [OPH]               | Medium Vector         | $\frac{\sqrt{3}}{3}V_{DC}$ |

| $V_{10}$                                                  | [OHP]               |                       | Ŭ                          |

| $V_{11}$                                                  | [HOP]               |                       |                            |

| $V_{12}$                                                  | [POH]               |                       |                            |

| $\begin{array}{c} V_{12} \\ V_{13} \\ V_{14} \end{array}$ | [POO]               |                       |                            |

| $\vec{V_{14}}$                                            | [PPO]               |                       |                            |

| $\overrightarrow{V_{15}}$ $\overrightarrow{V_{16}}$       | [OPO]               | Large Vector          | $\frac{2}{3}V_{DC}$        |

| $V_{16}$                                                  | [OPP]               |                       | Ť                          |

| $V_{17}$                                                  | [OOP]               |                       |                            |

| $\vec{V_{18}}$                                            | [POP]               |                       |                            |

Table 2.7: Voltage vectors created from different combination of the switches

Taking into consideration the length of these vectors four different kinds can be distinguished:

• Zero vector

The zero vector is created by three different switching states [OOO], [HHH] and [PPP]. The amplitude of  $V_0$  is equal to 0.

• Small vectors

Their amplitude is equal to  $\frac{1}{3}V_{DC}$ . Each of them can be created in two ways, f.e.  $\vec{V_1}$  is made by [HOO] and [PHH] switching states.

$$\vec{V}_{1}(HOO) = \frac{2}{3}(V_{AN}e^{j0} + V_{BN}e^{j\frac{2\pi}{3}} + V_{CN}e^{j\frac{4\pi}{3}})$$

$$= \frac{2}{3}(\frac{V_{DC}}{2}e^{j0}) = \frac{V_{DC}}{3}$$

(2.27)

**Figure 2.14:** Small vector  $\vec{V_1}(HOO)$  representation in  $\alpha\beta$  plane.

• Medium vectors

Their amplitude is equal to  $\frac{\sqrt{3}}{3}V_{DC}$ .

$$\vec{V}_{8}(HPO) = \frac{2}{3} (V_{AN}e^{j0} + V_{BN}e^{j\frac{2\pi}{3}} + V_{CN}e^{j\frac{4\pi}{3}})$$

$$= \frac{2}{3} (\frac{V_{DC}}{2}e^{j0} + V_{DC}e^{j\frac{2\pi}{3}}) = j\frac{\sqrt{3}}{3}V_{DC}$$

(2.28)

**Figure 2.15:** Medium vector  $\vec{V_8}(HPO)$  representation in  $\alpha\beta$  plane.

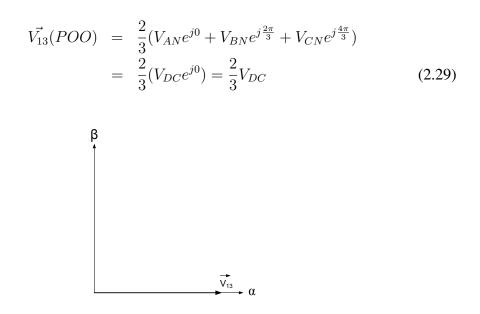

• Large vectors

Their amplitude is equal to  $\frac{2}{3}V_{DC}$ .

**Figure 2.16:** Large vector  $\vec{V_{13}}(POO)$  representation in  $\alpha\beta$  plane.

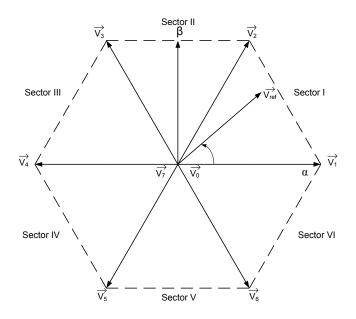

The large vectors divides the plane into six sectors. Each of these sectors can be split into four regions as it is depicted in Fig.2.17. Combination of vectors which should be used to synthetize  $V_{ref}$  is based on its position. For example, when  $V_{ref}$  is in region four of sector I,  $V_2$ ,  $V_7$  and  $V_{14}$  are used.

Figure 2.17: Space Vector Diagram.

### **Dwell Times**

The following Figure presents reference vector transition from sector I to sector II:

**Figure 2.18:**  $\vec{V_{ref}}$  transition between two sectors.

The dwell times calculation for three level SVM is similar to two level SVM. Vectors:  $\vec{V_2}$ ,  $\vec{V_7}$  and  $\vec{V_{14}}$  are used when  $\vec{V_{ref}}$  is in region four of sector I:

$$\vec{V_{14}}T_a + \vec{V_7}T_b + \vec{V_2}T_c = \vec{V_{ref}}T_s$$

(2.30)

where:

$$\vec{V_{14}} = \frac{2}{3} V_{DC} e^{j\frac{\pi}{3}}; \qquad \qquad \vec{V_7} = \frac{\sqrt{3}}{3} V_{DC} e^{j\frac{\pi}{6}}; \qquad \qquad \vec{V_2} = \frac{1}{3} V_{DC} e^{j\frac{\pi}{3}}$$

Solving Eq.2.31:

$$\frac{2}{3}[\cos(\frac{\pi}{3}) + j\sin(\frac{\pi}{3})]T_a + \frac{\sqrt{3}}{3}[\cos(\frac{\pi}{6}) + j\sin(\frac{\pi}{6})]T_b + \frac{1}{3}[\cos(\frac{\pi}{6}) + j\sin(\frac{\pi}{6})]T_c \\ = \frac{V_{ref}}{V_{DC}}[\cos(\theta) + j\sin(\theta)]T_s$$

(2.31)

And splitting into real and imaginary part:

• Real

$$\frac{1}{3}T_a + \frac{1}{2}T_b + \frac{1}{6}T_c = \frac{V_{ref}}{V_{DC}}\cos(\theta)T_s$$

(2.32)

• Imaginary

$$\frac{\sqrt{3}}{3}T_a + \frac{\sqrt{3}}{6}T_b + \frac{\sqrt{3}}{6}T_c = \frac{V_{ref}}{V_{DC}}sin(\theta)T_s$$

(2.33)

Together with:

$$T_a + T_b + T_c = T_s \tag{2.34}$$

a set of equations (2.32, 2.33 and 2.34) can be created to calculate dwell times:  $T_a$ ,  $T_b$ ,  $T_c$ . The dwell times for every region in sector I are presented in Tab.2.8:

| Region | $T_a$          |                                             |             | $T_b$                                       | $T_c$          |                                             |  |

|--------|----------------|---------------------------------------------|-------------|---------------------------------------------|----------------|---------------------------------------------|--|

| 1      | $\vec{V_1}$    | $T_s[2m_a sin(\frac{\Pi}{3}-\theta)]$       | $\vec{V_0}$ | $T_s[1 - 2m_a sin(\frac{\Pi}{3} + \theta)]$ | $\vec{V_2}$    | $T_s[2m_a sin(\theta)]$                     |  |

| 2      | $\vec{V_1}$    | $T_s[1 - 2m_a sin(\theta)]$                 | $\vec{V_7}$ | $T_s[2m_a sin(\frac{\Pi}{3} + \theta) - 1]$ | $\vec{V_2}$    | $T_s[1 - 2m_a sin(\frac{\Pi}{3} - \theta)]$ |  |

| 3      | $\vec{V_1}$    | $T_s[2 - 2m_a sin(\frac{\Pi}{3} + \theta)]$ | $\vec{V_7}$ | $T_s[2m_a sin(\theta)]$                     | $\vec{V_{13}}$ | $T_s[2m_a sin(\frac{\Pi}{3} - \theta) - 1]$ |  |

| 4      | $\vec{V_{14}}$ | $T_s[2m_a sin(\theta) - 1]$                 | $\vec{V_7}$ | $T_s[2m_a sin(\frac{\Pi}{3}-\theta)]$       | $\vec{V_2}$    | $T_s[2 - 2m_a sin(\frac{\Pi}{3} + \theta)]$ |  |

Table 2.8: Dwell times for sector I

, where  $m_a = \frac{\sqrt{3}V_{ref}}{V_{DC}}$  is modulation index.

The dwell times for the other sectors (II to VI) are calculated by subtracting a multiple of  $\frac{\pi}{3}$  from the angular displacement  $\theta$ . By doing this the modified angle falls into sector I and the calculations presented in Tab.2.8 can be used.

### **Switching Pattern**

The requirements for choosing switching pattern are the same like for two-level SVM.

- Zero or minimum changes in switching are desirable when the reference vector  $\vec{V_{ref}}$  is passing from one sector (region) to another.

- Only two switches in the same leg are involved when passing from one switching state to another in order to reduce device switching frequency.

**Figure 2.19:** Switching pattern when  $V_{ref}$  is placed in sector I region three and four.

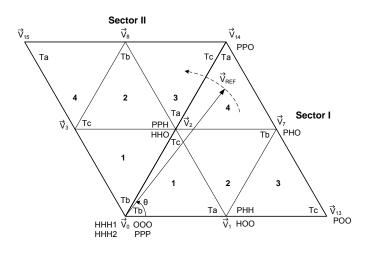

Tab.2.9 and Tab.2.10 presents the switching sequence for  $V_{ref}$  positioned in sector I and II. The transition of  $V_{ref}$  between two successive sectors is done excluding change in switching state. Also transition between two regions is realized with minimum number of switches changes. Reference vector in region three can be synthetized by three nearest stationary vectors:  $V_1$ ,  $V_7$  and  $V_{13}$ . It can be observed at Fig.2.19, that transition between two states includes change only between O and H state, or H and P. The switching patterns for all sectors are presented in Appendix C. The switching sequence presented on the Fig.2.19 has been designed for three level NPC inverter and spread in order to implement

|         | SECTOR I       |       |                |       |                |       |                |       |  |

|---------|----------------|-------|----------------|-------|----------------|-------|----------------|-------|--|

| Segment |                | 1     |                | 2     | 3              |       | 4              |       |  |

| 1st     | $\vec{V}_0$    | [000] | $\vec{V}_{1O}$ | [HOO] | $\vec{V}_{1O}$ | [HOO] | $\vec{V}_{2O}$ | [HHO] |  |

| 2nd     | $\vec{V}_{1O}$ | [HOO] | $\vec{V}_{2O}$ | [HHO] | $\vec{V}_{13}$ | [POO] | $\vec{V}_7$    | [PHO] |  |

| 3rd     | $\vec{V}_{2O}$ | [HHO] | $\vec{V}_7$    | [PHO] | $\vec{V}_7$    | [PHO] | $\vec{V}_{14}$ | [PPO] |  |

| 4th     | $\vec{V}_0$    | [HHH] | $\vec{V}_{1P}$ | [PHH] | $\vec{V}_{1P}$ | [PHH] | $\vec{V}_{2P}$ | [PPH] |  |

| 5th     | $\vec{V}_{2O}$ | [HHO] | $\vec{V}_7$    | [PHO] | $\vec{V}_7$    | [PHO] | $\vec{V}_{14}$ | [PPO] |  |

| 6th     | $\vec{V}_{1O}$ | [HOO] | $\vec{V}_{2O}$ | [HHO] | $\vec{V}_{13}$ | [POO] | $\vec{V}_7$    | [PHO] |  |

| 7th     | $\vec{V}_0$    | [000] | $\vec{V}_{1O}$ | [HOO] | $\vec{V}_{1O}$ | [HOO] | $\vec{V}_{2O}$ | [HHO] |  |

Table 2.9: Switching pattern for sector I

| SECTOR II |                |       |                |       |                |       |                |       |

|-----------|----------------|-------|----------------|-------|----------------|-------|----------------|-------|

| Segment   |                | 1     |                | 2     | 3              |       | 4              |       |

| 1         | $\vec{V_0}$    | [000] | $\vec{V_{2O}}$ | [HHO] | $\vec{V_{2O}}$ | [HHO] | $\vec{V_{3O}}$ | [OHO] |

| 2         | $\vec{V_{3O}}$ | [OHO] | $\vec{V_8}$    | [HPO] | $\vec{V_8}$    | [HPO] | $\vec{V_{15}}$ | [OPO] |

| 3         | $\vec{V_{2O}}$ | [HHO] | $\vec{V_{3P}}$ | [HPH] | $\vec{V_{14}}$ | [PPO] | $\vec{V_8}$    | [HPO] |

| 4         | $\vec{V_0}$    | [HHH] | $\vec{V_{2P}}$ | [PPH] | $\vec{V_{2P}}$ | [PPH] | $\vec{V_{3P}}$ | [HPH] |

| 5         | $\vec{V_{2O}}$ | [HHO] | $\vec{V_{3P}}$ | [HPH] | $\vec{V_{14}}$ | [PPO] | $\vec{V_8}$    | [HPO] |

| 6         | $\vec{V_{3O}}$ | [OHO] | $\vec{V_8}$    | [HPO] | $\vec{V_8}$    | [HPO] | $V_{15}$       | [OPO] |

| 7         | $\vec{V_0}$    | [000] | $\vec{V_{2O}}$ | [HHO] | $\vec{V_{2O}}$ | [HHO] | $\vec{V_{3O}}$ | [OHO] |

Table 2.10: Switching pattern for sector II

in system of parallel connected inverters. As it can be observed on the Fig.2.20 twelve new signals (six for H1 state utilization and six for H2 state utilization) has been created in order to control every leg of the system. The new switching pattern contains continuous states (P or 0) for whole sampling period.

From this pattern it is possible to calculate duty cycles, which will be compared with triangular in order to create switching signals. Following example presents calculation of duty cycle, which has been made for phase B of inverter one when the reference vector is passing through region three of sector one.

$$D_{B1} = \frac{0 \cdot \frac{T_a}{4} + 1 \cdot \frac{T_c}{2} + 1 \cdot \frac{T_b}{2} + 1 \cdot \frac{T_a}{4}}{\frac{T_s}{2}}$$

(2.35)

Following Eq.2.35 the duty cycles of each phase can be calculated likewise for every sector in hexagon depicted on the Fig.2.17.

**Figure 2.20:** Switching pattern separated for implementation in system of parallel connected inverters when  $V_{ref}^{i}$  is placed in sector I region three and four.

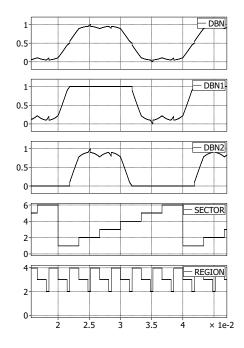

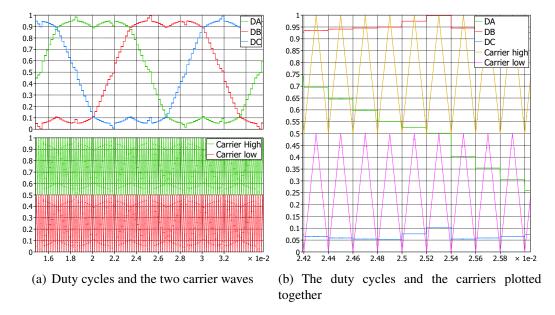

The Fig.2.21 presents the duty cycle  $(D_B)$  of phase B for NPC inverter, which is decomposed for duty cycles  $(D_{B1} \text{ and } D_{B2})$  for parallel connected inverters system.

**Figure 2.21:** Duty cycles  $(D_{B1} \text{ and } D_{B2})$  for system of parallel inverters obtained from duty cycle  $(D_B)$  for NPC inverter.

From Fig.2.21 it can be seen that the waveform of the duty cycles contains small spikes on lower and upper part of the waveform. The spikes occur in region two. The reason for this is the chosen switching sequence. The same three-level switching sequence is used for the proposed three-level SVM for parallel inverters and for the NPC inverter. Therefore the two methods will still be comparable.

As it can be observed the duty cycles  $D_{B1}$  and  $D_{B2}$  contains continuos states, which could be referred to switching pattern depicted on the Fig.2.20. Especially this phenomenon is visible in sector I - region three, where  $D_{B2}$  has value zero, which was shown in the switching pattern.

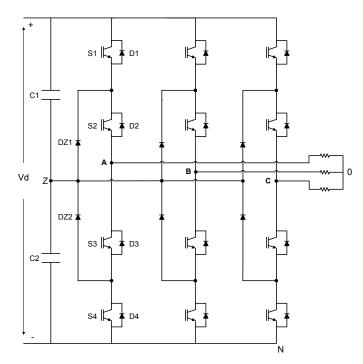

# 2.3 Three-level Neutral Point Clamped inverter

The most commonly used three-level inverter is the NPC inverter depicted in Fig.2.22 [10]. The main application area for the NPC is within MV drives. There are also other types of three-level inverters such as the Cascaded H-Bridge inverter and the capacitor-clamped (flying capacitor) inverter [10][2], but as mentioned before, the NPC is the most commonly used and therefore most suited for comparison with the parallel two-level inverter.

The NPC has three states that creates three levels on  $v_{xN}$ . The states and switch combinations can be seen in Tab.2.11.

Figure 2.22: Three-phase NPC inverter

In the H state, when switches S2 or S3 are on, the neutral point is clamped to the output through DZ1 or DZ2 and  $v_{AN}=1/2 v_{dc}$ . For the other two states, P and 0, the diodes are not conducting giving  $v_{AN}$  equal to  $v_{dc}$  and 0 respectively.

| State |            | VAN |            |    |             |

|-------|------------|-----|------------|----|-------------|

|       | <b>S</b> 1 | S2  | <b>S</b> 3 | S4 |             |

| Р     | 1          | 1   | 0          | 0  | $v_{dc}$    |

| Η     | 0          | 1   | 1          | 0  | $1/2v_{dc}$ |

| 0     | 0          | 0   | 1          | 1  | 0           |

Table 2.11: Switching states for a three-phase three-level NPC inverter

Tab.2.12 presents a different view of how the levels are created in the NPC inverter.

| State               | 0 | Η | P |

|---------------------|---|---|---|

| Top switch          | 0 | 0 | 1 |

| Upper middle switch | 0 | 1 | 1 |

| Lower middle switch | 1 | 1 | 0 |

| Bottom switch       | 1 | 0 | 0 |

Table 2.12: Representation of the different states for leg A

Figure 2.23: Waveforms of the NPC inverter.  $f_{SW}=1000Hz V_{DC}=540V V_{ref}=180V$

Benefits of the NPC:

- Low du/dt and harmonics. The line-to-line voltage will have five levels, which will give lower du/dt and harmonics compared to the two-level inverter which will have three level line-to-line voltage[2][10][13]. This will reduce switching stresses for the windings in a motor or a transformer.

- Because of the topology of the NPC, the switches withstand only half of the dc bus voltage during commutation from P to H, H to 0 and vica versa. Switching between P and 0 is not allowed[10].

- The input current will have very low distortion[2].

Drawbacks of the NPC:

- Increased complexity for control and modulation strategy.[10]

- Unequal load distribution on the switches. S2 is always on in P state and S3 always on in the 0 state. S1 and S4 is not used in the H state so S2 and S3 are used more than S1 and S4. This has been corrected in the Active Neutral Point Clamped (ANPC), where the clamping diodes have been replaced with switches[16].

- Additional clamping diodes (NPC), or additional switches (ANPC) compared to a two-level inverter. This increases the inverter cost and also the losses in the inverter.

- Neutral point balancing problems. The neutral point may deviate during operation because of minor component difference in the capacitors[10].

# 2.4 Conclusion

The relation between two parallel connected two-level inverters and a three-level inverter has been shown. The two-level and the three-level Space Vector Modulation strategy has been derived and will be used in simulations and experiments.

The three-level NPC gives better performance when it comes to harmonics on the ac side and also regarding ripple in the dc current, but the complexity of control together with the increased number of components makes it more expensive compared to the single two level inverter. The proposed system of two parallel connected two-level inverters has the ability to create the voltage levels much like in the NPC inverter. For the parallel inverters, the number of switches are the same as for the NPC, but the NPC will have six extra diodes. On the other hand the parallel inverters need sharing inductors on the output of each inverter and the two inverter currents must be balanced. It must be noted that the sharing inductors will only need to take half of the load current.

The three-level NPC inverter experience unequeal load distribution on the switches and neutral point balancing problems, where in the parallel system the switches can be loaded equally and will not have problems with balancing the neutral voltage since this point is not used at all in the inverter. The unequal loading of the switches in the NPC inverter comes from the fact that the states will only change between P and H and between H and 0. Therefore the state H will be used more than P and 0, leading to more use of the switches representing H. However, in the parallel system of two-level inverters, H can be represented in two ways giving a chance to distribute the load more evenly on the switches.

In theory it is possible to use the same three-level SVM strategy for the NPC and the parallel two-level inverter. The only difference is how the states P, H and 0 are represented by the switches and how the triangle modulation is realized.

The proposed system of two parallel connected two-level inverters will be tested in simulations and experiments and its performance will be compared when using identical two-level SVPWM, pulse shifted two-level SVPWM and three-level SVPWM. The comparison with the three level NPC inverter using three-level SVPWM will be done only in simulation due to laboratory contraints.

This chapter deals with different simulations for the system of two parallel connected two-level inverters. Two-level SVM with synchronized pulses, two-level SVM with pulses shifted and three level SVM are implemented in open loop condition to study behaviour of the system. The simulation of Three-Level NPC Inverter is also presented in this chapter in order to compare with the system of parallel connected inverters. All the simulations have been made in Matlab/Simulink environment with the use of PLECS toolbox. Each modulation strategy will be briefly discussed before the results are compared.

# 3.1 Simulation constraints and parameters

The simulation for the different modulation strategies are carried out in open loop, since the purpose is to make a comparison between the performance of the system with synchronized pulses, shifted pulses and the proposed system using three-level SVM. In addition, simulation results of the NPC inverter will be briefly discussed. By running the system in open loop it can be observed what amount of THD and which harmonics the different strategies will generate. This makes the comparison as fair as possible. A current controller will be able to reduce and possibly eliminate the low order harmonics. Therefore a modulation strategy having mainly low order harmonics can be improved more by a current controller than a modulation strategy with higher order harmonics.

It should also be noted than only an L-L filter is used, so there is no capacitor to short circuit the high frequency components in the voltage. Therefore there will be a high ripple in the current, and there will be a lot of harmonics in the voltage. However, this will make it easier to distinguish any difference in performance between the different systems.

Simulation Parameters:

- Power for each inverter = 2.2kW

- $V_{DC} = 540V$

- Carrier frequency  $f_{carrier} = 5000$ Hz

- Modulation index  $m_a = 0.9$  (Vref = 280V)

- Three-phase inductor L1 and L2 = 8mH  $0.2\Omega$

- Three-phase load inductor = 7.2mH

- Load resistor =  $40\Omega$

The simulation parameters represent the values for the components that is used in the lab. This ensures the best comparison between the simulation results and the laboratory results.

Figure 3.1: Specification of measurements for the parallel inverter system.

Fig.3.1 shows where the different measurements are taken. This is valid for all measurements taken on the parallel inverter system. The measurements taken for the NPC inverter will be specified in the relevant section.

# 3.2 Simulation models

### 3.2.1 Two-level SVM

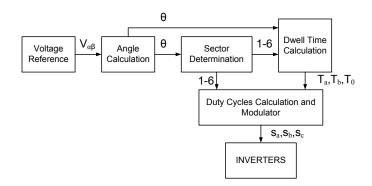

The idea behind two-level SVM has been explained in the previous chapter. The model of two-level SVM contains sector selection, dwell time calculation, duty cycle calculation and triangle modulator. The created switching signals are input to the inverter switches. A block diagram of the simulation model is depicted in Fig.3.2.

Figure 3.2: Block diagram of two-level SVM.

# **3.2.2** Parallel inverters with synchronized pulses

In Matlab/Simulink with Plecs all wires are ideal and equal components have the exact same value. This means that the case explained in 2.2 where components are ideal and the duty cycles are synchronized (identical) will be true for the simulation.

The two inverters use the same SVM to calculate the duty cycle from the voltage reference. This ensures that the duty cycles are identical for inverter 1 and inverter 2. The duty cycle is compared to a synchronized PWM module for each inverter.

## **3.2.3** Parallel inverters with interleaved pulses

The simulation model for parallel inverters with interleaved pulses is the same model as the one used for synchronized pulses, with exception for the PWM modules. In the PWM module the carrier wave for Inverter 2 is shifted with 180° compared to inverter 1.

# **3.2.4** Proposed three-level SVM for system of parallel connected inverters.

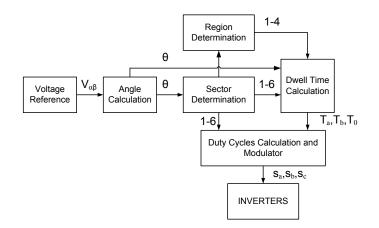

The analytical explanation of the three-level SVM has been presented in section 2.2.3. The simulation model is similar to two-level SVM. Additional part is region determination in which reference vector appears.

Figure 3.3: Block diagram of three-level SVM.

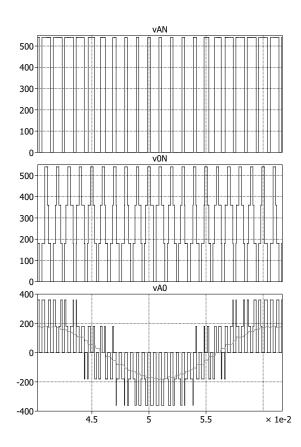

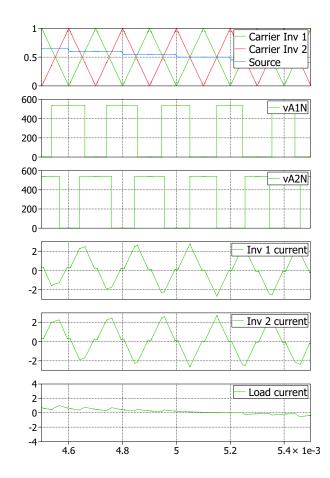

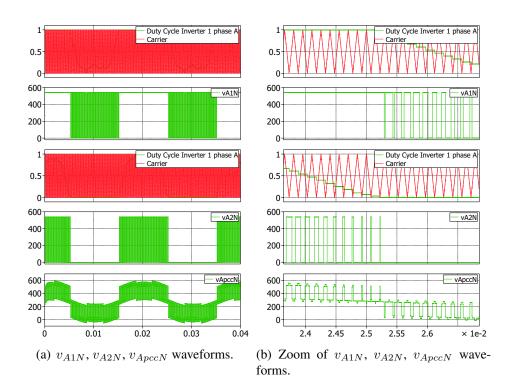

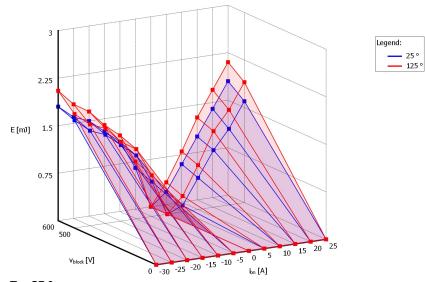

Because of the possibility to realize state  $H = 0.5V_{DC}$  in two ways (H1 and H2), three different ways of realization of three-level SVM has been designed. In first case the modulation has been realized, when H1 state is only used. The next modulation strategies have been designed in case when state H1 and H2 are swapping each other every sampling period or every second sampling period. The modulator of the first strategy is presented on the Fig.3.4(a) and 3.4(b).  $v_{A1N}$  and  $v_{A2N}$  contain continous states P and 0 for every t = 0.01. The voltage  $v_{ApccN}$  is created from three levels.

Figure 3.4: Three-level SVM using only H1 state.

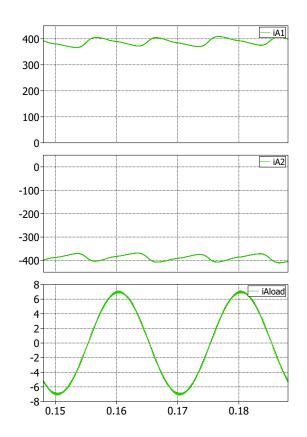

The Fig.3.5 presents the individual currents of inverters of phase A, when state H is realized in one way (H1 or H2). As it can be observed the big dc-offset is introduced in these currents with mean value around 380[A]. Even if the current on the load will have smooth sinusoidal waveform, this modulation technique can not be use in real system due to danger of destroying inverters.

Figure 3.5: Individual inerters and load A-phase current.

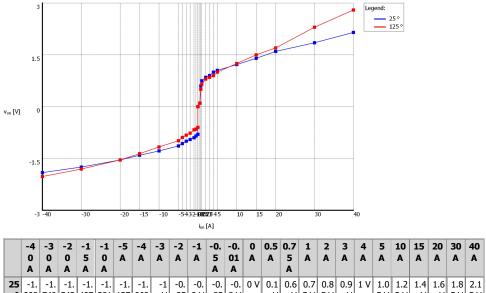

The next modulation strategy has been designed in case when state H1 and H2 are swapping each other every sampling period. This strategy introduce less stresses on the single power module. It can be observed from the Fig.3.6(a) and 3.6(b) that to realize state H two different pairs of the switches are used. The duty cycles are compared to two traingular carriers with different frequencies. Using  $f_{carrier} = 5[kHz]$  the number of switching signals sent to single leg of individual inverter was equal  $N_{switch} = 77$  during t = 0.02[s] which gives avarage switching frequency equal  $f_{switching} = 3.85[kHz]$ . By increasing carrier frequency to  $f_{carrier} = 6.7[kHz]$  it was possible to obtain  $f_{switching} = 5[kHz]$ .

$$f_{switching} = \frac{N_{switch}}{t} = \frac{77}{0.02} = 3850[Hz]$$

(3.1)