### Power Consumption in DFTs for OFDM Systems

MASTER THESIS APPLIED SIGNAL PROCESSING AND IMPLEMENTATION (ASPI)

> Group 1042 Peter August Simonsen Jes Toft Kristensen

# AALBORG UNIVERSITY

#### Institute for Electronic Systems Fredrik Bajers Vej 7B Telefon 96 35 98 36 Fax 98 15 36 62 http://www.esn.aau.dk

#### **Abstract:**

This Master Thesis of "Applied Signal Processing and Implementation" specialization at Aalborg University is an investigation of FFT algorithms in OFDM receivers and the algorithms power usage on customizable platforms.

The project focuses on mobile applications and cooperative radios, wherein only a part of the received frequency spectrum is needed. This can be exploited by special FFT algorithms to yield a lower operations count and intuitively a lower power consumption. However, what is not reflected in the operations count is the power-consumption of the controlling HW/SW. This thesis seeks to investigate the possibilities and tradeoffs, with regards to power usage, when computing a subset of the frequency spectrum, as opposed to the full spectrum.

Initially, the concept of cooperative radio and a signal model for OFDM is defined. Afterwards, two Fourier transform algorithms - a full Split-Radix FFT and an FFT algorithm computing only a subset of the spectrum (SFFT) - are examined and mapped to a Cyclone III FPGA architecture. Next, the power performance of each implementation is examined and an investigation into possible improvements is performed. In conclusion the algorithms are compared to a performance measure of computational complexity traditionally used to theoretically evaluate FFT algorithms.

The test results shows that the SFFT is not feasible with regards to power usage, without further improvements. These improvements include, among others, an enhanced power-off mechanism when subsystems are not in use. If a power-off state is introduced it is predicted that the SFFT becomes feasible and that computational complexity corresponds to the power usage for this implementation.

#### Title:

Power Consumption in DFTs for OFDM Systems

#### Project period:

P10, fall semester 2008

Project group:

ASPI 08gr1042

#### Members:

Peter August Simonsen peter@augusts.dk Jes Toft Kristensen jes@buskefjomp.dk

#### **Supervisors:**

Anders B. Olsen Jesper M. Kristensen

#### Copies: 6

Pages in report: 106

Appendices: 1 CD

Printed June 3, 2008

# AALBORG UNIVERSITET

#### Institut for Elektroniske Systemer Fredrik Bajers Vej 7B Telefon 96 35 98 36 Fax 98 15 36 62 http://www.esn.aau.dk

#### Synopsis:

Dette master-projekt på "Applied Signal Processing and Implementation" specialet ved Aalborg universitet er en undersøgelse af FFT algoritmer til OFDM modtagere og disse algoritmers energiforbrug på konfigurerbare platforme.

Projektet fokuserer på mobile kommunikation og kooperativ radio, hvor kun en del af det modtagne frekvensspektrum er nødvendigt at demodulere i modtageren. Dette kan udnyttes i specielle FFT algoritmer til at give en lavere beregningskompleksitet og intuitivt deraf et lavere effektforbrug. Men i beregningskompleksiteten er effektforbruget af det styrende HW/SW ikke inkluderet. Dette projekt undersøger de muligheder og afvejninger, mht. effektforbrug, når kun en del af frekvens-spektret beregnes, i modsætning til at beregne det fulde frekvensspektrum.

Til at begynde med introduceres kooperativ radio som koncept og en signalmodel for OFDM opstilles. Bagefter udforskes to FFT algoritmer - en Split-Radix FFT der beregner det fulde spektrum og en FFT algoritme der kun beregner en del af spektret (SFFT) - og disse implementeres på en Cyclone III FPGA arkitektur. Herefter udforskes hver implementations effektforbrug og mulige effektmæssige forbedringer undersøges. Afslutningsvist testes testes algoritmerne og resultaterne sammenlignes med beregningskompleksiteten, der traditionelt bruges til at evaluere FFT algoritmer.

Testresultaterne viser at SFFT algoritmen ikke er hensigtsmæssig mht. effektforbrug uden yderligere forbedringer. Disse forbedringer er blandt andet en forbedret power-off mekanisme, når undersystemer ikke er i brug. Hvis et power-off stadie introduceres, viser beregninger, at SFFT algoritmen bliver mere effektiv end Split-Radix FFT algoritmen og at beregningskompleksitet korrelerer med effektforbruget for denne implementation.

#### Titel:

Power Consumption in DFTs for OFDM Systems

Projekt periode: P10, forårssemester 2008

Projekt gruppe: ASPI 08gr1042

#### Medlemmer:

Peter August Simonsen peter@augusts.dk Jes Toft Kristensen jes@buskefjomp.dk

#### Vejledere:

Anders B. Olsen Jesper M. Kristensen

#### Kopier: 6

Sider i rapport: 106

Antal bilag: 1 CD

Printet June 3, 2008

### Preface

This report is documentation for the master thesis project in Applied Signal Processing and Implementation (ASPI) concerning "Power Consumption in DFTs for OFDM Systems" at the Institute of Electronic Systems at Aalborg University (AAU). The report is prepared by group 08gr1042 and spans from February 1st to June 4th, 2008. The project is supervised by Anders Brødløs Olsen and Jesper Michael Kristensen, both from Center for Software Defined Radio (CSDR) at AAU.

The report is divided into three parts. These parts correspond to the project phases of analysis, design or mapping, and evaluation of achieved results. The bibliography is found on page xiv with references to the bibliography in square brackets as in [08gr1042, 2008]. The cited source [08gr1042, 2008] is the accompanying CD attached to the inside of the report cover. This CD contains the code and test material produced during the project period and an electronic copy of this report in pdf.

Peter August Simonsen

Jes Toft Kristensen

### Contents

| Titlepage                                                                                                                                                                                                                                               | i                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Sitlepage (Danish)                                                                                                                                                                                                                                      | iii                                           |

| Preface                                                                                                                                                                                                                                                 | v                                             |

| List of Figures                                                                                                                                                                                                                                         | X                                             |

| List of Tables                                                                                                                                                                                                                                          | xii                                           |

| Notation                                                                                                                                                                                                                                                | xiii                                          |

| Nomenclature                                                                                                                                                                                                                                            | xiv                                           |

| Bibliography                                                                                                                                                                                                                                            | XV                                            |

| Introduction1.1Cooperative Radio and Multiuser OFDM1.2Project Purpose and Objectives1.3Problem Specification1.4DFT Algorithms1.5Implementation Prerequisites and Constraints1.6Project Methodology1.6.1Analysis1.6.2Architecture Mapping1.6.3Evaluation | · 2<br>· 3<br>· 3<br>· 4<br>· 4<br>· 5<br>· 6 |

| Analysis                                                                                                                                                                                                                                                | 9                                             |

| Application Analysis         2.1       System Model                                                                                                                                                                                                     | <b>11</b><br>. 11                             |

|   |            | 2.1.1    | Orthogonal Frequencies           | 11 |

|---|------------|----------|----------------------------------|----|

|   |            | 2.1.2    | An OFDM Downlink System          | 12 |

|   | 2.2        | Subcar   | rier Allocation Schemes          | 15 |

|   | 2.3        | System   | n Specification                  | 15 |

|   |            |          |                                  |    |

| 3 |            |          | nsform Algorithms                | 19 |

|   | 3.1        | U        | thm Selection                    | 19 |

|   | 3.2        |          | te Fourier Transform             |    |

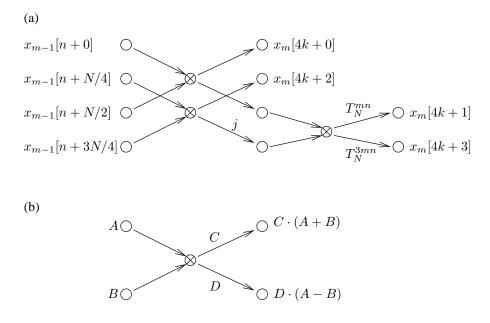

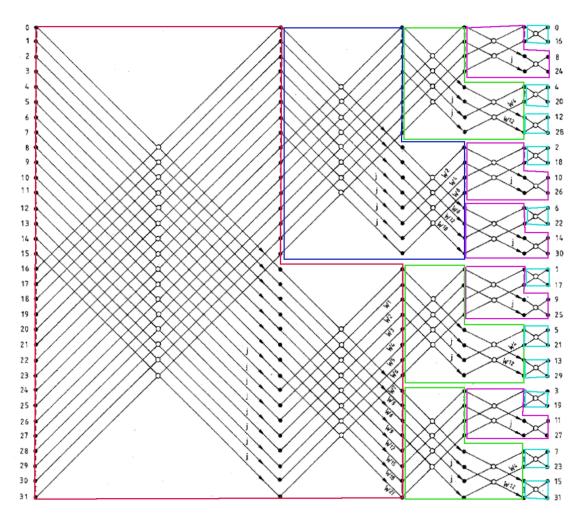

|   | 3.3        | -        | Radix FFT Algorithm              | 20 |

|   |            | 3.3.1    | SRFFT Derivation                 |    |

|   |            | 3.3.2    | Datapath Derivation              |    |

|   |            | 3.3.3    | Graphical Example                |    |

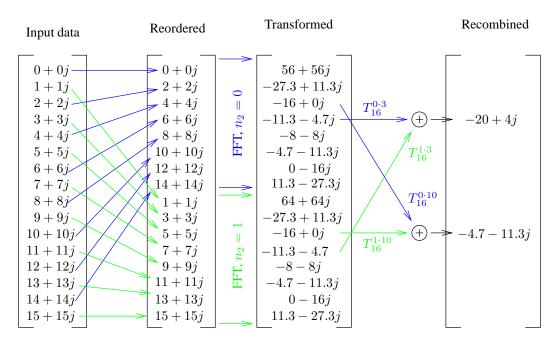

|   | 3.4        | ,        | en FFT                           | 23 |

|   |            | 3.4.1    | SFFT Derivation                  |    |

|   |            | 3.4.2    | Graphical Example                | 25 |

|   | 3.5        | -        | exity Analysis                   |    |

|   |            | 3.5.1    | DFT Complexity                   |    |

|   |            | 3.5.2    | Split-Radix FFT Complexity       |    |

|   |            | 3.5.3    | Sørensen FFT Complexity          | 26 |

|   |            | 3.5.4    | Comparison                       | 27 |

| 4 | A mal      | itaatuum | e Analysis                       | 31 |

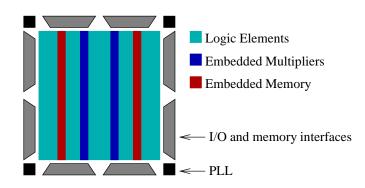

| 4 | 4.1        |          | yclone III FPGA                  | -  |

|   | 4.1<br>4.2 | •        | yclone III Starter Kit           |    |

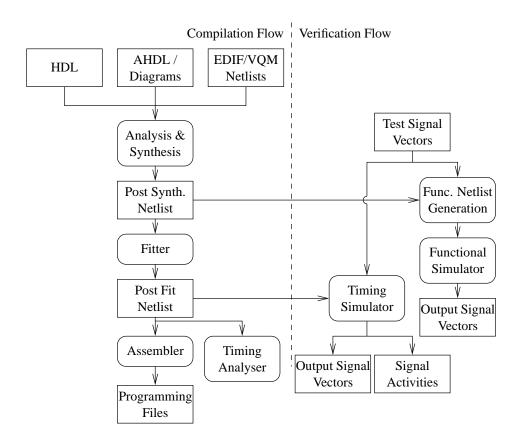

|   | 4.2<br>4.3 |          | Is oftware tools and design flow |    |

|   | 4.3        | 4.3.1    | Compilation Flow                 |    |

|   |            | 4.3.1    | Verification Flow                |    |

|   |            | 4.3.2    |                                  | 55 |

| 5 | Pow        | er Estin | nation and Measurement           | 37 |

|   | 5.1        | Power    | Simulations                      | 37 |

|   |            | 5.1.1    | Power models                     | 38 |

|   | 5.2        | Power    | Measurements                     | 41 |

|   | 5.3        | Power    | Performance Measure              | 42 |

|   |            |          |                                  |    |

|   |            | • / •    |                                  |    |

| Π | Alg        | gorithn  | n Mapping                        | 45 |

| 6 | Gen        | eral Ma  | opping                           | 47 |

|   | 6.1        |          | nment Description                | 47 |

|   |            | 6.1.1    | RAM                              | 47 |

|   | 6.2        |          | al Control Strategy              | 50 |

|   | 6.3        |          | er Representation                | 50 |

|   | 0.0        | 6.3.1    | Integer Word Length              | 51 |

|   |            | 6.3.2    | Fractional Word Length           | 53 |

|   |            | 0.5.2    |                                  | 55 |

|     | 6.4<br>6.5 | Arithmetic Operations       |    |

|-----|------------|-----------------------------|----|

| 7   | Split      | -Radix FFT Mapping          | 59 |

|     | 7.1        | Tasks                       | 59 |

|     | 7.2        | Datapath                    | 60 |

|     |            | 7.2.1 L-Butterfly           | 60 |

|     |            | 7.2.2 Two-Point Butterflies | 62 |

|     | 7.3        | Control Path                | 63 |

|     |            | 7.3.1 General Control Path  | 64 |

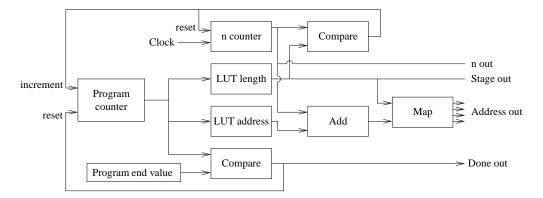

|     |            | 7.3.2 Address Generators    | 64 |

|     | 7.4        | Clock Domains Generation    | 67 |

|     | 7.5        | Summary                     | 67 |

|     |            | 7.5.1 Hardware Utilization  | 68 |

| 8   | Søre       | nsen FFT Mapping            | 71 |

|     | 8.1        | Tasks                       | 71 |

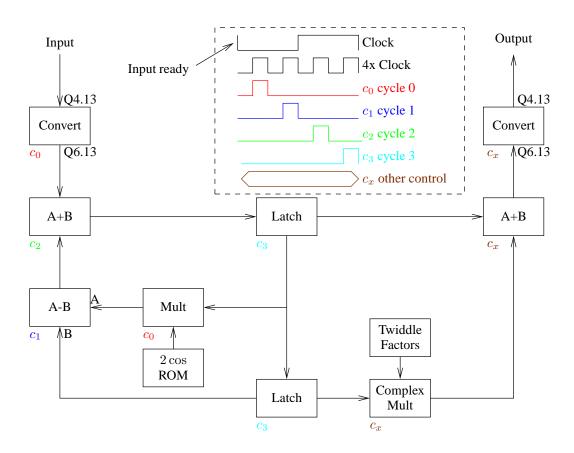

|     | 8.2        | Datapath                    | 72 |

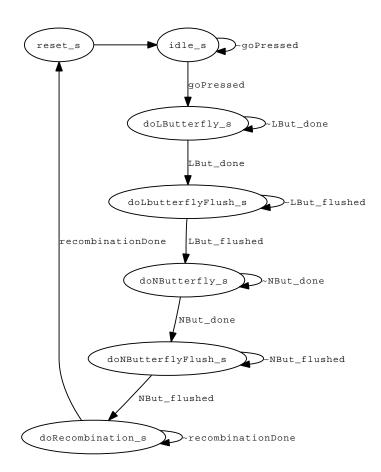

|     | 8.3        | Control Path                | 76 |

|     | 8.4        | Clock Adjustment            | 79 |

|     | 8.5        | Summary                     | 79 |

|     |            | 8.5.1 Hardware Utilization  | 79 |

| III | E          | valuation                   | 85 |

| 9  | Test  |         |                                    |   | 87    |

|----|-------|---------|------------------------------------|---|-------|

|    | 9.1   | Split R | Radix FFT                          |   | . 87  |

|    |       | 9.1.1   | Functional Verification            |   | . 87  |

|    |       | 9.1.2   | Power Simulations                  |   |       |

|    |       | 9.1.3   | Power Measurements                 |   | . 89  |

|    |       | 9.1.4   | Discussion                         |   | . 91  |

|    | 9.2   | Sørens  | sen FFT                            |   | . 92  |

|    |       | 9.2.1   | Functional Verification            |   | . 92  |

|    |       | 9.2.2   | Power Simulations                  |   | . 94  |

|    |       | 9.2.3   | Power Measurements                 |   | . 95  |

|    |       | 9.2.4   | Discussion                         |   | . 95  |

|    | 9.3   | Summa   | nary                               | • | . 97  |

| 10 | Desig | gn Spac | nce Exploration                    |   | 99    |

|    | 10.1  | Basis f | for Analysis                       |   | . 99  |

|    |       |         | lation Summary                     |   |       |

|    | 10.3  | Perform | rmance by Hierarchy                |   | . 100 |

|    | 10.4  | Exami   | ination of the SFFT Implementation | • | . 102 |

|    | 10.5 Summary | <br>••• | • • | ••• | • | <br> | ••• | • | <br>• | ••• | <br>• | • • | • | • | ••• | • | ••• | • |  |     |

|----|--------------|---------|-----|-----|---|------|-----|---|-------|-----|-------|-----|---|---|-----|---|-----|---|--|-----|

| 11 | Conclusion   |         |     |     |   |      |     |   |       |     |       |     |   |   |     |   |     |   |  | 105 |

# List of Figures

| 1.1 | Multiuser Cooperative Radio Scenario                       | 1  |

|-----|------------------------------------------------------------|----|

| 1.2 | Subcarrier allocation example for multiuser OFDM system.   | 2  |

| 1.3 | Project Methodology Overview                               | 4  |

| 1.4 | $A^3$ model                                                | 5  |

| 1.5 | FSMD structure for design mapping                          | 6  |

| 1.6 | Abstraction model for algorithm mapping                    | 7  |

| 2.1 | OFDM Downlink System Model                                 | 12 |

| 2.2 | Subcarrier allocation principles                           | 16 |

| 2.3 | Principal test system                                      | 16 |

| 3.1 |                                                            | 23 |

| 3.2 | 32 point SRFFT example                                     | 24 |

| 3.3 | SFFT example                                               | 26 |

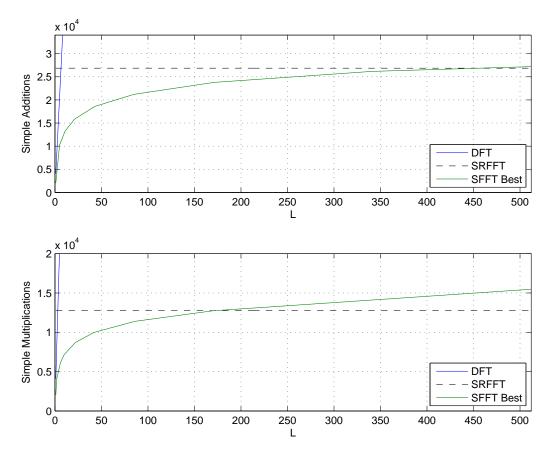

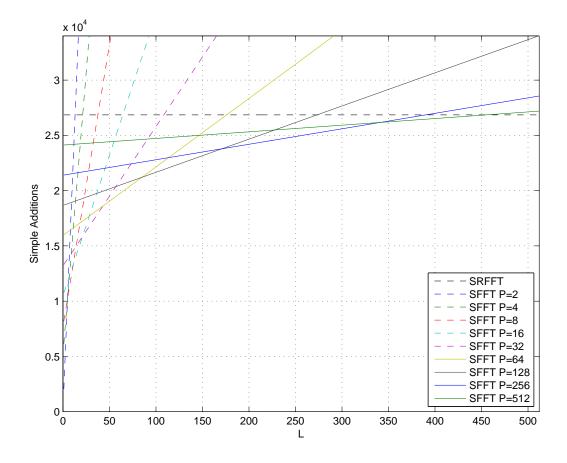

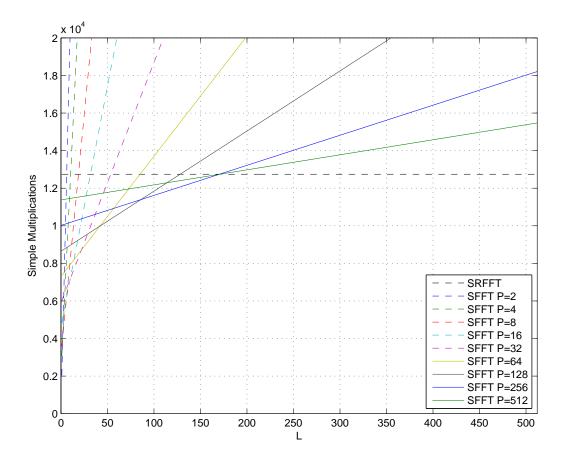

| 3.4 | Comparison of complexities                                 | 27 |

| 3.5 | Comparison of complexities, simple additions               | 28 |

| 3.6 | Comparison of complexities, simple multiplications         | 29 |

| 4.1 | Structural Cyclone III floorplan                           | 31 |

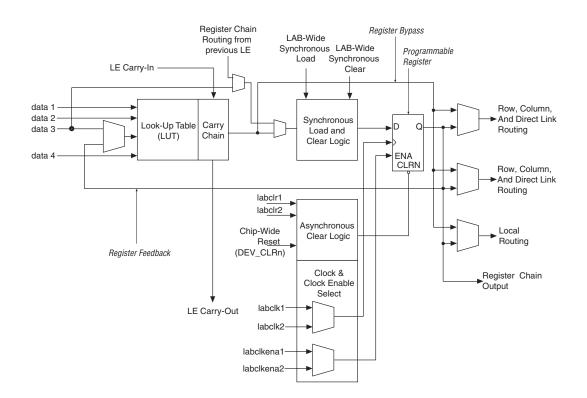

| 4.2 | Structure of a logic element                               | 32 |

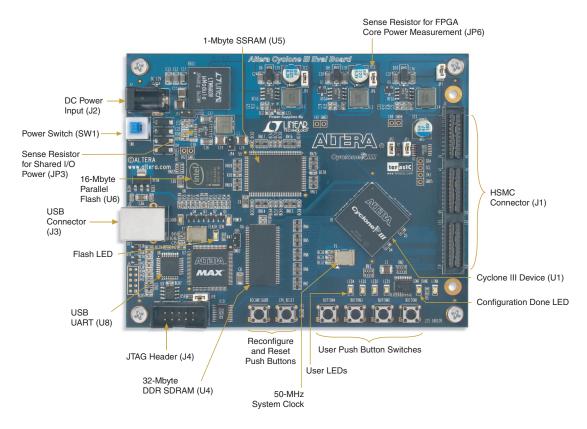

| 4.3 | Overview of the Cyclone III Starter Kit board              | 33 |

| 4.4 | Quartus II compilation flow                                | 35 |

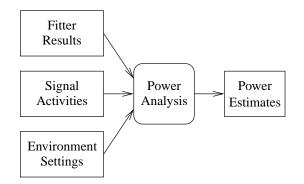

| 5.1 | Power Simulations Setup                                    | 38 |

| 5.2 |                                                            | 39 |

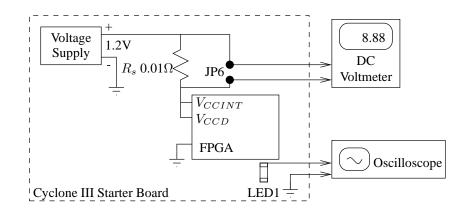

| 5.3 | Power Measurements Setup                                   | 42 |

| 6.1 | General interface between FFT and OFDM demodulation system | 48 |

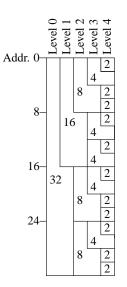

| 6.2 | Structure of data RAM block                                | 49 |

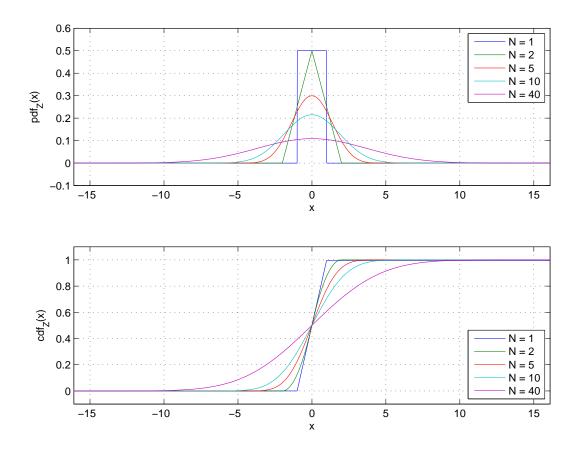

| 6.3 | Sum of uniform random variables                            | 54 |

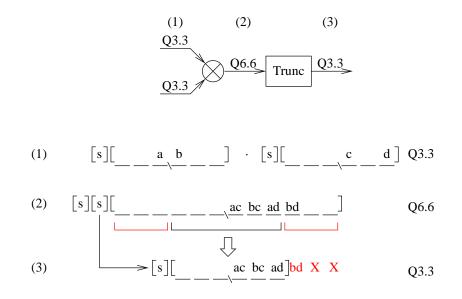

| 6.4 | Example of multiplication and truncation                   | 55 |

LIST OF FIGURES

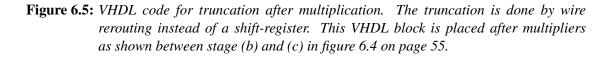

| 6.5  | VHDL code for truncation after multiplication                               | 57 |

|------|-----------------------------------------------------------------------------|----|

| 7.1  | 1                                                                           | 60 |

| 7.2  | Tasks for SRFFT                                                             | 61 |

| 7.3  | Implementation of L-shaped butterfly for SRFFT                              | 62 |

| 7.4  | 2-point butterfly implementation                                            | 63 |

| 7.5  | SRFFT controlling state machine                                             | 65 |

| 7.6  | L-butterfly address generator implementation                                | 66 |

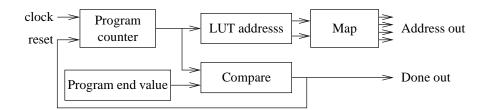

| 7.7  | Structure of 2-point butterfly address generator implementation             | 67 |

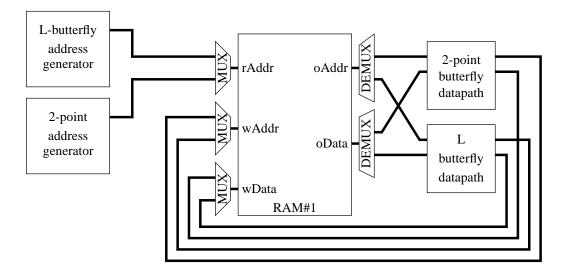

| 7.8  | Overview of SRFFT system                                                    | 68 |

| 8.1  | Tasks for SFFT                                                              | 72 |

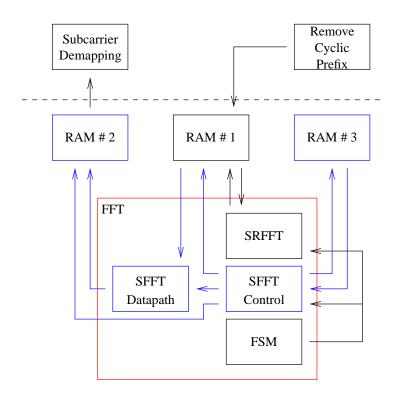

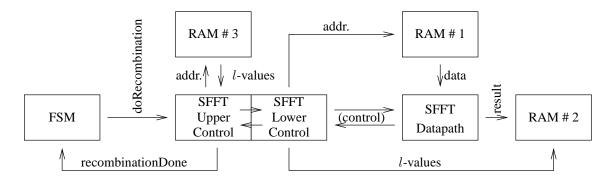

| 8.2  | SFFT in conjunction with system interfaces.                                 | 73 |

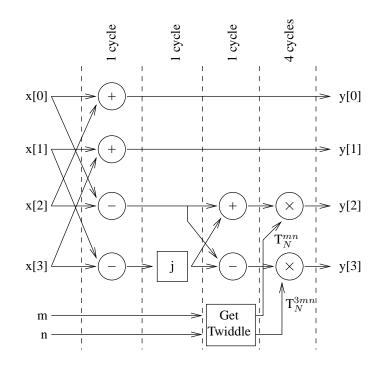

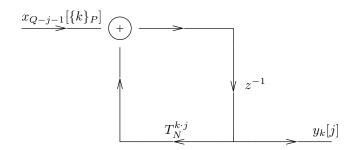

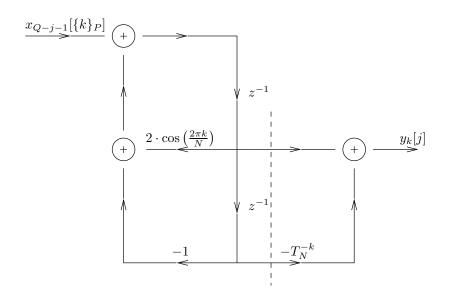

| 8.3  | SFFT Flowgraph A                                                            | 74 |

| 8.4  | SFFT Flowgraph B                                                            | 74 |

| 8.5  | SFFT recombination datapath                                                 | 76 |

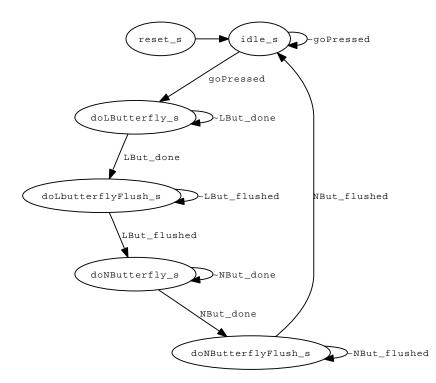

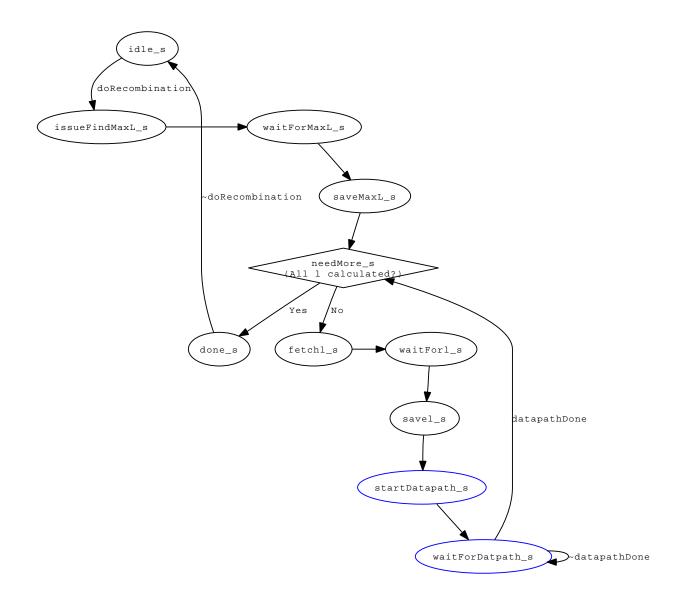

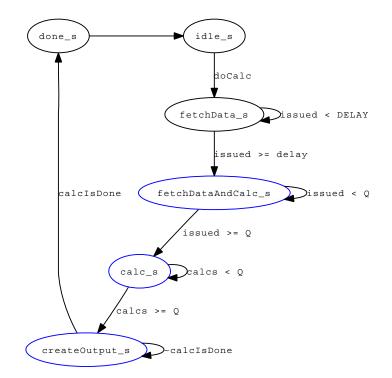

| 8.6  | SFFT controlling state machine                                              | 77 |

| 8.7  | Upper and lower control path of the SFFT                                    | 78 |

| 8.8  | SFFT upper control state machine                                            | 81 |

| 8.9  | SFFT lower control state machine                                            | 82 |

| 8.10 | Example state machine state in VHDL code, with bit reversal                 | 83 |

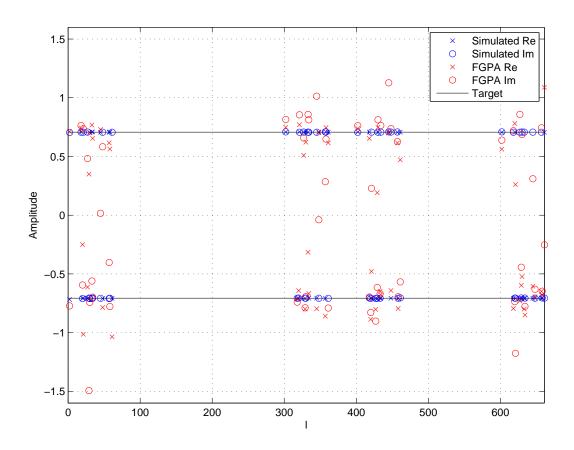

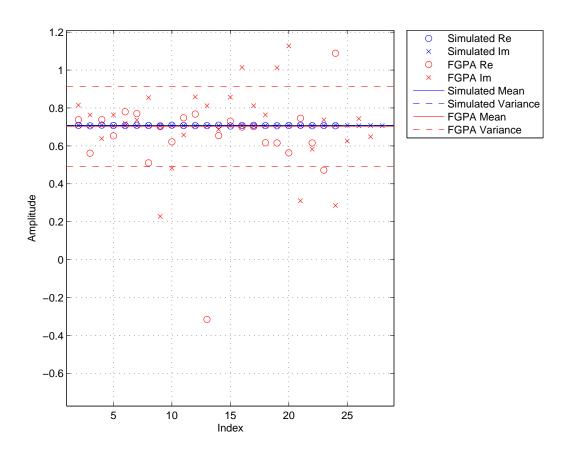

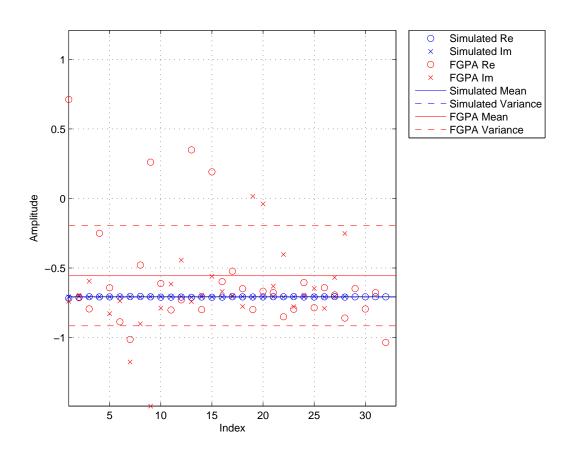

| 9.1  | Simulated and implemented SFFT output                                       | 93 |

| 9.2  | Simulated and implemented SFFT output for upper constellation point         | 94 |

| 9.3  | Simulated and implemented SFFT output for lower constellation point         | 95 |

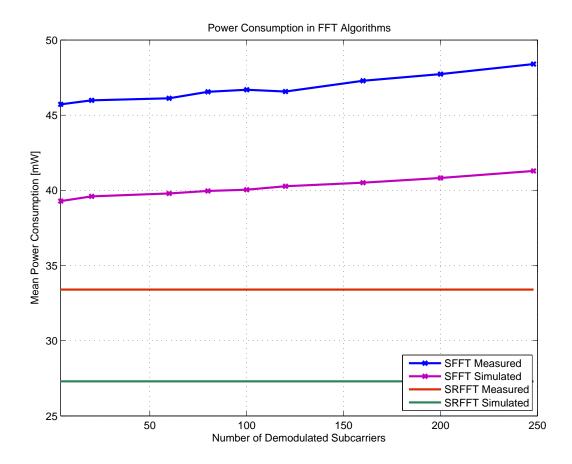

| 9.4  | Results of measurements and simulations of SRFFT and SFFT power consumption | 97 |

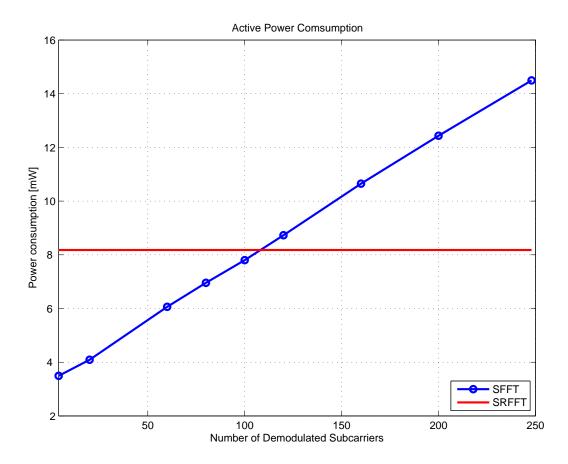

| 10.1 | Power consumption for FFT algorithms assuming zero idle power               | 01 |

## List of Tables

| System constraints for FFT size and timing performance | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cyclone III device specifications                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Maximum achieved values in the SRFFT                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Hardware utilization in the SRFFT system               | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SFFT datapath comparisons                              | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Cycle count for simulation of SFFT 7                   | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Hardware utilization in the SFFT system                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Power simulation results, full clock                   | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Power simulation results, reduced clock                | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Power measurement results for SRFFT, full clock        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Power measurement results for SRFFT, reduced clock     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Simulation and measurement results summary             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1                                                      | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                        | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Measurement results for SFFT                           | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Power analysis summary                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Power analysis by hierarchy                            | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SFFT power usage by hierarchy and multiplicity         | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SFFT datapath power usage                              | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                        | Cyclone III device specifications       3         Maximum achieved values in the SRFFT       5         Hardware utilization in the SRFFT system       6         SFFT datapath comparisons       7         Cycle count for simulation of SFFT       7         Hardware utilization in the SFFT system       7         Cycle count for simulation of SFFT       7         Hardware utilization in the SFFT system       8         Power simulation results, full clock       8         Power simulation results, reduced clock       8         Power measurement results for SRFFT, full clock       9         Power measurement results for SRFFT, reduced clock       9         Simulation and measurement results summary.       9         Mean and variances for the SFFT simulation and implementation       9         Simulation results for SFFT.       9         Measurement results for SFFT       9         Power analysis summary       10         Power analysis by hierarchy       10         SFFT power usage by hierarchy and multiplicity       10 |

### Notation

| Symbol                    | Association                                               |

|---------------------------|-----------------------------------------------------------|

| 8                         | Mathematical variables in italics                         |

| 10101001 <sub>b</sub>     | A binary number, representing the integer 169             |

| $ \bar{f A} $             | The matrix A                                              |

| $\overline{\mathbf{b}}$   | The vector b                                              |

| $\{x\}_y$                 | $x \mod y$                                                |

|                           | The expression of $a$ ceiled                              |

| $\lfloor a \rfloor$       | The expression of $a$ floored                             |

| $\mu(x)$                  | The mean of $x$                                           |

| $\mathbb{F}\left[a ight]$ | The discrete Fourier transform of $a$                     |

| ~ statement               | The binary negated statement                              |

| [08gr1042, 2008, p. 42]   | Bibliographic reference to index [08gr1042, 2008] page 42 |

The notation used throughout this report is documented below.

#### PLL Phase Locked Loop, page 31

SFFT Sørensen FFT, page 23

SQNR Signal to Quantization Noise Ratio, page 87

Twiddle Factor , page 20

### Nomenclature

- BS Base Station, page 1

- cdf Cumulative Distribution Function, page 53

- DFT Discrete Fourier Transform, page 20

- FFT Fast Fourier Transform, page 3

- FPGA Field Programmable Gate Array, page 4

- FSM Finite State Machine, page 6

- FSMD Finite State Machine with Datapath, page 6

- HDL Hardware Description Language, page 34

- ISI InterSymbol Interference, page 13

- LAB Logic Array Block, page 32

- LE Logic Element, page 32

- LSB Least Significant Bit, page 56

- MAC Multiply and ACcumulate, page 72

- MS Mobile Station, page 1

- OFDM Orthogonal Frequency-Division Multiplexing, page 2

- pdf Probability Density Function, page 52

### Bibliography

- The Project Group 08gr1042, June 2008. Additional materials for the project can be found on the accompanying CD.

- AAU. JADE Project Deliverable: D3.1.1. Aalborg University, 2004.

- Agilent. Agilent 34401A Multimeter -Product Overview. Agilent Technologies, 2007. get from: http: //cp.literature.agilent.com/ litweb/pdf/5968-0162EN.pdf.

- Altera. An OFDM FFT Kernel for WiMAX

Application note 452. Altera Corporation, 1.0 edition, 2007a. get

from: http://www.altera.com/

literature/an/an452.pdf.

- Altera. Cyclone III FPGA Starter Kit User Guide. Altera Corporation, 1.0.0 edition, 2007b.

- Altera. Nios II Processor Reference Handbook. Altera Corporation, 2008a. get from: http://www.altera.com/ literature/hb/nios2/n2cpu\_ nii5v1.pdf.

- Altera. *Cyclone III Device Handbook*. Altera Corporation, 2007c.

- Altera. *Quartus II Version 7.2 Handbook,*. Altera Corporation, 7.2.0 edition, 2007d.

- Altera. Quartus II Device Support Release Notes. Altera Corporation, 2008b. get from: http://www.altera.com/ literature/rn/rn\_qts\_72sp2\_ dev\_support.pdf.

- Altera. *FPGA Power Management and Modeling Techniques*. Altera Corporation, 1.0 edition, 2007e.

- Jeffrey G. Andrews. *Fundamentals of WiMAX*. Prentice Hall, 2007. ISBN 0-13-222552-2.

- Abdellatif Bellaouar and Mohammed I. Elmasry. Low-Power Digital VLSI Design. Kluwer Academic Publishers, 1st edition, 1995. ISBN 0-7923-9587-5.

- David M. Bradley and Ramesh. C. Gupta. On the Distribution of the Sum of n Non-Identically Distributed Uniform Random Variables. Department of Mathematics and Statistics, University of Maine, Orono, ME, 2007. URL citeseer.ist.psu.edu/ 449216.html.

- Suvra Sekhar Das. Techniques to Enhance Spectral Efficiency of OFDM Wireless Systems. Center for TeleInFrastruktur (CTIF), September 2007. ISBN 87-92078-07-9.

- P. Duhamel and H. Hollmann. 'Split Radix' FFT Algorithm. IEEE, 1 edition, 1983. Electronics Letters, 5th January 1984, Vol. 20, No. 1.

- Pierre Duhamel. Implementation of "Split-Radix" FFT Algorithms for Complex, Real and Real-Symmetric Data. IEEE, 1986. IEEE Transactions on acoustics, speech and signal processing, vol. ASSP-34, No. 2, April 1986.

- Daniel D. Gajski. *Principles of Digital Design*. Prentice Hall, 1997. ISBN 0-13-242397-9.

BIBLIOGRAPHY

- Steven G. Johnson and Matteo Frigo. A modified split-radix FFT with fewer arithmetic operations. IEEE, 1st edition, 2007. IEEE Trans. Signal Processing 55 (1), 11-119.

- Youngok Kim and Jaekwon Kim. Low Complexity FFT Schemes for Multicarrier Demodulation in OFDMA Systems. IEICE, 1st edition, 2007. IEICE Transactions on Communication, November 2007, Vol. E90-B, No. 11, pp. 3290-3293.

- E. Lawrey. *Multiuser OFDM*. ISSPA, 1st edition, 1999. Proc. IEEE International Symbiosum on Signal Processing and its Applications, August 1999, Vol. 2, pp. 761-764.

- John D. Markel. FFT Pruning. IEEE, 1971. IEEE Transactions on Audio and Electroacoustics, Vol. AU-19, No. 4, December 1971.

- Yannick Le Moullec. DSP Design Methodology. AAU, 2007. Lecture notes for mm1 of course in DSP Design Methodology, ASPI8-4 http: //kom.aau.dk/~ylm/aspi8-4/ aspi8-4-part1-2007.pdf.

- Charles D. Murphy. Low-Complexity FFT Structures for OFDM Trancievers. IEEE, 2002. IEEE transactions on communication, vol.50, no. 12, December 2002, pp. 1878-1881.

- Erik L. Oberstar. *Fixed-Point Representation & Fractional Math.* Oberstar Consulting, 1.2 edition, 2007.

- Alan V. Oppenheim and Ronald W. Schafer. *Discrete-Time Signal Processing*. Prentice-Hall Inc., 2nd edition, 1998.

- Henrik Schulze and Christian Lüders. Theory and Applications of OFDM and CDMA. John Wiley & Sons, Ltd., 2005. ISBN 0-470-85069-8.

- K. Sam Shanmugan and A. M. Breipohl. *Random Signals, Detection, Estimation and Data Analysis.* Wiley and Sons, 1st edition, 1988. ISBN 0-471-81555-1.

- David P. Skinner. *Pruning the Decimation in-Time FFT Algorithm*. IEEE, 1976. IEEE transactions on acoustics, speech and signal processing, April 1976, pp. 193-194.

- A. N. Skodras and A. G. Constantinides. *Efficient computation of the split-radix FFT*. IEEE, 1 edition, 1992. IEEE PROCEEDINGS-F, Vol. 139, No. 1, FEBRUARY 1992.

- Henrik V. Sørensen and C. Sidney Burrus. *Efficient Computation of DFT with Only a Subset of Input or Output Points*. IEEE, 1st edition, 1993. IEEE Transactions on Signal Processing, Vol 41. No 3, March 1993.

- John F. Wakerly. *Digital Design, Principles and Practices.* Prentice Hall, 3rd edition, 2001. ISBN 0-13-090772-3.

Chapter ]

### Introduction

In the introduction the purpose, objectives and methodology of the project is presented. First, an informal introduction to multiuser OFDM is given along with the motivation for examining FFT algorithms and FPGA implementations of these in a power consumption context. Next, fundamental project delimitations are introduced regarding FFT algorithms for examination and FPGA platform for implementation are presented. Further discussions of these delimitations are carried out in the analysis part of the report. Finally, the project methodology and report structure is presented.

#### 1.1 Cooperative Radio and Multiuser OFDM

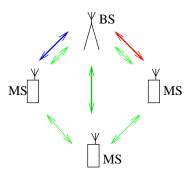

Figure 1.1 shows a wireless communication scenario, where multiple users, or mobile stations (MS), are communicating with a base station (BS) and each other.

**Figure 1.1:** Multiuser Cooperative Radio Scenario. The communication path may be either directly from base station to mobile station or data can be relayed through other mobile stations to get to the destination.

The inter MS communication may both be data exchanged between the local MSs, or data from the base station relayed through one MS to the destination. If for instance the direct channel from BS to destination MS cannot accommodate the required bandwidth. Such a system requires some cooperation between devices and a method for dividing the channel between BS and MS links.

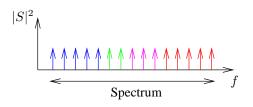

In Orthogonal Frequency-Division Multiplexing (OFDM) the spectrum or channel is divided into a set of mutually orthogonal subcarriers, which are used to modulate the data to be transmitted. In Multiuser OFDM the subcarriers may be assigned to different communication paths as exemplified in figure 1.2, where the spectrum are divided into blocks of subcarriers for each path.

Figure 1.2: Example of subcarrier allocation for each communication path, where each color is assigned to a different path.

In OFDM the Discrete Fourier Transform (DFT) and it's inverse counterpart plays a significant role, as it is used to modulate data symbols onto the subcarriers in the transmitter and demodulate the data at the receiver. A more elaborate analysis of an OFDM system and the DFT function herein is presented in chapter 2.

#### **1.2 Project Purpose and Objectives**

In this project, focus is turned to the DFT block of the OFDM receiver used to demodulate the system subcarriers. A range of low complexity Fast Fourier Transform algorithms have been developed to reduce to number of computations when calculating the DFT, both for calculation of all subcarrier transforms and for calculation of only a subset of the subcarrier transforms, which is relevant when only the data designated for one MS is of interest.

Classic evaluation methods of Fourier transform algorithms intended for OFDM systems are based on number of additions and multiplications spent calculating the actual transform [Murphy, 2002]. While this measure gives a theoretic indication of which algorithm is optimal in a given situation, the measure based on needed calculation only, does not take into account the control structures needed to manage and ensure timing of input and output data for the calculation units in an implementation of the algorithms.

When turning focus to implementations of algorithms, the cost function changes from counting calculations to a combination of algorithm execution time, hardware area utilization (e.g. logic units in FPGAs, memory usage), and power consumption:

$$Cost = Power \times Area \times Time$$

(1.1)

Since keeping power consumption as low as possible is key in battery powered mobile devices, the purpose of this project is to evaluate different DFT schemes for OFDM or Cooperative Radios with regards to power consumption in FPGA implementations. Requirements for the DFT is taken from the WiMAX standard, to set constraints on calculation time which is based on a standard targeted at mobile devices.

The goal of applying a power consumption measure to FPGA implementations of Fourier transform algorithms is to investigate how the theoretical measure of computational complexity compares to performance achievements of actual implementations. Evaluating the performance of these implementations, across a variable number of needed subcarriers and using a power measure, will show in which situation it is advantageous to use each of the investigated algorithms.

The results of these implementation evaluations are finally compared with the computational complexity measure to determine if each of the investigated algorithms have more or less relevance in actual implementations than their computational complexity suggest.

#### **1.3** Problem Specification

How well does the performance measure of computational complexity compare to power consumption in FPGA implementations of DFT algorithms for multiuser OFDM?

#### **1.4 DFT Algorithms**

For this project two Fast Fourier Transform (FFT) algorithms are chosen for comparison. The algorithms considered in this project are:

#### • Split-Radix Fast Fourier Transform (SRFFT):

One approach is to calculate the full transform, regardless of how many subcarriers, that are of interest. Several algorithm exist which can perform this task. The radix-2 FFT is a recursive decomposition into two DFTs of N/2 length, the radix-4 makes use of decompositions into four N/4 DFT, and the Split-Radix FFT employs decomposition into one N/2 and two N/4 DFTs. The SRFFT has proven to feature one of the lowest computational complexities of the mentioned algorithms [Duhamel and Hollmann, 1983] and is therefore chosen for investigation in this project.

#### • "Sørensen" Fast Fourier Transform (SFFT):

As mentioned above, one user may only need to receive the data sent using a subset of the available subcarriers. Therefore methods calculating only a subset of the FFT have been developed, where the SFFT [Sørensen and Burrus, 1993] reduces the number of calculations by only calculating decomposition into a set of small FFTs and then recombining the results for only the subset of subcarrier that are of interest.

Each of the investigated algorithms are elaborated in sections 3.3 and 3.4

#### **1.5 Implementation Prerequisites and Constraints**

The DFT algorithms are examined when implemented on a Field Programmable Gate Array (FPGA) platform. The configurability of FPGAs allows for faster development of systems combining predeveloped building blocks, like a DFT, to compose a system fitting the application in question. With FPGA families emerging developed for low power consumption (e.g. Altera Cyclone III) FPGAs become applicable in battery powered mobile devices. Therefore, an FPGA platform is used to evaluate the power consumption of the examined DFT algorithms.

The selected platform is the Altera Cyclone III Starter Kit. This selection is based on the toolchain, support in the form of the Quartus II and associated software, and knowledge available at Aalborg University.

Using a development kit allows for focusing on the mapping of algorithms onto the architecture, and evaluating and comparing these implementations. This focus comes at the cost of reduced possibilities for dimensioning the system to fit the requirements and may introduce some unnecessary overhead for the design to fit the hardware. Still, the development board provides a well defined platform for comparison of the algorithms and the resources saved from not designing the platform can be used to focus on answering the problem specification stated in section 1.3.

#### 1.6 Project Methodology

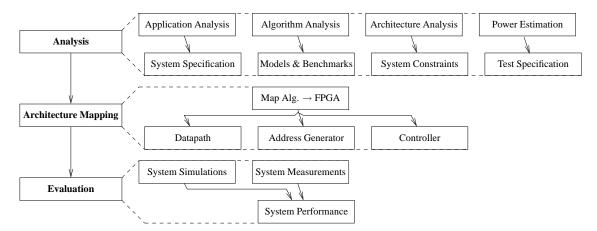

The purpose of the design methodology is to supply a structured approach to the analysis, design and evaluation of results obtained in the project. Therefore, the following structure of analysis, design and evaluation also reflects the structure of this report. The project methodology is depicted in figure 1.3.

Figure 1.3: Project Methodology overview. For each part of the project - Analysis, Mapping and Evaluation - tasks and results are depicted. Architecture Mapping and Evaluation are repeated for each algorithm.

#### 1.6.1 Analysis

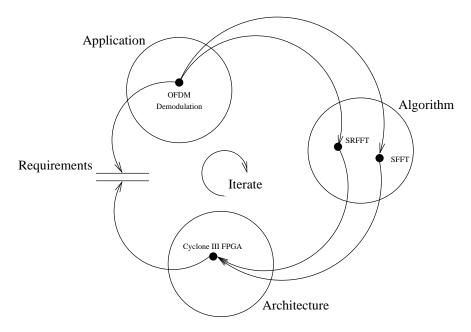

The project analysis makes use of the three domains of the  $A^3$  model [Moullec, 2007], Application, Algorithm, and Architecture, shown in figure 1.4, to divide the system analysis into three main parts:

**Figure 1.4:**  $A^3$  model for project.

• Application:

In the application domain, an analytical OFDM model is presented to determine the context in which, the FFT implementations are to function. Based on this system model, the functional requirements of the FFT block, and specifications and constraints of a test system for validation is determined.

• Algorithm:

In the algorithms domain, the two Fourier transform algorithms used to solve the specified task of the OFDM FFT block are analyzed. The analysis focus on derivation of the structure of computations and computational complexity of each algorithm. The computational complexity measure of each algorithm is evaluated in same test cases as are defined for power analysis of the implementations for comparison and evaluation. Furthermore, each algorithm is modelled in C where an outline of a datapath and control structure for the following mapping is designed.

• Architecture:

In the architecture domain, the FPGA hardware used to implement the investigated FFT algorithms are analyzed. The characteristics of the FPGA development kit of choice, i.e.

available hardware and system limitations, are examined. Next the development tools and methods available for the platform are described, as are the possibilities for simulating and measuring the power consumption of each algorithm implementation.

#### 1.6.2 Architecture Mapping

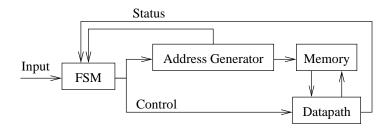

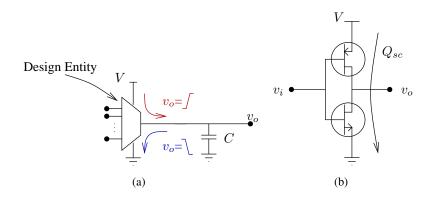

The system design in this project is concerned with mapping each of the algorithms onto the FPGA architecture. The mapping is done using a datapath and control structure approach, as shown in figure 1.5. This mapping method is based on the Finite State Machine with Datapath (FSMD) approach to digital design presented in [Gajski, 1997, page 320-322].

**Figure 1.5:** General structure model for design mapping of algorithms using a finite state machine for controlling an address generator and datapath.

Each mapping design consists of a datapath, where the algorithm calculation units are contained. The control structure consists of a Finite State Machine (FSM), which is used to setup the datapath to do the relevant operations on the data, and an address generator, used to retrieve data from memory.

This approach differs slightly from [Gajski, 1997, page 320-322] since program counters keeping track of algorithm progress and the logic used to generate addresses for memory access are extracted from the datapath and handled explicitly in the project. This additional partitioning of the datapath is done in order be able to design the calculation units of the data path separately and next design memory handling units to fit these calculation units.

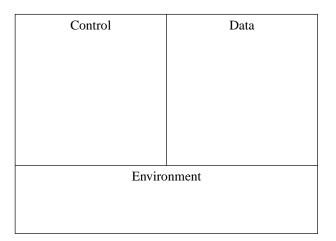

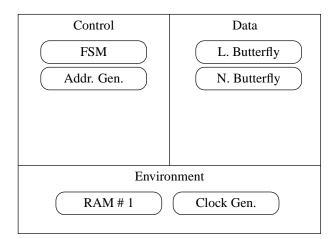

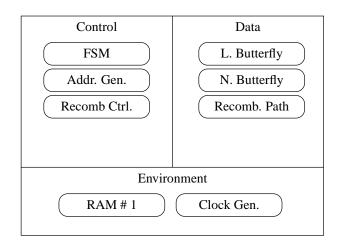

When partitioning the design in the algorithm part II, the design is divided into three domains and shown in figure 1.6 on the facing page; environment, control and data domains.

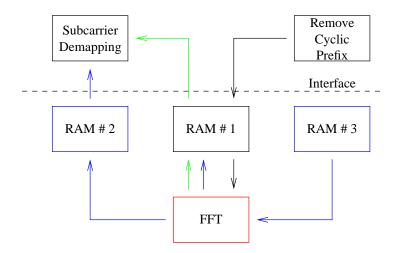

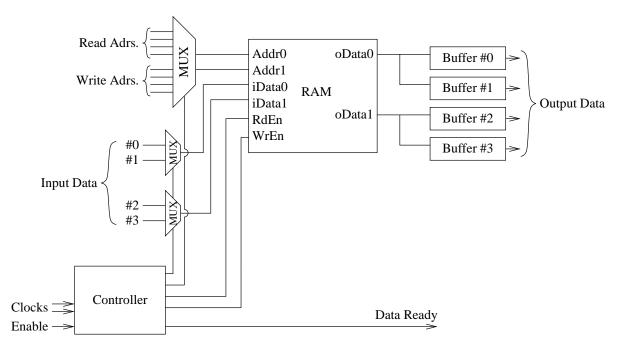

The environment domain contains peripherals and interfaces to the implemented algorithms. As the algorithms only perform the FFT task in the OFDM demodulation, see figure 2.1 on page 12, the environment domain provides a convenient representation of the surrounding system and requirements which are somewhat common to the data and control domains. In effect, the environment domain thus contains the memory part of figure 1.5 and system clock domains. The data domain contains the datapaths of the mapped algorithm and the control domain contains the FSM controller and address generators for memory access.

**Figure 1.6:** The abstraction model used to describe algorithm mapping. The model contains the three domains: environment, control path and datapath. These domains and their interfaces are used as a basis for describing the mapping from mathematical algorithm to FPGA implementation.

#### 1.6.3 Evaluation

The final part of the project is concerned with verifying the functionality of the implemented algorithms and evaluating the systems with regards to the power performance measure setup in the analysis. This evaluation is carried out using both the available power analysis tool provided by the FPGA manufacturer and by measurements of the FPGA power consumption in a set of test scenarios that ultimately allows for comparing the obtained results with the theoretical performance derived from algorithm computational complexity.

This comparison is used to answer the problem specification stated in section 1.3, and to evaluate the coherence between algorithm computational complexity and power consumption.

### Part I

### Analysis

This part moves the problem specification previously defined through the application level. This includes a closer examination of the system model, examination of the Fourier transform algorithms and the FPGA, both functional and power-wise

Initially the concept of OFDM is introduced and the system is specified. Afterwards two FFT algorithms are examined mathematically and finally compared complexity-wise. Chapter 4 introduces the FPGA platform and associated tools while chapter 5 presents a power performance simulation and measurement.

#### Contents

| 2 | 2.1       System Model       1         2.2       Subcarrier Allocation Schemes       1                                                                                                | 1<br>11<br>15<br>15              |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 3 | 3.1       Algorithm Selection       1         3.2       Discrete Fourier Transform       2         3.3       Split-Radix FFT Algorithm       2         3.4       Sørensen FFT       2 | 19<br>19<br>20<br>20<br>23<br>25 |

| 4 | 4.1 The Cyclone III FPGA       3         4.2 The Cyclone III Starter Kit       3                                                                                                      | 81<br>31<br>33<br>34             |

| 5 | 5.1 Power Simulations       3         5.2 Power Measurements       4                                                                                                                  | 87<br>87<br>41<br>42             |

# Chapter 2

### **Application Analysis**

The application analysis presents the system model which is an OFDM downlink transmission scheme, that can be used in cooperative radios. Based on this model a test system is specified to enable testing the functionality of the proposed DFT algorithms.

#### 2.1 System Model

This section is a general introduction to the OFDM downlink scenario considered in this project. First the concept of orthogonal frequencies is explained, followed by how this principle is used to communicate data symbols from a base station through a wireless channel to a mobile station, where only a subset of the subcarriers is of interest. The main sources on which the following presentation of OFDM is based are [Schulze and Lüders, 2005, sec. 4.1] and [AAU, 2004, chap. 2].

#### 2.1.1 Orthogonal Frequencies

Orthogonal Frequency Division Multiplexing (OFDM) is a framework for multicarrier transmission where several data symbols are transmitted at the same time by modulation with orthogonal subcarriers. In a system with N subcarriers, the baseband signal for one OFDM symbol period  $(T_u)$  may be written as:

$$s(t) = \sum_{n=-N/2}^{N/2-1} X_n e^{j\frac{2\pi nt}{T_u}} , 0 \le t \le T_u$$

(2.1)

where  $X_n$  is the *n*'th data symbol. In the frequency domain the signal has the form of:

$$S(\omega) = \frac{1}{\sqrt{T_u}} \sum_{n=-N/2}^{N/2-1} X_n \delta(\omega - \frac{n}{T_u})$$

(2.2)

The OFDM symbol duration  $(T_u)$  being an integer m n multiple of each subcarrier duration,  $T_c \cdot n = T_u$ , is the key to orthogonality between the subcarriers. This orthogonality may be

proven by calculating the cross correlation between two subcarriers, which possess the properties of spacing and time duration mentioned above. The values of the data symbols  $X_n$  may be left out of this calculation since they are constant over the entire symbol interval.

$$\int_{0}^{T_{u}} (e^{j\frac{2\pi n_{1}t}{T_{u}}})^{*} \cdot (e^{j\frac{2\pi n_{2}t}{T_{u}}}) dt$$

(2.3)

$$= \int_{0}^{T_{u}} e^{j \frac{(2\pi n_{2} - n_{1})t}{T_{u}}} dt$$

(2.4)

$$= \delta(n_2 - n_1) \tag{2.5}$$

Equation (2.5) show that two subcarriers only correlate if  $n_1$  and  $n_2$  are equal, i.e. are located at the same frequency.

#### 2.1.2 An OFDM Downlink System

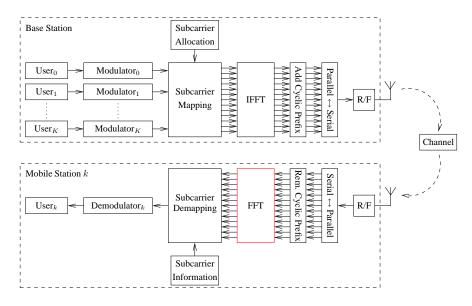

Figure 2.1 shows the structure of an OFDM downlink system.

**Figure 2.1:** System model of general OFDM downlink. The red marked FFT block of the mobile station is to be implemented and evaluated.

#### **Base Station**

At the Base Station, data symbols are distributed across the subcarriers assigned to each user. The mapped data symbols are next mixed onto the assigned subcarriers by use of an inverse Fourier transform. This produces a signal of the same length as the FFT, which has the form of equation (2.1).

In the next part of the system, the output of the IFFT block is extended by a cyclic prefix:

$$s'(t) = \begin{cases} s(t + T_u - T_g) & 0 \le t < T_g \\ s(t - T_g) & T_g < t < T_s \\ 0 & \text{Otherwise} \end{cases}$$

(2.6)

$T_g$  is the length of the cyclic prefix, which must have the following property:

$$\delta \delta_t + \tau_{max} < T_g \tag{2.7}$$

where  $\delta_t$  is the maximum time synchronization offset between BS and MS and  $\tau_{max}$  is the maximum delay spread of the wireless channel. By adding this cyclic prefix it is ensured that the MS always is able to receive a sample of length  $T_u$ , which does not feature Intersymbol Interference (ISI) caused by the reception of multiple reflections of s' at the MS.

Finally, the signals for each  $T_s$  interval are concatenated and modulated onto a carrier sinusoid with frequency  $f_c$  to form the BS output signal, o(t):

$$o(t) = \sum_{s=0}^{S-1} s'(t - sT_s) \cdot e^{2\pi f_c t}$$

(2.8)

where S is the number of  $T_s$  symbol intervals to be transmitted.

#### Wireless Channel

Passing the signal, o(t), through a wireless channel is analogue to passing the signal through a FIR filter, which models the fading and reflecting of the signal which is experienced from BS to MS. Such a filter  $h_{u,s}(t)$  for a specific user u and OFDM symbol period s may be written as:

$$h_{u,s}(t) = \sum_{l=0}^{L-1} h_{u,l}[s]\delta(t-\tau_l), \quad \text{where} \quad sT_s < t < (s+1)T_s$$

(2.9)

where l is one of the L multipaths received at the MS.  $h_{u,l}[s]$  is the complex gain of the l'th multipath of the u'th user for OFDM symbol interval s.

In addition to the filtering characteristics of the multipath fading channel, the received signal at the MS will feature a noise contribution, v(t). At the *u*'th mobile station, the received signal, r(t) is thus:

$$r(t) = \Re\left\{ (s'(t) * h_{u,s}(t))e^{j2\pi f_c t} \right\} + v(t), \quad \text{where} \quad sT_s < t < (s+1)T_s \tag{2.10}$$

#### **Mobile Station**

The first task at the receiver is to down convert r(t) from the carrier frequency band to baseband. Since perfect synchronization of time and system clock frequency cannot be assumed, the received baseband signal becomes:

$$r'(t) = (s'(t - \delta_t) * h_{u,s}(t))e^{j\delta_{\omega}t} + v'(t), \quad \text{where} \quad sT_s < t < (s+1)T_s$$

(2.11)

where  $\delta_t$  is the time synchronization mismatch between BS and MS and  $\delta_{\omega}$  is the system frequency mismatch.

Next the cyclic prefix is removed from each  $T_s$  long signal block, to get a received version of s(t) for the s'th symbol, denoted  $y_s(t)$ :

$$y_s(t) = r'(t' + T_g - sT_s), \text{ where } 0 < t < T_s - T_g$$

(2.12)

$$= (s'(t - \delta_t + T_g - sT_s) * h_{u,s}(t))e^{j\delta_\omega t} + v'_s(t)$$

(2.13)

Here it becomes clear that if the cyclic prefix duration,  $T_g$ , satisfies the requirement of Equation (2.7), removing the cyclic prefix will effectively remove any intersymbol interference introduced from both time synchronization mismatch between BS and MS, and channel delay spread, since these effects will be constrained to the first  $T_q$  part of each  $T_s$  interval.

Next, to extract the data intended for  $MS_k$ ,  $y_s(t)$  is correlated with each of the  $M_k$  the subcarrier frequencies assigned to user k:

$$Y_s[m] = \frac{1}{\sqrt{T_u}} \int_0^{T_u} y_s(t) e^{-j(\omega_m + \delta_\omega)t} dt, \quad \text{where} \quad \le m \le M_k - 1 \tag{2.14}$$

Equation (2.14) is recognized as the Fourier transform of  $y_s(t)$  evaluated in a single subcarrier frequency,  $\omega_m + \delta_{\omega}$ . To uncover the components of  $Y_s[m]$  we start be evaluating the Fourier transform of  $y_s(t)$ , which may be written as:

$$Y_s(\omega) = \mathbb{F}[y_s(t)\xi(t)]$$

(2.15)

$$= \mathbb{F}\left[\left(\left(s'_{s}(t-\delta_{t}+T_{g}-sT_{s})*h_{u,s}(t)\right)e^{j\delta_{\omega}t}+v'_{s}(t)\right)\xi(t)\right]$$

(2.16)

$$\approx \mathbb{F}\left[\left((s_s(t-\delta_t)*h_{u,s}(t))e^{j\delta_\omega t}+v'_s(t)\right)\xi(t)\right]$$

(2.17)

$$= e^{-j\omega\delta_t} \mathbb{F}\left[s_s(t) * h_{u,s}(t)\right] * \delta(\omega - \delta_\omega) * \Xi(\omega) + \mathbb{F}\left[v'_s(t)\right] * \Xi(\omega)$$

(2.18)

where the term  $e^{j\omega\delta_t}$  is the constant phase shift introduced by the time synchronization mismatch,  $\xi(t)$  is a rectangular window of length  $T_u$  with corresponding Fourier transform  $\Xi(\omega)$ :

$$\Xi(\omega) = T_u \cdot e^{j\pi\omega T_u} \cdot \operatorname{sinc}(\omega T_u)$$

(2.19)

Equation (2.18) may be rewritten to:

$$Y_{s}(\omega) = e^{-j\omega(\delta_{t}+\pi T_{u})} \cdot \left[ \dots \right]$$

$$\dots \qquad \sum_{k=-N/2}^{N/2-1} X_{s}[k]H_{u,s}\left[\frac{k}{T_{u}}\right] \operatorname{sinc}\left(T_{u}(\omega-\frac{k}{T_{u}}-\delta_{\omega})\right) + N_{s}(\omega) \right]$$

(2.20)

where  $N_s(\omega) = \mathbb{F}[v'_s(t)] * \Xi(\omega)$ . Since  $Y_s[m] = Y_s(\omega_m)$  and  $\omega_m \in \frac{T_u}{n} | 0 \le n \le N - 1$  we get:

$$Y_{s}[m] = e^{-j\omega_{m}(\delta_{t} + \pi T_{u})} X_{u,s}[m] H_{u,s}[m] + N_{s}[m]; \delta_{\omega} = 0;$$

(2.21)

where  $X_{u,s}[m]$  is the *m*'th symbol for user *u* in OFDM symbol interval *s*, located at  $\omega_m$ ,  $H_{u,s}[m] = H_{u,s}(\omega_m)$  and  $N_s[m] = N_s(\omega_m)$ . Finally, we include the constant phase shift,  $e^{-j\omega_m(\delta_t + \pi T_u)}$ , in the channel gain coefficient,  $H_{u,s}[m]$ , to get  $H'_{u,s}[m]$ :

$$H'_{u,s}[m] = e^{-j\omega_m(\delta_t + \pi T_u)} H_{u,s}[m]$$

(2.22)

since terms will be estimated together, when estimating the equalization factor,  $Z_{u,s}[m]$ , used to produce a estimate of  $X_{u,s}[m]$ :

$$\hat{X}_{u,s}[m] = Z_{u,s}[m]H_{u,s}[m]X_{u,s}[m] + Z_{u,s}[m]N_s[m]$$

(2.23)

This concludes the analytical system model, presenting the process of modulating and transmitting a symbol from the base station to estimation of a symbol at the mobile station.

#### 2.2 Subcarrier Allocation Schemes

The task of allocating subcarriers for multiple users in OFDM systems to maximize spectrum utilization is an entire field of study of it's own. The topic of subcarrier allocation is not discussed in detail here, but the principal structures of subcarrier locations are described in order to outline the possible conditions under which the DFT is utilized.

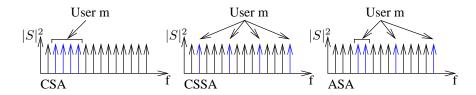

Three basic structures of subcarrier allocations exist (Kim and Kim [2007] and Lawrey [1999]), which are shown in figure 2.2 on the following page and described below:

#### • Clustered Subcarrier Allocation (CSA):

With CSA the subcarriers are allocated as a set on consecutive subcarriers are assigned to each user. This allocation may be static for the entire BS-MS link period or a frequency hopping sequence may be used to increase the mean performance of the link, by avoiding static location of the allocated subcarriers in a spectrum null.

#### • Comb Spread Subcarrier Allocation (CSSA):

Another way of avoiding subcarrier locations in a spectrum null is to allocate the subcarriers in a comb structure, where the subcarriers are spread over the entire spectrum.

#### • Adaptive Subcarrier Allocation (ASA):

Finally, ASA uses spectrum sensing to determine the locations in the spectrum to place the subcarriers to maximize throughput. This way each user will always be assigned the best channel available, thus increasing the overall system performance.

#### 2.3 System Specification

In order to focus on the implementation challenges and performance achievements of the OFDM downlink FFT block, marked with red color in figure 2.1, the following delimitations are introduced in the test system used for validating the proposed implementations:

Figure 2.2: Subcarrier allocation principles. CSA allocates subcarriers for a user as a block of consecutive subcarriers. CSSA spreads the allocated subcarriers evenly across the spectrum. ASA allocates the subcarriers adaptively to maximize channel throughput, thus no structure of subcarrier locations are assumed.

#### • Ideal RF transmission and channel

The RF carrier modulation and demodulation and channel effects applied to a signal transmitted through a wireless channel are not included in the test system, since the FFT block does not process the received signal to neutralize the transmission effects.

#### Ideal synchronization between BS and MS

An extension of ideal transmission between BS and MS is the assumption of ideal synchronization in time and frequency. Time synchronization eliminates the need for the test system to include handling the addition and removal of cyclic prefixes, and frequency synchronization, or system clock matching, preserves the orthogonality between subcarriers.

#### · Data symbols to be transmitted are QPSK modulated

The test system input is randomly generated QPSK symbols with amplitude  $||X_n||^2 =$  1. The system input is only used for validation of the results calculated by the FFT block, thus there need not be an elaborate coding and decoding of payload data.

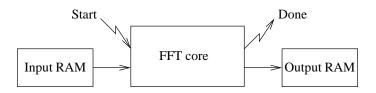

Figure 2.3: Principal blocks of test system. The system consists of a FFT core, RAM for input and output data, a signal starting calculation of the FFT and a signal for indicating when calculation has finished.

The system to be implemented on a FPGA platform is shown in figure 2.3. This test system consists:

- Memory containing a test vector with MatLAB simulations of a mobile station FFT block input frame and a second vector containing subcarrier locations. When the FFT is calculated, the results are placed in the same memory as the input.

- FFT core for demodulating the necessary subcarriers.

- Control signals for indication of input data ready (start) and result (output data) ready (done).

Finally, a set of global system constraints are taken from the WiMax standard [Das, 2007, table 2.3] to define the basic system structure with regards to length of the full FFT length and the OFDM symbol duration. These constraints are then used define the system parameters for completion time and number of subcarriers to be demodulated. These constants are shown in table 2.1.

| Parameter             | System Constraint | WiMAX standard range |

|-----------------------|-------------------|----------------------|

| Frame duration [ms]   | 2                 | min. 2               |

| Full FFT length       | 1024              | 128 - 2048           |

| FFT Time [ms]         | 0.5               | 0.1                  |

| Number of subcarriers | 1 - 250           | -                    |

**Table 2.1:** System constraints for FFT size and timing performance.