### Title:

## Analyzing and Implementing a Reed-Solomon Decoder for Forward Error Correction in ADSL

### **Project Period:**

10<sup>th</sup> February 2007 – 5<sup>th</sup> June 2007

### Group:

ASPI, group 1040

### **Group Members:**

Aleksandras Šaramentovas Paulius Ruzgys

### **Supervisors:**

Rasmus Abildgren Yannick Le Moullec

Number of reports printed: 5 Number of pages in report: 99 Number of pages in appendix: 20 Total number of pages: 133

### Abstract:

This report presents a rapid design strategy for an efficient implementation of a Reed-Solomon (RS) decoder specified in ADSL standard ITU G.992.1 onto the Xilinx Virtex II FPGA and TigerSHARC ADSP-TS201 DSP.

ADSL is a home user-oriented modem technology that uses existing twisted-pair copper telephone lines to transport highbandwidth data, such as multimedia and video.

The project goes through the given system (i.e., RS decoder) analysis, its modeling, simulation, selection of a particular RS decoder over another for its further analysis and implementation onto the available types of architectures.

Before the actual implementation step, it is necessary to determine which type of architecture (DSP or FPGA) is the most suitable for the execution of the selected RS decoder. For that, algorithm characterization is performed. The main idea of characterization is to extract relevant information from the given algorithm to guide the designer towards an efficient algorithm-architecture matching. To this effect, different performance metrics are efficiently used in the project to rapidly stress the proper architecture style for the given RS decoding algorithms.

Aalborg University • Fredrik Bajers Vej 7 • Aalborg 2007

# Preface

This master thesis was written by 1040 group of ASPI specialization at the Faculty of Engineering and Science, Institute of Electronic Systems, Department of Communication, Aalborg University, Denmark.

The project was proposed by the project supervisors. The project report guides the reader through a rapid design strategy for an efficient implementation of a Reed-Solomon decoder specified in ADSL standard ITU G.992.1 onto the available architectures.

The enclosed CD contains all source codes, which were used in this project work.

5th of June, 2007

Aleksandras/Šaramentovas

Paulius Ruzgys

# **List of Abbreviations**

| A/D        | Analog-to-Digital                                          |  |  |  |

|------------|------------------------------------------------------------|--|--|--|

| ADSL       | Asymmetric Digital Subscriber Line                         |  |  |  |

| AFI        | Automatic Function Inlining                                |  |  |  |

| ALU        | Arithmetic Logic Unit                                      |  |  |  |

| ALC        | American National Standards Institute                      |  |  |  |

| ASIC       | Application-Specific Integrated Circuit                    |  |  |  |

| AWGN       | Additive White Gaussian Noise                              |  |  |  |

| BER        | Bit Error Rate                                             |  |  |  |

| BM         | Berlekamp-Massey                                           |  |  |  |

| BMR        | Bit Manipulation Rate                                      |  |  |  |

| BPSK       | Binary Phase-Shift Keying                                  |  |  |  |

| BTB        | Branch Target Buffer                                       |  |  |  |

| CD         | Compact Disk                                               |  |  |  |

| CDFG       | Control and Data Flow Graph                                |  |  |  |

| CDFG       | Code Division Multiple Access                              |  |  |  |

|            | -                                                          |  |  |  |

| CLB<br>CLU | Configurable Logic Block         Communications Logic Unit |  |  |  |

| CO         | Communications Logic Unit<br>Central Office                |  |  |  |

| CPLD       |                                                            |  |  |  |

|            | Complex Programmable Logic Device                          |  |  |  |

| CRC        | Cyclic Redundancy Check                                    |  |  |  |

| D/A        | Digital-to-Analog                                          |  |  |  |

| DC         | Direct Current                                             |  |  |  |

| DCM        | Digital Clock Manager                                      |  |  |  |

| DFG        | Data Flow Graph                                            |  |  |  |

| DMA        | Direct Memory Access                                       |  |  |  |

| DMT        | Discrete Multi-Tone                                        |  |  |  |

| DR         | Data Ratio                                                 |  |  |  |

| DRAM       | Dynamic Random Access Memory                               |  |  |  |

| DSL        | Digital Subscriber Line                                    |  |  |  |

| DSP        | Digital Signal Processor                                   |  |  |  |

| DVB        | Digital Video Broadcasting                                 |  |  |  |

| DVD        | Digital Versatile Disc                                     |  |  |  |

| EDAC       | Error Detection and Correction                             |  |  |  |

| EDIF       | Electronic Data Interchange Format                         |  |  |  |

| EEPROM     | Electrically Erasable Programmable Read-Only Memory        |  |  |  |

| EPROM      | Erasable Programmable Read-Only Memory                     |  |  |  |

| FDM        | Frequency-Division Multiplexing                            |  |  |  |

| FEC        | Forward Error Correction                                   |  |  |  |

| FIFO       | First In, First Out                                        |  |  |  |

| FPGA       | Field-Programmable Gate Array                              |  |  |  |

| GCD        | Greatest Common Divisor                                    |  |  |  |

| GF         | Galois Fields                                              |  |  |  |

| GPP        | General Purpose Processor                                  |  |  |  |

| GRM        | General Routing Matrix                                     |  |  |  |

| HCDFG      | Hierarchical Control and Data Flow Graph                   |  |  |  |

| HDL        | Hardware Description Language                                                   |  |  |  |

|------------|---------------------------------------------------------------------------------|--|--|--|

| I/O        | Inputs/Outputs                                                                  |  |  |  |

| IAB        | Instruction Alignment Buffer                                                    |  |  |  |

| IAU        | Integer Arithmetic Logic Unit                                                   |  |  |  |

| IDDE       | Integrated Development and Debugging Environment                                |  |  |  |

| IFFT       | Inverse Fast Fourier Transform                                                  |  |  |  |

| IOB        |                                                                                 |  |  |  |

| IPO        | Input/Output Block                                                              |  |  |  |

| ISDN       | Interprocedural Optimizations                                                   |  |  |  |

|            | Integrated Services Digital Network                                             |  |  |  |

| ISE<br>ITU | Integrated Software Environment           International Telecommunication Union |  |  |  |

|            |                                                                                 |  |  |  |

| LC         | Logic Cell                                                                      |  |  |  |

| LFSR       | Linear Feedback Shift Register                                                  |  |  |  |

| LUT        | Look-Up Table                                                                   |  |  |  |

| LVDS       | Low-Voltage Differential Signaling                                              |  |  |  |

| MAC        | Multiply and Accumulate                                                         |  |  |  |

| MSB        | The Most Significant Bit                                                        |  |  |  |

| NSP        | Network Service Provider                                                        |  |  |  |

| ОТР        | One-Time Programmable                                                           |  |  |  |

| PC         | Program Counter                                                                 |  |  |  |

| PGO        | Profile-Guided Optimizations                                                    |  |  |  |

| PI         | Programmable Interconnection                                                    |  |  |  |

| PLD        | Programmable Logic Devices                                                      |  |  |  |

| РО         | Procedural Optimizations                                                        |  |  |  |

| POTS       | Plain Old Telephone System                                                      |  |  |  |

| QAM        | Quadrature Amplitude Modulation                                                 |  |  |  |

| RAM        | Random Access Memory                                                            |  |  |  |

| RS         | Reed-Solomon                                                                    |  |  |  |

| SCD        | Strong Circularity Degree                                                       |  |  |  |

| SHARC      | Super Harvard Architecture Single-Chip Computer                                 |  |  |  |

| SHD        | Strong Harvard Degree                                                           |  |  |  |

| SMD        | Strong MAC Degree                                                               |  |  |  |

| SNR        | Signal-to-Noise Ratio                                                           |  |  |  |

| SOC        | System-On-a-Chip                                                                |  |  |  |

| SPD        | Strong Parallelism Degree                                                       |  |  |  |

| SRAM       | Static Random Access Memory                                                     |  |  |  |

| ТС         | Transmission Convergence                                                        |  |  |  |

| ТСМ        | Trellis Coded Modulation                                                        |  |  |  |

| VDSL       | Very High Speed Digital Subscriber Line                                         |  |  |  |

| VHDL       | Very-High-Speed Integrated Circuit Hardware Description Language                |  |  |  |

| WCD        | Weak Circularity Degree                                                         |  |  |  |

| WHD        | Weak Harvard Degree                                                             |  |  |  |

| WMD        | Weak MAC Degree                                                                 |  |  |  |

| WPD        | Weak Parallelism Degree                                                         |  |  |  |

# Contents

| 1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 1.1. Project Objective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11                                                                                                             |

| 1.2. A <sup>3</sup> Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12                                                                                                             |

| 1.3. Design Trajectory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 13                                                                                                             |

| 1.4. Project Limitations and System Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14                                                                                                             |

| 1.5. System Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                |

| 1.6. Organization of the Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15                                                                                                             |

| 2. ADSL System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17                                                                                                             |

| 2.1. Forward Error Correction in Transceivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                                                                                                             |

| 2.1.1. Error-Control Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 19                                                                                                             |

| 2.2. Overview of ADSL System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20                                                                                                             |

| 2.2.1. Spectrum Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20                                                                                                             |

| 2.2.2. ADSL Modem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22                                                                                                             |

| 2.2.3. Data Protection and Correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22                                                                                                             |

| 2.2.3.1. Cyclic Redundancy Check (CRC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23                                                                                                             |

| 2.2.3.2. Forward Error Correction (FEC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23                                                                                                             |

| 2.2.3.3. Interleaving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23                                                                                                             |

| 2.2.3.4. Fast and Interleaved Paths                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23                                                                                                             |

| 2.2.4. Modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 24                                                                                                             |

| 2.2.4.1. Trellis Coded Modulation (TCM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25                                                                                                             |

| 2.2.4.2. Bit-loading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25                                                                                                             |

| 2.3. Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 26                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                |

| 3. Reed-Solomon Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27                                                                                                             |

| <b>3. Reed-Solomon Codes</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27                                                                                                             |

| 3.1. Introduction to Reed-Solomon Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27<br>27                                                                                                       |

| <ul> <li>3.1. Introduction to Reed-Solomon Codes</li> <li>3.2. Properties of Reed-Solomon Codes</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27<br>27<br>28<br>29                                                                                           |

| <ul> <li>3.1. Introduction to Reed-Solomon Codes</li> <li>3.2. Properties of Reed-Solomon Codes</li> <li>3.2.1. Reed-Solomon Codes Perform Well Against Burst Noise</li> <li>3.3. Galois Fields</li> <li>3.3.1. Properties of Finite Field</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27<br>27<br>28<br>29<br>29                                                                                     |

| <ul> <li>3.1. Introduction to Reed-Solomon Codes</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27<br>27<br>28<br>29<br>29<br>30                                                                               |

| <ul> <li>3.1. Introduction to Reed-Solomon Codes</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27<br>27<br>28<br>29<br>29<br>30<br>30                                                                         |

| <ul> <li>3.1. Introduction to Reed-Solomon Codes</li> <li>3.2. Properties of Reed-Solomon Codes</li> <li>3.2.1. Reed-Solomon Codes Perform Well Against Burst Noise</li> <li>3.3. Galois Fields</li> <li>3.3.1. Properties of Finite Field</li> <li>3.3.2. Prime Size Finite Field GF(p)</li> <li>3.3.2.1. Binary Field GF(2)</li> <li>3.3.3. Extensions to the Binary Field – GF(2<sup>m</sup>)</li> </ul>                                                                                                                                                                                                                                                                             | 27<br>27<br>28<br>29<br>29<br>30<br>30<br>31                                                                   |

| <ul> <li>3.1. Introduction to Reed-Solomon Codes</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27<br>27<br>28<br>29<br>30<br>30<br>31<br>32                                                                   |

| <ul> <li>3.1. Introduction to Reed-Solomon Codes</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27<br>27<br>28<br>29<br>29<br>30<br>30<br>31<br>32<br>33                                                       |

| <ul> <li>3.1. Introduction to Reed-Solomon Codes</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27<br>27<br>28<br>29<br>29<br>30<br>30<br>31<br>32<br>33<br>34                                                 |

| <ul> <li>3.1. Introduction to Reed-Solomon Codes</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27<br>27<br>28<br>29<br>30<br>30<br>31<br>32<br>33<br>34<br>35                                                 |

| <ul> <li>3.1. Introduction to Reed-Solomon Codes</li> <li>3.2. Properties of Reed-Solomon Codes</li> <li>3.2.1. Reed-Solomon Codes Perform Well Against Burst Noise</li> <li>3.3. Galois Fields</li> <li>3.3.1. Properties of Finite Field</li> <li>3.3.2. Prime Size Finite Field GF(p)</li> <li>3.3.2.1. Binary Field GF(2)</li> <li>3.3.3. Extensions to the Binary Field – GF(2<sup>m</sup>)</li> <li>3.3.4. Representation of Finite Field Elements</li> <li>3.3.5. GF(2<sup>m</sup>) Arithmetic Implementation</li> <li>3.4.1. Systematic Encoding</li> <li>3.4.2. Implementation of Encoding</li> </ul>                                                                          | 27<br>27<br>28<br>29<br>29<br>30<br>30<br>31<br>32<br>33<br>34<br>35<br>36                                     |

| <ul> <li>3.1. Introduction to Reed-Solomon Codes</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27<br>27<br>28<br>29<br>30<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37                                     |

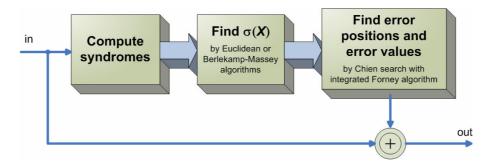

| <ul> <li>3.1. Introduction to Reed-Solomon Codes</li> <li>3.2. Properties of Reed-Solomon Codes</li> <li>3.2.1. Reed-Solomon Codes Perform Well Against Burst Noise</li> <li>3.3. Galois Fields</li> <li>3.3.1. Properties of Finite Field</li> <li>3.3.2. Prime Size Finite Field GF(p)</li> <li>3.3.2.1. Binary Field GF(2)</li> <li>3.3.3. Extensions to the Binary Field – GF(2<sup>m</sup>)</li> <li>3.3.4. Representation of Finite Field Elements</li> <li>3.3.5. GF(2<sup>m</sup>) Arithmetic Implementation</li> <li>3.4.1. Systematic Encoding</li> <li>3.4.2. Implementation of Encoding</li> <li>3.5. Reed-Solomon Decoding</li> <li>3.5.1. Syndrome Calculation</li> </ul> | 27<br>27<br>28<br>29<br>30<br>30<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38                         |

| <ul> <li>3.1. Introduction to Reed-Solomon Codes</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27<br>27<br>28<br>29<br>30<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39                         |

| <ul> <li>3.1. Introduction to Reed-Solomon Codes</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27<br>27<br>28<br>29<br>30<br>30<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40             |

| <ul> <li>3.1. Introduction to Reed-Solomon Codes</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27<br>27<br>28<br>29<br>30<br>30<br>30<br>31<br>32<br>33<br>34<br>35<br>35<br>36<br>37<br>38<br>39<br>40<br>41 |

| 3.5.5. Forney Algorithm                                     |    |

|-------------------------------------------------------------|----|

| 3.6. Summary                                                | 44 |

|                                                             |    |

| 4. Performance Evaluation of Reed-Solomon Codes             |    |

| 4.1. Theoretical Performance of Reed-Solomon Codes          |    |

| 4.1.1. Code Rate                                            |    |

| 4.1.2. Reed-Solomon Performance as a Function of Code Size  |    |

| 4.1.2.1. Selection of Reed-Solomon Codeword Size            |    |

| 4.1.3. Reed-Solomon Performance as a Function of Redundancy |    |

| 4.1.4. Mis-decoding                                         |    |

| 4.2. Simulation of Reed-Solomon Codes                       |    |

| 4.2.1. FEC Model                                            |    |

| 4.2.2. FEC Model Simulation                                 |    |

| 4.2.2.1. Simulation Results                                 |    |

| 4.2.3. Selection of Reed-Solomon Redundancy                 |    |

| 4.2.3.1. Advantages and Drawbacks of RS(255, 239) in ADSL   |    |

| 4.3. Summary                                                |    |

| 5. Algorithm Characterization                               |    |

| 5.1. Architectural Features                                 |    |

| 5.1.1. DSP Architectural Features                           |    |

| 5.1.2. FPGA Architectural Features                          |    |

| 5.2. Performance Metrics                                    |    |

| 5.2.1. Data Oriented Metric                                 |    |

| 5.2.2. DSP Oriented Metrics                                 |    |

| 5.2.2.1. Circular Addressing                                |    |

| 5.2.2.2. MAC Operations                                     |    |

| 5.2.2.3. Harvard Architecture                               |    |

| 5.2.3. FPGA Oriented Metrics                                |    |

| 5.2.4. Difference between Strong and Weak Degrees           |    |

| 5.2.5. Selection of Defined Metrics                         |    |

| 5.2.5.1. Selection of FPGA Oriented Metrics                 |    |

| 5.2.5.2. Selection of DSP Oriented Metrics                  |    |

| 5.2.5.3. Threshold for Highly Computational Loops           |    |

| 5.2.6. The Affinity                                         |    |

| 5.3. The Design-Trotter Tool                                |    |

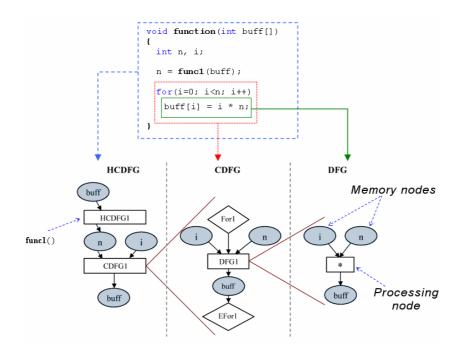

| 5.3.1. C to HCDFG Conversion                                |    |

| 5.3.2. Algorithm Characterization in Design-Trotter         |    |

| 5.3.2.1. $\gamma$ Metric                                    |    |

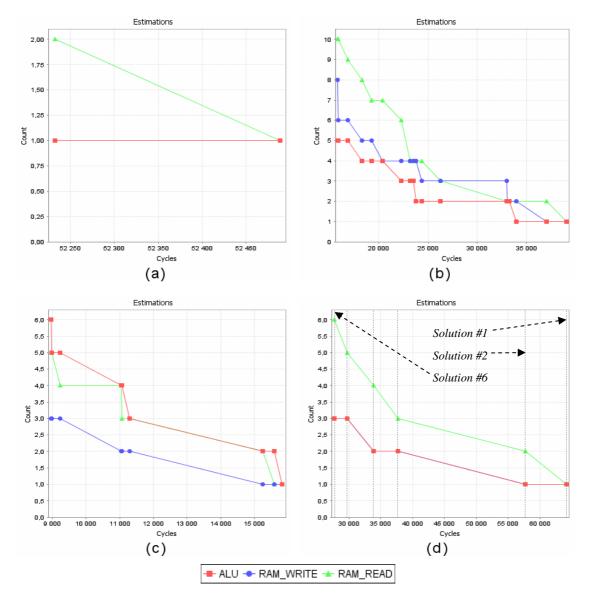

| 5.3.3. Parallelism Exploration                              |    |

| 5.3.4. Scheduling                                           |    |

| 5.3.4.1. Schedule Details                                   |    |

| 5.3.5. Architecture Specification                           |    |

| 5.4. The Affinity Results                                   |    |

| 5.5. Summary                                                |    |

| 6. FPGA Implementation                                                      | 77    |

|-----------------------------------------------------------------------------|-------|

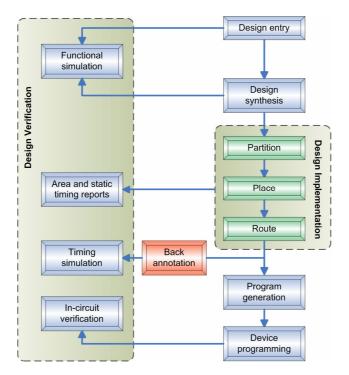

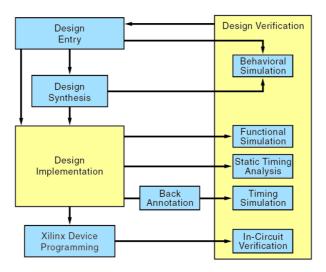

| 6.1. FPGA Design Flow                                                       | 77    |

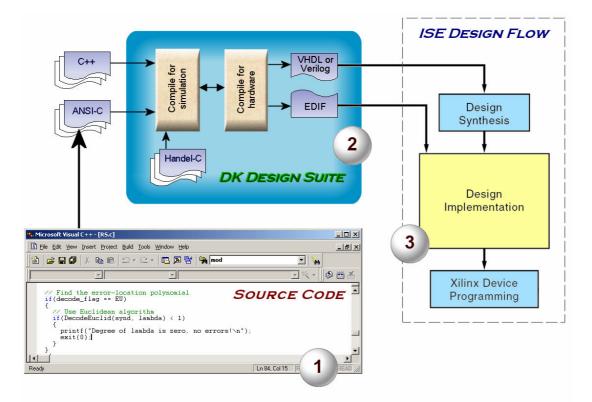

| 6.1.1. The ISE <sup>TM</sup> Design Flow                                    | 78    |

| 6.2. Hardware Description Languages                                         | 79    |

| 6.2.1. Handel-C                                                             | 80    |

| 6.2.1.1. Comparison of Handel-C and ANSI-C                                  | 81    |

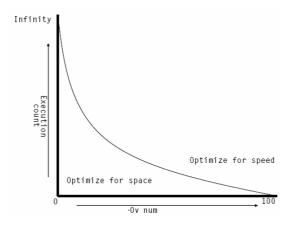

| 6.2.1.2. Handel-C Code Optimization                                         | 83    |

| 6.3. Implementation Results and Analysis                                    | 85    |

| 6.4. Summary                                                                | 87    |

| 7. DSP Implementation                                                       | 80    |

| 7.1. VisualDSP++ Environment                                                |       |

| 7.1.1. Optimizing Performance with VisualDSP++                              |       |

| 7.1.2. Using the Compiler Optimizer                                         |       |

| 7.1.3. Tuning the Code for the Target Compiler                              |       |

| 7.1.3.1. Quad-Word-Aligning                                                 |       |

| 7.1.3.2. Putting Arrays into Different Memory Blocks                        |       |

| 7.2. Implementation Results and Analysis                                    |       |

| 7.3. DSP Implementation Results vs. FPGA Results                            |       |

| 7.4. Summary                                                                |       |

|                                                                             |       |

| 8. Affinity Results Evaluation                                              |       |

| 8.1. Evaluation of Affinity towards FPGA                                    |       |

| 8.2. Evaluation of Affinity towards DSP                                     |       |

| 8.3. General Affinity Evaluation                                            |       |

| 8.4. Cost Function                                                          |       |

| 8.5. Summary                                                                | . 103 |

| 9. Conclusion                                                               | . 105 |

| 9.1. General Summary                                                        |       |

| 9.2. Applying the Proposed Design Trajectory to Other Types of Applications |       |

|                                                                             |       |

| A. Programmable Logic                                                       |       |

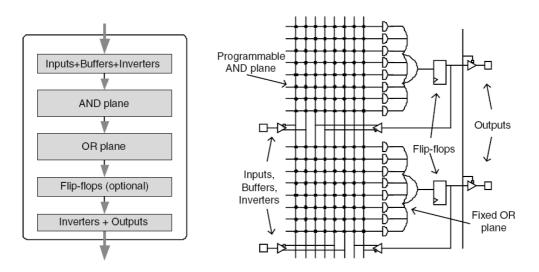

| A.1. Programmable Logic Devices (PLDs)                                      |       |

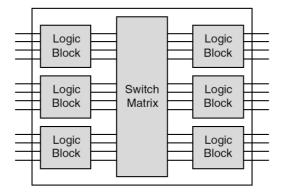

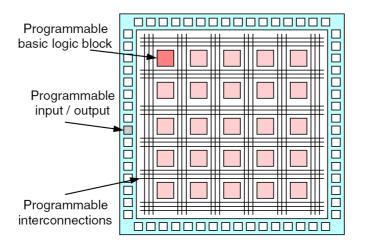

| A.2. Basic FPGA Concepts                                                    |       |

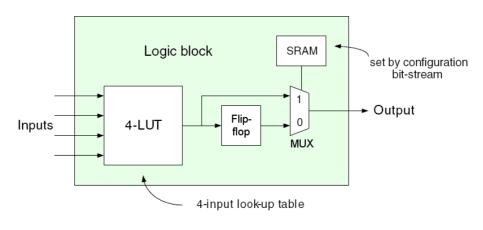

| A.2.1. Programming Methods<br>A.2.2. Look-Up Tables                         |       |

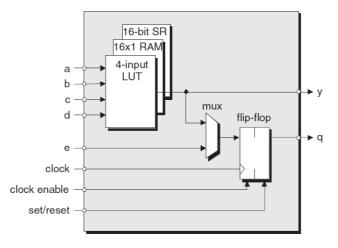

| A.2.2. Look-Op Tables<br>A.2.3. FPGA Logic Block                            |       |

| -                                                                           |       |

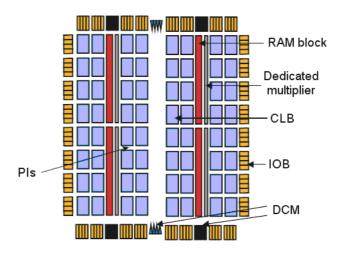

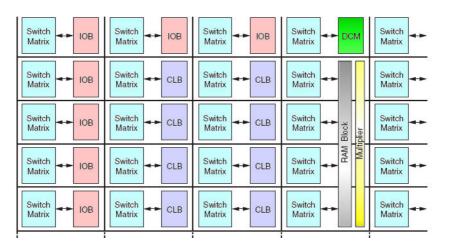

| A.3. Xilinx <sup>TM</sup> Specifics                                         |       |

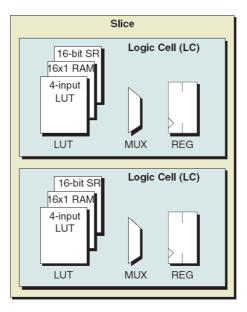

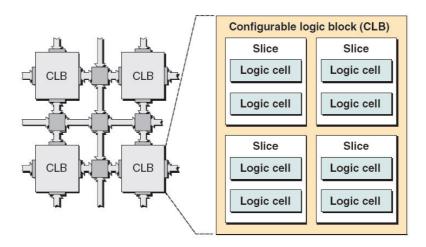

| A.3.1. Configurable Logic Blocks                                            |       |

| A.3.1.1. Distributed RAMs and Shift Registers                               |       |

| A.3.3. Dedicated Multipliers                                                |       |

| A.3.4. Input/Output Blocks                                                  |       |

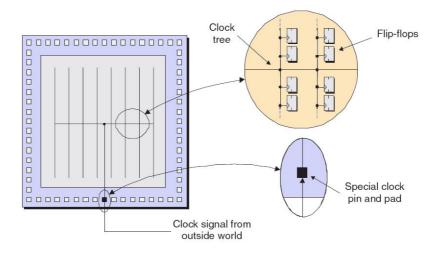

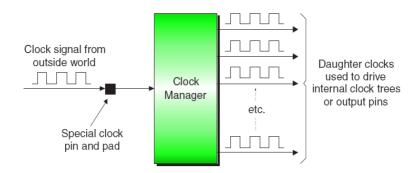

| A.3.5. Digital Clock Manager                                                |       |

| A.3.6. Programmable Routing                                                 |       |

|                                                                             | 1     |

| B. Architecture of TigerSHARC ADSP-TS201 Processor | 123 |

|----------------------------------------------------|-----|

| B.1. Computational Blocks                          | 124 |

| B.1.1. Arithmetic Logic Unit (ALU)                 | 124 |

| B.1.2. Multiplier                                  | 125 |

| B.1.3. Shifter                                     | 126 |

| B.1.4. Communications Logic Unit (CLU)             | 127 |

| B.2. Integer ALU                                   | 127 |

| B.3. Program Sequencer                             | 127 |

| B.3.1. Instruction Line Structure                  |     |

| B.3.2. Instruction Alignment Buffer (IAB)          | 128 |

| B.3.3. Branch Target Buffer (BTB)                  | 129 |

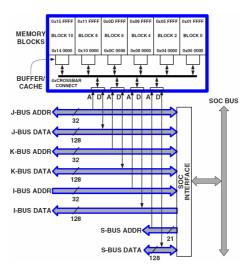

| B.4. Memory and Buses                              | 129 |

| B.4.1. Buses                                       | 130 |

| B.4.2. Memory                                      | 130 |

| Bibliography                                       | 131 |

# INTRODUCTION

Digital communication systems are used for transferring information data between separate remote points, which are connected by appropriate communication channels. The data being sent is usually affected by different channel errors (e.g., noise or interference) that worsen the quality of transmission link. The communication system performance and quality of transmissions can be increased by applying the *Forward Error Correction (FEC)* technique, which is used in almost all digital communication systems to improve performance with regards to Bit Error Rate (BER). Theoretically, FEC allows the maximum level of information in any channel. In practice, it reduces the cost for designing the communication system.

This is also the case for *Asymmetric Digital Subscriber Line (ADSL)*, which uses both *Trellis coding* and *Reed-Solomon* FEC to perform error corrections. In ADSL, the error correction algorithms used (especially decoding) are computationally complex and demanding compared to the other algorithms used (e.g., encoding, modulation, etc). Thus, to meet the given time constraints and to save hardware resources, an efficient implementation is preferred. With increasingly strict time-to-market, a fast process of implementation is also required.

In order to realize fast and efficient implementations, the use of different design strategies/methodologies becomes very important. Without having a strictly defined design strategy, many development projects fail to create effective systems on time and within available budget. However, to develop an expedient design strategy, even both academics and commercial firms that specialized in devising such designs spend tremendous effort for that.

### **1.1. Project Objective**

The main objective of the project is to investigate whether a *fast* design strategy for an *efficient* implementation of a Reed-Solomon (RS) decoder specified in ITU G.992.1 [1] (is the standard for ADSL) on the given target architectures (i.e., DSP and FPGA) can be provided or not. In order to accomplish this, the proposed design trajectory, described in Section 1.3, is evaluated. The design trajectory is based on the  $A^3$  framework. The main idea of this framework is presented in the next section.

# **1.2.** A<sup>3</sup> Framework

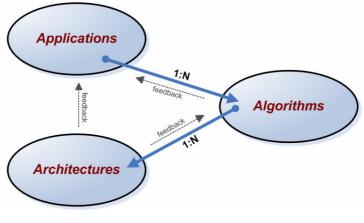

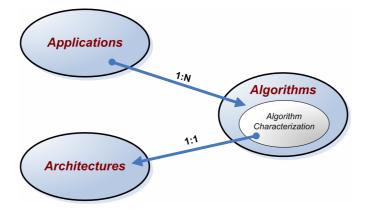

The typical  $A^3$  framework consists of three related domains: *Applications*, *Algorithms* and *Architectures* (Figure 1.2.1). They are described below:

*Figure 1.2.1: Typical A<sup>3</sup> framework.*

### • Applications domain (first step):

This domain is used for:

- 1. Specifying the system;

- 2. System analysis;

- 3. Defining the main tasks that the system must perform.

As we see in Figure 1.2.1, this domain has the relation with the "Algorithms" domain. This relation is "one-to-many" (1:N). It means that there may be a lot of algorithms in the "Algorithms" domain that can be used for a mathematical description of the system functionality. However, from existing algorithms we need to select only one, which best satisfies the given application requirements.

### • Algorithms domain (second step):

This domain is mainly used for algorithms development, simulation and selection. From the simulation results we are able to see, which algorithm is more appropriate for the given application. Although sometimes it is difficult to find an optimal algorithm for the given application, and so the dashed line from the "Algorithms" domain to the "Applications" domain (see Figure 1.2.1) indicates that if such problem occurs, it is necessary to review the application and maybe it is useful to make some changes in the given specification to achieve better results.

As shown in Figure 1.2.1, the "Algorithms" domain has the relation with the "Architectures" domain. This relation is "one-to-many" (1:N). It means that the chosen algorithm can be implemented on different types of architectures (e.g. GPP, DSP, FPGA, etc.), or different architectures of a particular type.

#### • Architectures domain (third step):

In the "Architectures" domain the selected algorithm is implemented on the given architecture(s). As we see in Figure 1.2.1, this domain has the two dashed lines: one line is pointed to the "Algorithms" domain, meaning that not always the best algorithm for the given application will show the best result in a certain architecture, and so, in such case, we need to return one step back to the "Algorithms" domain for another algorithm selection. Other dashed line is pointed to the "Applications" domain, meaning that when we map an algorithm to the target architecture(s), the result of this mapping sometimes may not fulfill the given application requirements. In such case, it is necessary to review and possibly change these requirements.

## **1.3. Design Trajectory**

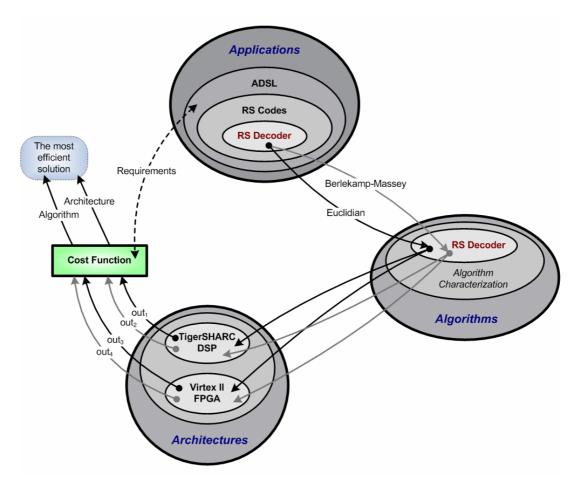

The proposed design trajectory, shown in Figure 1.3.1, slightly differs from the typical  $A^3$  framework, illustrated in Figure 1.2.1. Each particular domain of the proposed design trajectory is described below:

#### • Applications domain:

In this domain the ADSL technology with RS coding (i.e., encoding/decoding) are analyzed as the application of the project.

#### • Algorithms domain:

In this domain, first of all, the appropriate algorithms for RS coding are described in a structured way. In addition, the simulation of described algorithms is run to verify the functionality and evaluate the performance of the corresponding system. According to the limitations of the project (described in Section 1.4), the two different RS decoding algorithms are considered for their further analysis and implementation on the target architectures.

For the reason that the implementation may be performed on different types of architectures (i.e., DSP and FPGA), the following question occurs: which type of architecture is the most suitable for the execution of a certain algorithm? In order to answer this question, *algorithm characterization* is an option. The main idea of characterization is to extract relevant information from the specification of an application (i.e., algorithm) to guide the designer towards an efficient algorithm-architecture matching. For this purpose, different metrics can be efficiently used to rapidly stress the proper architecture style for the given application. In our case, this is referred to as a fast implementation.

#### • Architectures domain:

After the characterization of the given RS decoding algorithms, the implementation is performed. In order to implement the decoding algorithms, the two available devices

are used in the project: *Xilinx Virtex II* reconfigurable FPGA (v3000) and *TigerSHARC ADSP-TS201* DSP. The functionalities of these devices are presented in Appendixes A and B, respectively.

To verify that the obtained characterization results are true, the two decoding algorithms are first *optimized* (considering the capabilities of the target architectures) and then implemented both onto FPGA and DSP, resulting in four outputs: two architectures with two different algorithms in each (see Figure 1.3.1). For the desired verification, the corresponding implementation results are then compared with the characterization results.

Finally, only one particular architecture with one particular algorithm, which best satisfy the defined *cost function* related to the ADSL requirements, is selected from existing implementation outputs.

*Figure 1.3.1:* A<sup>3</sup> *framework of the project.*

### **1.4. Project Limitations and System Constraints**

Because of the limited project period, a number of constraints have been made:

- It is decided to focus on the two commonly used RS decoding algorithms: *Berlekamp-Massey* and *Euclidean* algorithms (described in Chapter 3);

- The *erasure technique* (described in Chapter 3) in RS decoding is not considered;

- The programs for simulation and implementation of RS codes are built upon existing ones<sup>1</sup>, written in C/C++ language;

- RS codes have a number of parameters, which can be modified. For the easier code optimization and implementation purposes, these parameters should be kept fixed.

## **1.5. System Requirements**

There are several requirements for the system (i.e., RS decoder) to be developed during the project period:

- The system should follow ITU G.992.1 [1], which defines the system to support a minimum of 6.144 Mbit/s downstream;

- Changing the RS parameters, bit-error performance of RS codes changes as well. Since these parameters are selected to be constant in our case, we need to initially make a decision on the level of bit-error performance, which will correspond to a particular set of RS parameters. In order to feel the power of RS codes, it is decided to extract the highest available bit-error performance from RS codes and apply this performance to the system.

## **1.6. Organization of the Report**

The report is divided into three parts. The first part consists of Chapters 2 and 3, where the ADSL technology with RS coding (i.e., encoding/decoding) are described as the application of the project. The second part is related to the "Algorithms" domain in the proposed design trajectory (Figure 1.3.1), and consists of Chapter 4, where the simulation is performed, and Chapter 5 ("Algorithm Characterization"). The last part of the report is related to the "Architectures" domain in the proposed design trajectory, and presented in Chapter 6 ("FPGA Implementation"), Chapter 7 ("DSP Implementation"), and Chapter 8, which carries out the verification of the algorithm characterization results.

<sup>&</sup>lt;sup>1</sup> http://www.eccpage.com/

# **ADSL SYSTEM**

In recent years, Digital Subscriber Line (DSL) technology has been gaining popularity as a high speed network access technology, capable of the delivery of multimedia services over the existing telephone infrastructure. A major impairment for DSL is *impulse noise* in the telephone line. Lightning and switching equipment transients are common causes of impulse noise. However, current DSL services make use of forward error correction (FEC) techniques for improved resistance to noise interference in the data transmission.

The current chapter explains the FEC mechanism and presents the background to Asymmetric DSL (ADSL) system, which is a particular version of DSL technology.

### **2.1. Forward Error Correction in Transceivers**

Forward error correction (FEC) in *transceiver* (transmitter/receiver pair) is used to deliver information from a source (transmitter) to a destination (receiver) through a noisy communication channel with a minimum of errors. FEC allows a receiver in the system to perform Error Detection and Correction (EDAC) without requesting a retransmission of the corrupted data. FEC offers a number of benefits:

- FEC enables a system to achieve high data reliability;

- FEC results in greater effective throughput of user data, because valuable bandwidth is not being used to retransmit corrupted data;

- FEC yields performance gains and low error rates for systems in which other options, such as increasing the transmitted power or installing noise-limiting components, are too expensive or impractical;

- System costs can be reduced by eliminating an expensive or sensitive component and compensating for the lost performance by a suitable FEC scheme.

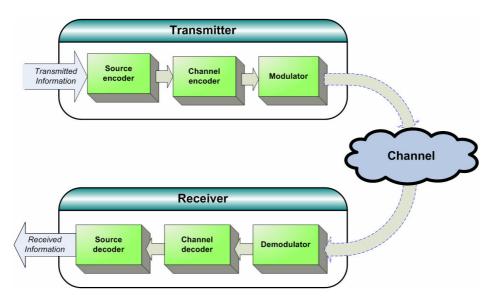

Figure 2.1.1 depicts a typical FEC communication scheme:

### • Source encoder:

In the *source encoder* of the transmitter (Figure 2.1.1), the message to be transmitted is transformed into a sequence of bits that represents the original message. These bits are then fed to the *channel encoder*.

### • Channel encoder:

The channel encoder (or FEC encoder) is designed to perform error correction with the aim of converting an unreliable communication channel into a reliable one. The encoder adds *redundancy* to the data produced by the source encoder in the form of *parity information*. Then at the receiver, a *channel decoder* is able to exploit the redundancy in such a way that a reasonable number of errors introduced by the channel can be corrected. Without redundancy, the code would not allow us to detect the presence of errors and therefore would not have any error controlling properties.

### • Modulator:

The coded data produced by the channel encoder is then mapped into analogue signal (waveforms) in the *digital modulator*, and fed to the channel.

### • Channel:

The channel provides the communication link between the transmitter and receiver, and introduces various forms of corruption to the transmitted signal, like environment noise, attenuation, etc. The errors introduced by the communication channel are classified into two main categories:

Figure 2.1.1: FEC communication system.

- *Random errors*. The probability of error is independent from one transmitting symbol to the next. Random errors occur in the *Additive White Gaussian Noise (AWGN)* channel in which the transmitted signal suffers the addition of wide-band noise whose amplitude is a normally (Gaussian) distributed random variable;

- *Burst errors.* The bit errors occur sequentially in very short time as groups. For example, impulse noise can cause a burst of errors. Impulse noise is a short burst of relatively high energy noise.

Thus, the task of the receiver is to capture the transmitted signal, and remove the effects of the channel.

### • Demodulator:

The *demodulator* converts the waveforms received from the channel into a binary sequence, which is fed to the channel decoder.

### • Channel decoder:

The job of the channel decoder (or FEC decoder) is to decide what the transmitted information was. The channel decoder removes the redundancy introduced by the channel encoder in the transmitter, and attempts to detect and correct possible bit errors using the knowledge of the code used by the channel encoder and the redundancy contained in the received data. The frequency at which bit errors occur at the output of the channel decoder is a measure of the demodulator-decoder performance. Typically the bit error rate (BER) at this point is kept at a desired level so as to have acceptable quality of communication with minimum resource usage.

### • Source decoder:

Finally, the *source decoder* tries to reconstruct the original message from the decoded data. This will be an estimation of the original message due to the possible corruption introduced to the data along its way through the communication link.

### 2.1.1. Error-Control Codes

FEC is also known as channel coding (realized by the FEC encoder/decoder), which is based on a specific error-control code. There are the two main types of error-control codes used in communication systems:

- 1. *Block codes*. Block codes are based strictly on finite field arithmetic. They can be used to either detect or correct errors;

- 2. *Convolutional codes*. These codes are developed with a separate strong mathematical structure and are primarily used for real-time error correction.

The question of whether to choose block codes or convolutional codes depends on the following. When the environment consists predominately of random errors, convolutional codes provide a low bit error rate (BER) solution. However, when the environment consists mainly of burst errors, block codes often perform even better.

Some applications, such as ADSL (described in the following section), use both convolutional and block codes. In such case, concatenated codes result in strong performance by operating in two steps.

### 2.2. Overview of ADSL System

Digital Subscriber Line (DSL) technology is a home user-oriented modem technology that uses existing twisted-pair copper telephone lines to transport high-bandwidth data, such as multimedia and video. The technology is attractive in the aspect that it utilizes the telephone system infrastructures, usually already installed in buildings and facilities. In the Plain Old Telephone System (POTS), only a fraction of the bandwidth of the copper loop (telephone line) is used, thus the DSL service is designed to use the excess bandwidth for downstream and upstream data transmission. DSL service is dedicated, point-to-point, public network access over twisted-pair copper wire on the local loop between a Network Service Provider (NSP's) central office and the customer site.

Some other popular services, such as a standard dial-up modem or an ISDN line, also use the telephone lines to communicate. However, those services prevent the simultaneous operation of standard analog phone service on the same phone line. An important advantage of DSL is that it allows the POTS signal to co-exist with the DSL data signal. The POTS channel is split off from the digital modem by filters commonly called "splitters", thus guaranteeing uninterrupted POTS.

Asymmetric Digital Subscriber Line (ADSL) is the most widely used DSL standard today. The term asymmetric reflects the difference between upstream and downstream bit rates in the transmission link. ADSL allows more bandwidth downstream – from an NSP's Central Office (CO) to the customer site – than upstream from the subscriber to the central office. This asymmetry, combined with always-on access, makes ADSL ideal for Internet surfing, since users typically download much more information than they send.

ANSI standard T1.413 defines an ADSL system to transmit downstream and upstream data rates up to 6.8 Mbit/s and 640 kbit/s, respectively. ITU Recommendation G.992.1 [1] (is the standard for ADSL) defines a system based on T1.413 as a core, but expanded via three annexes to meet particular regional needs. The maximum data rates mentioned in the literature are about 8 Mbit/s downstream and 1 Mbit/s upstream, see [1] or [2].

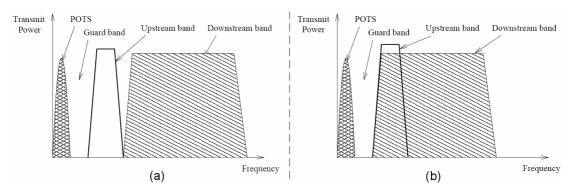

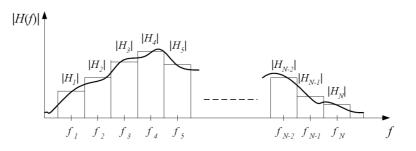

### 2.2.1. Spectrum Allocation

According to [1] (annex A), ADSL is designed to provide data transmission on loops up to 5 km over a 25 kHz - 1.1 MHz frequency band. An ADSL circuit connects an

ADSL modem on each end of a twisted-pair telephone line, creating three information channels – a downstream channel, an upstream channel, and a basic telephone service channel. Each of these channels has its own frequency band. The POTS band goes from near DC to approximately 4 kHz. A frequency guard band is placed between the POTS spectrum and the ADSL spectrum to help avoid interference. The ADSL spectrum (downstream and upstream bands) starts above the POTS band and extends up to approximately 1.1 MHz. There are actually two different ways that the ADSL spectrum can be arranged: to create multiple channels, ADSL modems divide the available bandwidth of a telephone line in one of two ways: *Frequency-Division Multiplexing (FDM)* or *echo-cancellation*, as shown in (Figure 2.2.1): [3]

#### • Frequency-Division Multiplexing (FDM):

In FDM mode, the upstream and downstream frequency bands are separated. Using FDM, the upstream channel allocation ranges from about 26 kHz to 138 kHz, and downstream ranges from 138 kHz to 1.1 MHz (Figure 2.2.1a).

#### • Echo-cancellation:

An alternative to FDM is to use echo-cancellation, which enables upstream and downstream signals to use the same spectrum (Figure 2.2.1b). The objective of echocancellation is to enable the downstream data to use lower frequencies than are available in FDM mode. Using lower frequencies, we can achieve less signal attenuation, which theoretically allows faster downstream data rates on longer loops [2]. Echo-cancellation also adds more available spectrum to the downstream channel.

However, it does require echo-canceling circuitry to remove the reflection of the locally transmitted signal in the overlapped band. This certainly increases the complexity of digital signal processing in the receivers.

Figure 2.2.1: Frequency spectrum usage by ADSL with: (a) FDM, and (b) echo-cancellation.

### 2.2.2. ADSL Modem

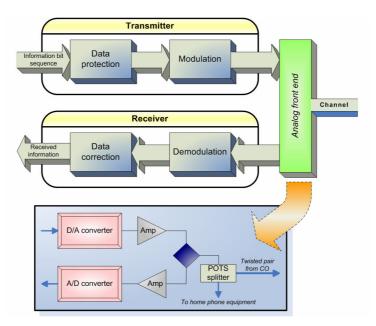

Each ADSL modem consists of transmitter and receiver. A block diagram of a typical ADSL transmitter/receiver pair (transceiver) is shown in Figure 2.2.2.

Figure 2.2.2: Block diagram of a typical ADSL modem.

At the transmitter the information data to be sent is first protected, then modulated and finally transmitted. At the receiver the obtained data is first demodulated and then corrected from errors introduced by the communication channel. Each of these steps is briefly described in the following sections. The analog front end (Figure 2.2.2) is of no interest in our case, and its description is therefore beyond the scope of this report.

### 2.2.3. Data Protection and Correction

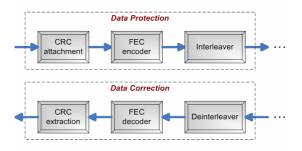

The physical layer of ADSL must ensure that data is transferred reliably across the channel, so the process of data protection is performed: *Cyclic Redundancy Check* (*CRC*) attachment, data coding (FEC technique) and *interleaving* are designed to provide this (Figure 2.2.3).

Figure 2.2.3: Data protection and correction blocks of an ADSL modem, shown in Figure 2.2.2.

### 2.2.3.1. Cyclic Redundancy Check (CRC)

CRC is a method used to detect errors in the received signal. This is done by converting the binary signal to a polynomial and then dividing it with a predefined polynomial called the key. The remainder in this division is called CRC. The signal together with the CRC is transmitted. The receiver performs the same operation as the transmitter, dividing the signal with the same predefined polynomial (key), and then checks the difference between the obtained reminder (CRC) at the receiver and CRC received from the transmitter. If the difference is zero, there is a high probability that the signal has been received correctly, otherwise an error has probably occurred. [4]

### 2.2.3.2. Forward Error Correction (FEC)

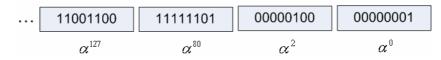

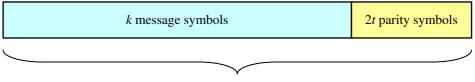

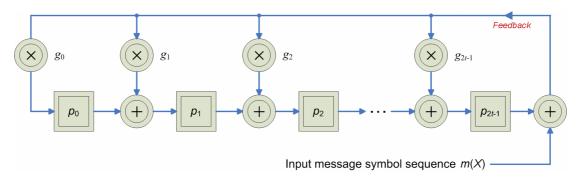

Reed-Solomon (RS) codes (are block codes) have been chosen for the FEC technique in ADSL [1]. The RS encoder takes k data symbols of 8-bits each (byte) and adds parity symbols (redundancy) to make an n symbol data block, called *codeword*. The maximum length (starting from n = 1) of a codeword with 8-bit symbols in ADSL is 255 bytes. There are (n - k) redundant bytes. The ADSL standard requires support of all even numbers from 0 to 16 of redundancy bytes per codeword. This would allow for up to 8 bytes to be in error for every RS codeword.

The essence of RS codes and the principles of RS encoding and decoding are presented in detail in the next chapter.

### 2.2.3.3. Interleaving

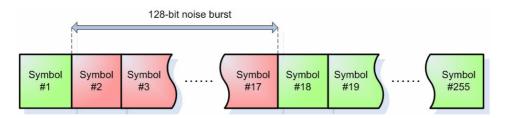

The purpose of the combination of an interleaver in the transmitter and a deinterleaver in the receiver is to spread burst of errors, which occur between several (usually the two), over many codewords, and thus reduce the number of errors in any one codeword to what can be corrected by the Reed-Solomon decoder. The two important parameters for the interleaver are the number of bytes per codeword, n, and the *interleave depth*, D. An interleaver of depth D reads D codewords of length n each and arranges them in a block (array) with D rows and n columns. Then the codewords in the formed array are *convolutionally interleaved* (see [2]) and fed to the channel. In the deinterleaver the bits are rearranged back to its original order. ADSL supports interleave depth which is a power of two from 1 to 64.

The higher interleave depth is, the more data can be interleaved, resulting in much more effective RS FEC performance. But increasing the interleave depth will cause additional latency or delay in the time the data is transmitted and the time it is available to the receiving user.

### 2.2.3.4. Fast and Interleaved Paths

There are actually two separate paths in the data protection and correction blocks of an ADSL modem: "*fast*" and *interleaved*. In the "fast" path the interleaving is not used. The interleaved path provides a lower error rate, but higher latency in comparison with the non-interleaved "fast" path. The increased latency normally causes no problems for general data transmission, but digitized voice over a highlatency path results in extremely unpleasant echo. For this reason, a minimum interleave depth (or no interleaving) is always used on data channels carrying voice traffic. As delay is added to voice transmissions, the problem of echo increases radically and requires additional treatment.

Deciding on a compromise between burst error rate and latency for each data channel is a function of the Transmission Convergence (TC) layer in ADSL [2], which must combine the multiple input data channels and assign them to either the "fast" or the interleaved path.

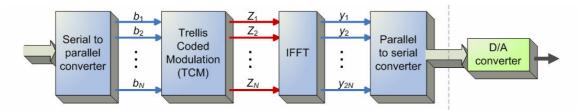

### 2.2.4. Modulation

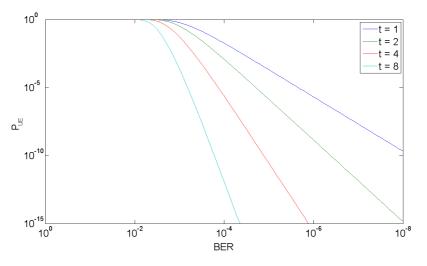

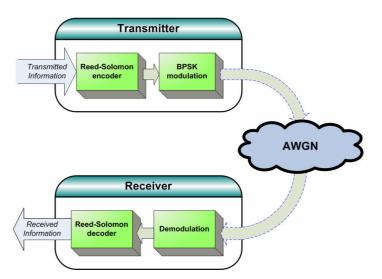

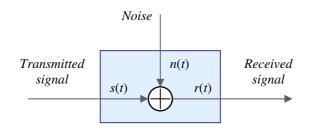

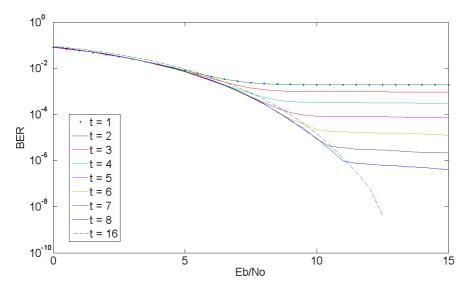

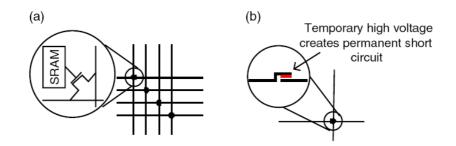

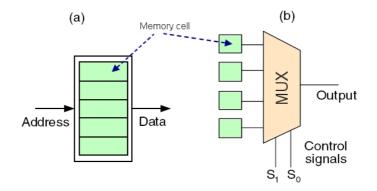

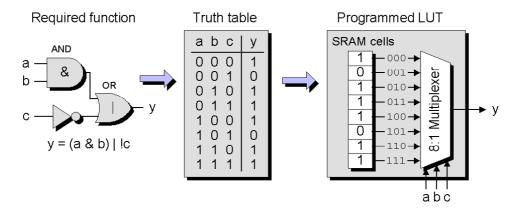

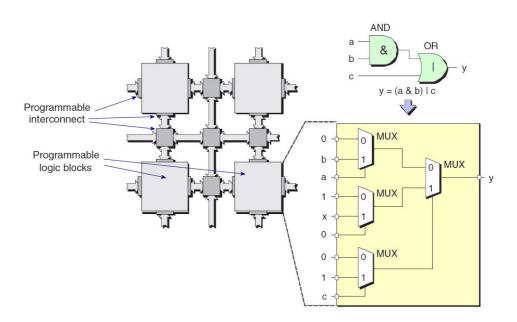

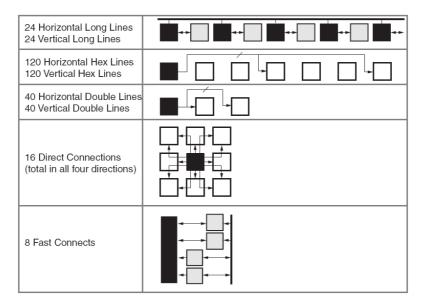

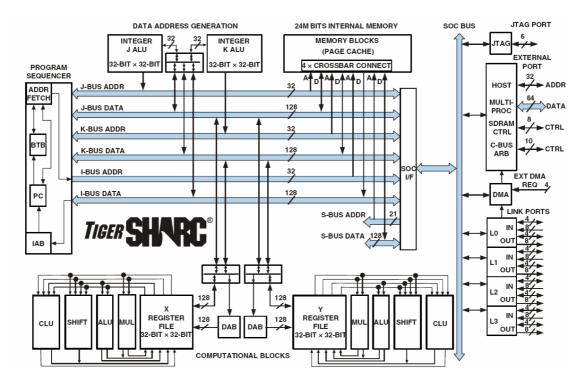

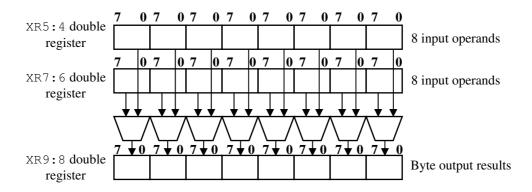

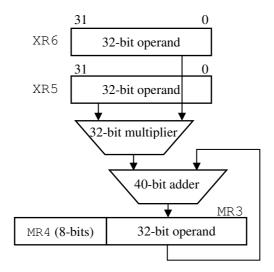

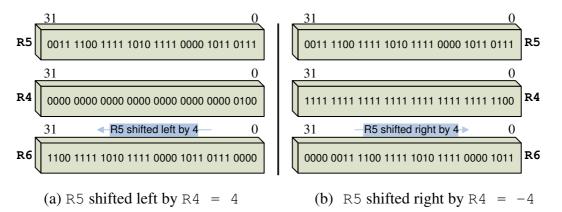

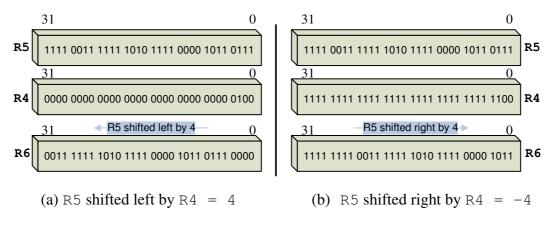

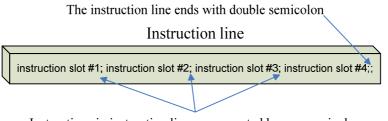

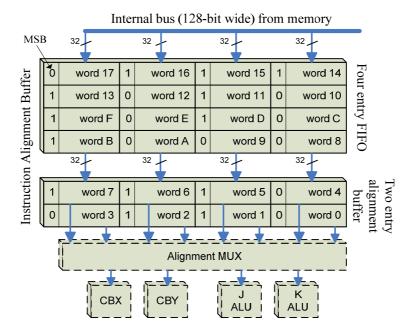

The physical layer of ADSL uses a multicarrier modulation technique, known as *Discrete Multi-Tone (DMT)*, to create the ADSL signal. The basic idea of DMT is to split the available bandwidth into a large number of subchannels, where each subchannel uses *Quadrature Amplitude Modulation (QAM)* [5].