# PEEL

$P_{\text{roperty}} \\$

$E_{\text{xtraction}}$

$E_{\text{ngine}}$

$_{\text{for}}\,L_{\text{SCs}}$

**DAT-6** · **Master's thesis** 1st of June, 2004

Aalborg University

Department of Computer Science

#### Title:

Property Extraction Engine for LSCs

#### Theme:

Modelling and Verification Tools for Embedded Programming

#### **Project period:**

**DAT-6: Master's thesis**

1st of Feb., 2004 - 1st of June, 2004

#### **Authors:**

Jens Gorm Rye-Andersen Mads W. Jensen René Gøttler Michael Jakobsen

#### **Supervisor:**

Anders Peter Ravn

Number of copies: 9

Number of pages: viii + 104

**Appendix:** 6

#### **Synopsis:**

This report presents Live Sequence Charts (LSCs) as a diagrammatic requirements specification language for the formal verification tool UPPAAL, supplementing the already used tree logic language of TCTL.

UPPAAL models are formally described to identify a subset of LSC constructs relevant for UPPAAL model verification. The LSC subset is also formally specified and used in a prototype verification engine PEEL.

Experiments are conducted in order to evaluate LSCs as a requirement specification language for UPPAAL and demonstrate the PEEL prototype.

The experiments show that LSCs are an intuitive way for specifying interobject communication usable for UPPAAL requirements specification. Furthermore, PEEL demonstrates the support of the selected LSC subset.

# **Preface**

This report was written during the spring term of the year 2004. The project was created in collaboration with CISS - Center for Embedded Software Systems, at AAU (Aalborg University). The project report is the authors' Master's thesis in Computer Science.

The report documents an extension of UPPAAL with a diagrammatic approach for requirements specification in the form of Live Sequence Charts, LSCs. A UPPAAL compliant subset of LSC features are identified and formally specified. A prototype verification engine, PEEL, implements support for verifying a UPPAAL model through LSCs.

All first person statements such as "Our opinion..." refer to the authors. All references occur as alphanumeric text in square brackets referring to bibliography entries.

We would like to thank the OFFIS group at the Carl von Ossietzky Universität Oldenburg, especially Bernd Westphal and Bernhard Josko, for providing the LSCEditor with support for use in this project.

We also thank Gerd Behrmann from CISS at Aalborg University for help regarding UPPAAL and for providing the UPPAAL verifyta with support for FSM computation graph output.

If interested in the software implemented and used in this project, please contact Anders Peter Ravn from CISS Aalborg University at <apr@cs.auc.dk>.

| Jens Gorm Rye-Andersen | Mads W. Jensen   |

|------------------------|------------------|

|                        |                  |

| René Gøttler           | Michael Jakobsen |

# **Contents**

| 1 | Intr | oduction                                   | 1  |

|---|------|--------------------------------------------|----|

|   | 1.1  | Diagrammatic requirements specification    | 3  |

|   | 1.2  | Project goals                              | 4  |

|   | 1.3  | Related work                               | 6  |

|   | 1.4  | Overview                                   | 7  |

| 2 | UPP  | PAAL                                       | 9  |

|   | 2.1  | Informal description                       | 9  |

|   | 2.2  | Formal description                         | 13 |

|   | 2.3  | Requirements specification language (TCTL) | 19 |

|   | 2.4  | Example                                    | 21 |

|   | 2.5  | Summary                                    | 23 |

| 3 | Live | e Sequence Charts                          | 25 |

|   | 3.1  | LSC constructs                             | 26 |

|   | 3.2  | Extensions to the basic LSC constructs     | 38 |

|   | 3.3  | LSC behaviour                              | 43 |

|   | 3.4  | Formal description                         | 46 |

|   | 3.5  | Summary                                    | 53 |

| 4 | PEE  | CL - Property Extraction Engine for LSCs   | 55 |

|   | 4.1  | LSCEditor                                  | 56 |

|   | 4.2  | UPPAAL computation graph                   | 61 |

|   | 4.3  | Verification algorithm                     | 63 |

|   | 4.4  | The running time of the algorithms         | 71 |

|   | 4.5  | Optimisation                               | 74 |

|   | 4.6  | Test                                       | 76 |

|   | 4.7  | Summary                                    | 79 |

| 5 | Exp  | eriments                                   | 81 |

|   | 5.1  | Broadcast                                  | 81 |

|   | 5.2  | Train-gate                                 | 84 |

|   | 5.3  | Distributed control                        | 89 |

|   | 5 4  | Summary                                    | 94 |

| 6 | Eval | luation and Conclusion | 95  |

|---|------|------------------------|-----|

|   | 6.1  | Project summary        | 95  |

|   | 6.2  | Evaluation             | 98  |

|   | 6.3  | Future work            | 101 |

|   | 6.4  | Conclusion             | 103 |

| A | UPP  | AAL Expressions        | 105 |

| В | PEE  | L Diagrams             | 108 |

|   | Bibl | iography               | 111 |

# List of Figures

| 1.1  | Sequence diagram from Rhapsody modelling a scenario from a set- | 2  |

|------|-----------------------------------------------------------------|----|

| 1.0  | top box.                                                        | 2  |

| 1.2  | An existential LSC.                                             | 4  |

| 1.3  | Overview of PEEL                                                | 6  |

| 2.1  | The sender and receiver templates of a Broadcast example        | 10 |

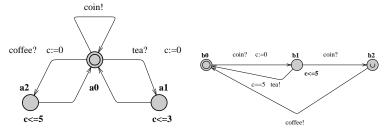

| 2.2  | UPPAAL model of a coffee vending machine                        | 21 |

| 2.3  | FSM computation graph for the vending machine example           | 22 |

| 3.1  | LSC with prechart and main chart                                | 27 |

| 3.2  | The overlap of prechart and main chart                          | 28 |

| 3.3  | An LSC with hot and cold instance lines                         | 31 |

| 3.4  | Synchronous and asynchronous messages in an LSC                 | 32 |

| 3.5  | Two messages exchanged at the same time                         | 33 |

| 3.6  | The types of conditions in LSCs                                 | 34 |

| 3.7  | An LSC with a coregion                                          | 36 |

| 3.8  | How coregions are interpreted                                   | 37 |

| 3.9  | LSC modelling an if-then-else construct                         | 39 |

| 3.10 | LSC two simultaneous regions                                    | 40 |

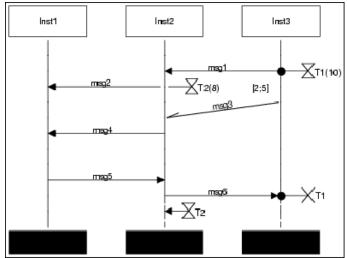

| 3.11 | LSC illustrating Klose's timer constructs                       | 42 |

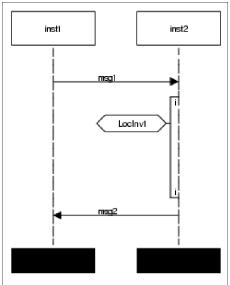

| 3.12 | LSC with a local invariant                                      | 43 |

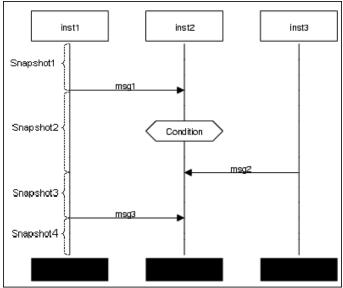

| 3.13 | An LSC divided into snapshots                                   | 44 |

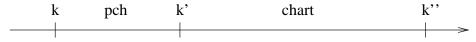

| 3.14 | The order of the charts to be satisfied by a trace              | 48 |

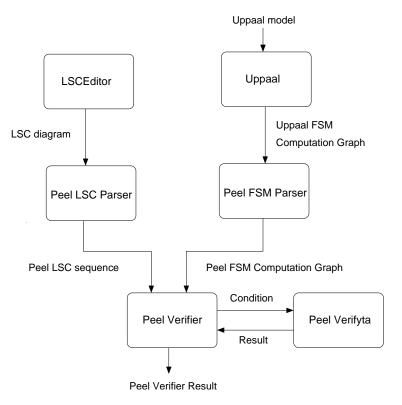

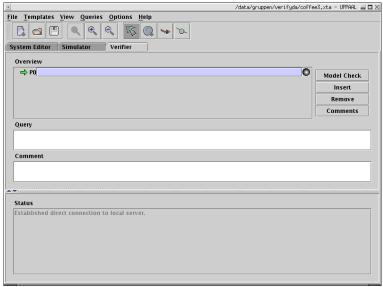

| 4.1  | Data-flow diagram for PEEL                                      | 56 |

| 4.2  | Screenshot displaying the LSCEditor                             | 57 |

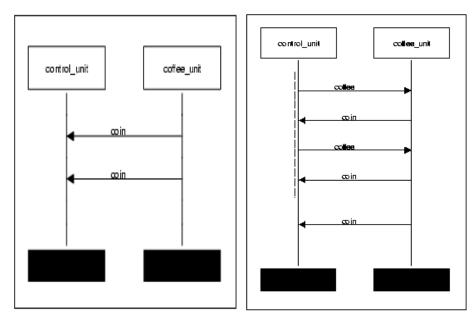

| 4.3  | LSC for the coffee vending machine example                      | 59 |

| 4.4  | Map file for the vending machine example                        | 59 |

| 4.5  | LSC file for the vending machine example                        | 60 |

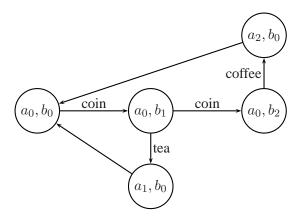

| 4.6  | FSM graph for the vending machine example                       | 62 |

| 4.7  | FSM computation graph for the vending machine example           | 62 |

| 4.8  | FSM computation graph traversion                                | 64 |

| 4.9  | PEEL sequence output                                            | 77 |

| 4.10 | PEEL LSC structure output                                       | 78 |

| 4.11 | PEEL help output                                                | 79 |

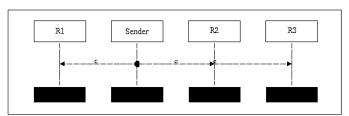

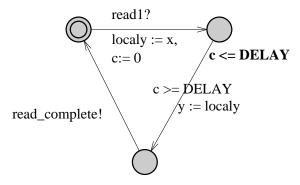

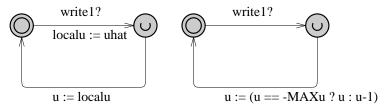

| 5.1  | The sender and receiver templates                                    | 82  |

|------|----------------------------------------------------------------------|-----|

| 5.2  | LSC for the broadcast experiment                                     | 82  |

| 5.3  | LSC prechart and body for the broadcast experiment                   | 83  |

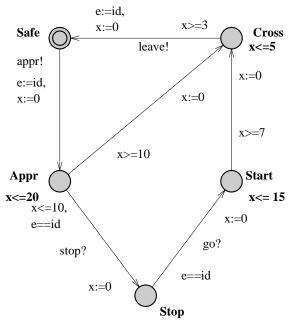

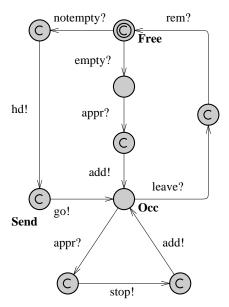

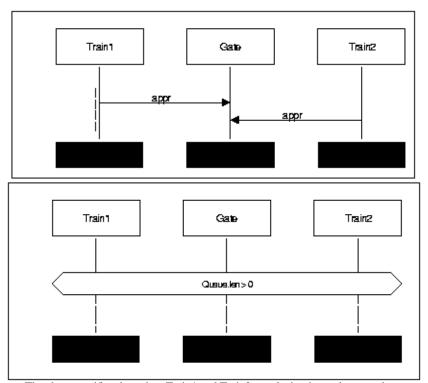

| 5.4  | The train template                                                   | 84  |

| 5.5  | The gate template                                                    | 85  |

| 5.6  | The queue template                                                   | 86  |

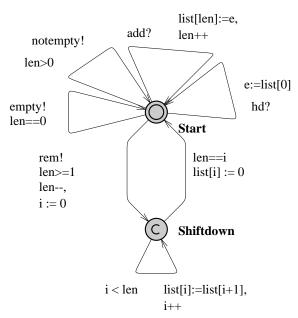

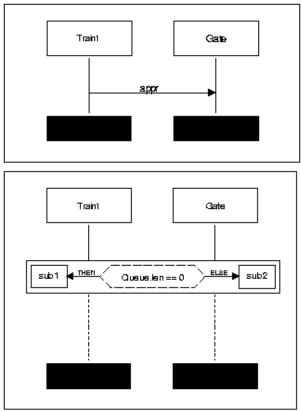

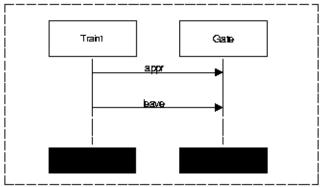

| 5.7  | LSC prechart and body for Train-gate                                 | 87  |

| 5.8  | The subcharts for the Train-gate LSC                                 | 87  |

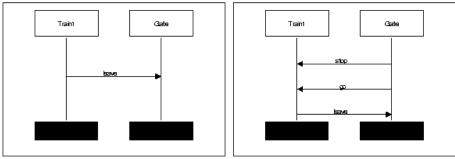

| 5.9  | An existential LSC for the Train-gate experiment                     | 88  |

| 5.10 | LSC prechart and body for the queue in Train-gate                    | 88  |

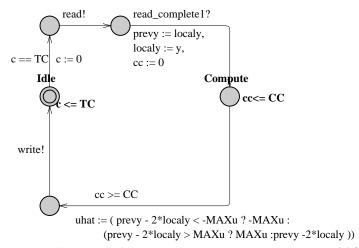

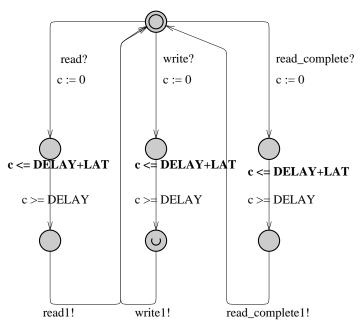

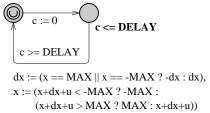

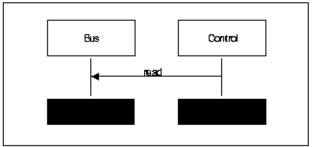

| 5.11 | The template of the controller                                       | 89  |

| 5.12 | The bus template                                                     | 90  |

| 5.13 | The template of the sensor                                           | 91  |

|      | The templates of the actuators                                       | 91  |

|      | The template of the plant                                            | 92  |

| 5.16 | LSC prechart for the read-write scenario                             | 93  |

| 5.17 | LSC chart specifying the read-write cycle of the Distributed control |     |

|      | experiment                                                           | 93  |

| 6.1  | Screenshot of UPPAAL                                                 | 102 |

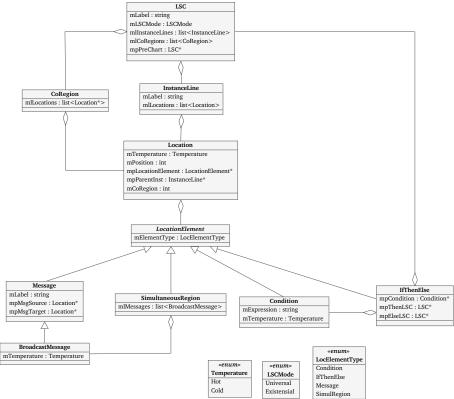

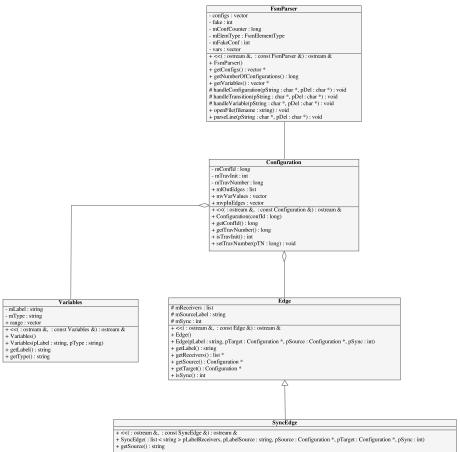

| B.1  | Class diagram of the PEEL LSC Parser output                          | 108 |

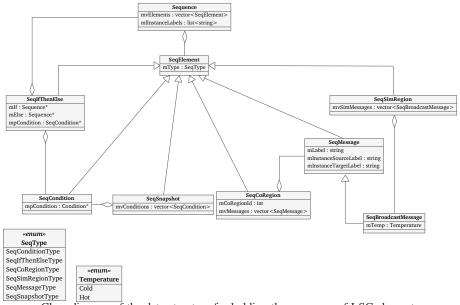

| B.2  | Class diagram for the sequence of LSC elements                       | 109 |

| B.3  | Class diagram of the PEEL FSM Parser output                          | 110 |

# 1 Introduction

#### **Contents**

| 1.1 | Diagrammatic requirements specification | 3 |

|-----|-----------------------------------------|---|

| 1.2 | Project goals                           | 4 |

| 1.3 | Related work                            | 6 |

| 1.4 | Overview                                | 7 |

The goal of software development is to develop software. But how can we know that the software behaves correct? This can be established by validating and verifying the software.

The first part of this Master's thesis was in collaboration with FUTARQUE, which is a company that develops software and hardware for set-top boxes. The goal was to integrate the CASE (computer-aided software engineering) tool Rhapsody into the existing software development department at FUTARQUE. Rhapsody allows for a model-driven development process, which means that the models themselves (UML models) provide means for analysing problem domains and designing the software. Rhapsody provides means for compiling, testing, validating, executing, and debugging the designed models [RAJGJ03].

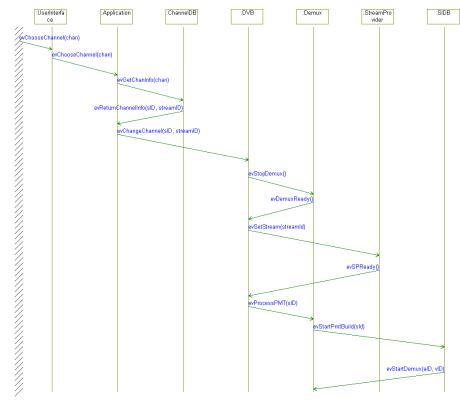

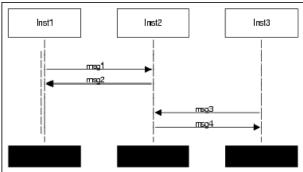

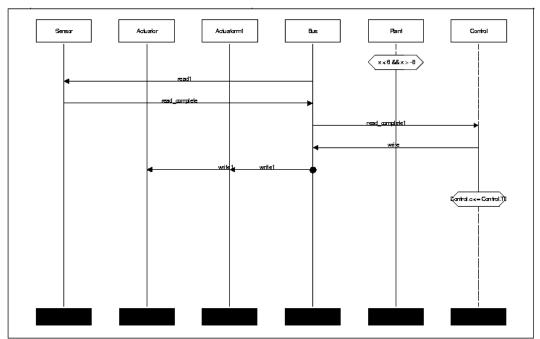

An advantage of Rhapsody is the use of UML diagrams, e.g., sequence diagrams (SDs), which is a version of message sequence charts (MSCs). The SD in Figure 1.1 shows a scenario from a set-top box modelled in Rhapsody. The vertical lines are instances of the system, and the messages between the instance lines describe a message trace through the system. SDs can be used for both analysis and testing in Rhapsody.

Rhapsody's *TestConductor*, which uses SDs as its specification method, was found to perform well for system validation. The SDs provide a good visual formalism for specifying scenario requirements, but the system testing is a validation testing only. Validation is the process of running simulations of the system being built, which gives the benefits of exercising the actual system, but at the cost of test coverage, i.e., it is very difficult, if not impossible, to simulate every possible trace through a system. Verification is the process of building a model of the system and performing formal checking of the model, i.e., model-checking. The technique enables testing of all possible traces through a system, but the downside to this

2 Introduction

The scenario shows a channel change in the set-top box. First the channel data information is looked up in the ChannelDB, then the information is passed to the DVB layer. The DVB layer first stops the Demux, sets channel information in the StreamProvider, starts the de-multiplexing and starts parsing DVB packets in the service information database, SIDB.

Figure 1.1: Sequence diagram from Rhapsody modelling a scenario from a set-top box.

approach is that it is only a model of the system that is being tested and not the actual system.

Tools for verification of systems are used in the industry today, an example is Statemate MAGNUM from I-LOGIX [i-l04]. Statemate provides an environment for specifying, analysing, designing, documenting, and verifying complex reactive systems [HLN<sup>+</sup>88]. Spin is another verification system, used for the formal verification of distributed software systems [spi04]. visualSTATE [vis04] from IAR systems is a tool used for generating state machines, which can be documented, simulated, verified, and finally, code-generated through visualSTATE. UPPAAL, which is used in this project, is developed between Uppsala and Aalborg Universities [upp04]. UPPAAL is an integrated tool environment for modelling, validation,

and verification of real-time systems in the form of networks of timed automata. Another verification tool for real-time systems is the KRONOS tool [DOTY95].

Most of the above tools support the developer during all phases of the software development, but the testing phase must be emphasised as this is the final step before releasing the product. When testing a product, a good requirements specification is important as this is the exit criteria for the final product. It therefore seems natural to use the requirements specification to automate the validation and verification of the product. Requirements specification can be done in many ways and different representations exist, e.g., use cases, state machines, MSCs, and in particular LSCs (live sequence charts) seem to be a powerful way to express property specifications with respect to validation and verification. The goal of the requirement specification is to develop a clear and unambiguous understanding of the software to be developed and the requirements specification is the basis for the software testing.

One of the problems with the domain of formal specification is that the methods developed demand that practitioners need to be experts within the property specification language used in order to gain full potential of the tools. It has long been known that computer programming languages are meant for humans to understand and not machines, thus the popularity of high level programming languages, but in formal specification, logic languages are still being used instead of newer diagrammatic requirements specification languages, which can be used as a high level specification language compared to logic languages. [vL00, BS03].

## 1.1 Diagrammatic requirements specification

A high-level modelling language, which may be used for expressing property specifications, is the Unified Modelling Language (UML) [HT03]. UML is a language for specifying object-oriented software, and it is widely used in the industry. Among other things, UML contains a diagrammatic requirements specification formalism, the MSC.

Unfortunately, MSCs have several deficits. They only show possible and safe behaviour, i.e., they only specify that nothing bad will ever happen, and they cannot express liveness properties that something may happen nor enforce progress through a chart. In addition, the MSC constructs of conditions do not have a formal semantics, i.e., they are merely comments in the chart, whereas conditions are first-class citizens in LSCs and affect the run of a model. A formal semantics is also lacking for the timer durations, and so they are ignored in MSCs as well. Fi-

4 Introduction

nally, it is not possible to specify simultaneity in MSCs, i.e., that more than one event may happen at the same time [Klo03, BDW<sup>+</sup>02, DH01].

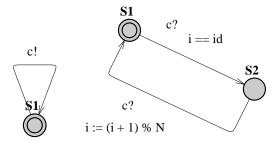

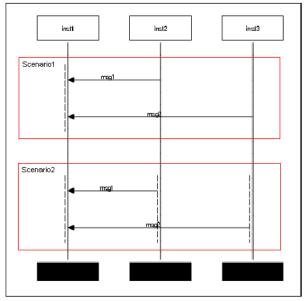

LSCs are a graphical notation for specifying temporal relationships between signals and events, and they are an extension of MSCs that provide stronger expressive power in order to make up for the deficits described above, especially concerning liveness, i.e., representation of provisional versus mandatory behaviour in systems [DH01]. Work is being done in relating specifications in LSCs to UML's diagrams [KW02], [DW03], and [dBBGdR03], which indicates that CASE-tools will soon adopt variants of this specification language. Statemate MAGNUM from I-LOGIX has already been extended with support for LSCs [BDW00], and work is in progress for extending Rhapsody as well [BJK+01]. See Figure 1.2 for an example of an LSC.

This example shows a simple LSC which specifies that at least one scenario must exist with the specified messages.

Figure 1.2: An existential LSC.

LSCs enable the developer to construct requirements specifications in a visual fashion and does not require background knowledge in formal validation and verification.

## 1.2 Project goals

The purpose of this project is to introduce LSCs as a diagrammatic specification language in the formal verification tool UPPAAL. In order to allow LSCs to be used in combination with UPPAAL, the semantics of both feature sets are described informally and additionally the semantics of UPPAAL is formally described in order to determine what properties from UPPAAL models are suitable for specification in LSCs. Based on the feature selection, a formal semantics of the LSC subset is described.

5

UPPAAL has been chosen because it is a verification tool for timed automata and the behaviour of these automata may be specified by LSCs, which are suitable for interobject communication in the form of messages. Another reason is that UPPAAL uses Timed Computation Tree Logic (TCTL) to specify properties for verification, and TCTL cannot specify message sequences, which is one of LSCs strong features. Furthermore, as UPPAAL is developed in-house, i.e., at Aalborg University, it is an obvious candidate because it is easier to acquire detailed knowledge about the tool.

If the analysis determines that some elements in the languages are not possible to translate such elements are disregarded in the final result. This means that the formal understanding of the subset of LSCs adopted in this report is defined in relation to UPPAAL models, and the LSC elements not in this subset must be prohibited from being used or just ignored when traversing an LSC. Correspondingly, elements in the UPPAAL language, which cannot be captured by LSCs, limit what kind of properties LSCs can be used to specify.

The requirements specification is verified by extracting properties from LSCs and these properties are used to test UPPAAL models. More specifically, the computation tree from UPPAAL is traversed and the LSC properties are used to query this tree. Since LSCs focus on interobject communication, messages and message sequences are the most important properties to test in the UPPAAL models. This is one of the problems with the specification language used in UPPAAL, TCTL, as it has no means of referring to messages. Thus, LSCs have the potential to be a good supplement compared to TCTL with respect to semantic expressibility as well as general user-friendliness.

A prototype engine, PEEL, is implemented to perform the testing of UPPAAL models with LSC specifications. This prototype is based on a graphical LSC editor, and the properties from this editor are extracted and tested against the UPPAAL models, see Figure 1.3. PEEL is applied to a number of experimental cases in order to evaluate PEEL and the diagrammatic approach for specifying properties. The evaluation includes a discussion of advantages and disadvantages of visual specification as opposed to logic languages like TCTL. Furthermore, the application of LSCs as a specification language in combination with the verification tool UPPAAL are evaluated.

6 Introduction

This is an overview of the PEEL prototype. PEEL uses an LSC to verify that a UPPAAL model is correct.

Figure 1.3: Overview of PEEL.

#### 1.3 Related work

Several studies regarding usage of LSCs as a specification language have been performed. In [KKR02], LSCs are used as a specification language which introduces a visual environment for designing and validating software systems early in the development process. The authors propose LSCs as a visual means of specifying properties of a system design, so the environment can be used by practitioners unknowing of formal methods. LSCs are translated to AR-automata, which are run in parallel to the design being validated. The automata simulate the design and therefore some features of LSCs, e.g., liveness requirements are not used. The environment helped the authors find several design flaws in a train system they had built. Also, they found that the effort in specifying the requirements had been reduced, which combined with the visual counter-examples shortened their validation cycles significantly. We use LSCs as a visual means of specifying properties as well, but [KKR02] does unlike the work presented in this report not adopt LSCs liveness features. This is because they simulate the LSCs using finite automata for validating the design, whereas we verify behaviour of models and thus need to test for infinite traces. The authors conclude that less effort is required when specifying properties in LSCs. We agree, it is more intuitive to use than TCTL.

A case study used an extension of LSCs to specify parts of an air traffic control system which modelled all scenarios of the system [BHK03]. In fact they found that LSCs are so straightforward that they believe non-technical stake holders can understand and help capture LSCs. We agree with [BHK03] on their remark of how easy it is to construct LSCs, and this is one of the motivations for our project - to ease specification of verification properties.

1.4 Overview 7

[BDW<sup>+</sup>02] presents a methodology for developing train system applications based on Statemate, which is extended to include verification and testing facilities in the form of a model-checker and an automatic generation of test vectors. Also, LSCs as a specification language is included in the extension. The difference from our work is that instead of constructing a verification engine from bottom, we use a small verification engine on top of the existing UPPAAL engine. This requires us to explore the symbolic state space of the UPPAAL model through the computation tree when testing the message sequence. UPPAAL'S TCTL is still used for non-message related property checking.

In [BG01] the authors apply LSCs on hardware protocols. They found that LSCs have a significant potential for use when formally specifying hardware standard protocols if ignoring a weakness with the timing model. Instead of having a full timing model, MSCs and LSCs rely on partial order imposed by the order in which events occur along a life line in which messages are passed between processes. They determined that LSCs are not strong enough to formally specify protocol standards, but as LSCs were developed for system level and software design the authors were not surprised of this. The authors want to extend LSCs with a full timing model, thus eliminating the weakness. This weakness is corrected in Klose's dissertation [Klo03], but Because it has been chosen not to use Klose's extension in this report, the LSCs adopted in our LSC subset do not have a full timing model either. The total order of messages is sufficient for specifying the order of the messages and thus message traces.

#### 1.4 Overview

First, an introduction of UPPAAL is presented in Chapter 2. It includes a formal semantics of UPPAAL models and the subset of TCTL used.

Next, LSCs are described informally in Chapter 3 and a relevant subset is described formally to be used in the PEEL engine.

Chapter 4 describes the property extraction engine. Chapter 5 provides experiments of how LSC diagrams can be used to verify UPPAAL automata with the PEEL engine, and finally an evaluation and conclusion of the project is given in Chapter 6 together with directions of future work.

#### **Contents**

| 2.1 | Inform | nal description                          |

|-----|--------|------------------------------------------|

|     | 2.1.1  | Model constructs                         |

|     | 2.1.2  | Model behaviour                          |

| 2.2 | Forma  | al description                           |

|     | 2.2.1  | Network                                  |

|     | 2.2.2  | Maximal delay                            |

| 2.3 | Requi  | rements specification language (TCTL) 19 |

|     | 2.3.1  | Local properties                         |

|     | 2.3.2  | Temporal properties                      |

| 2.4 | Exam   | ple                                      |

| 2.5 | Summ   | nary                                     |

UPPAAL is a tool for modelling, validating, and verifying real-time systems. It models systems as a collection of non-deterministic processes with finite control structures and real-valued clocks, i.e., network of timed automata. The processes synchronise through channels and may exchange values through shared, finite data structures.

This chapter gives an informal as well as a formal description of UPPAAL and the requirements specification language, TCTL, used. An example of a UPPAAL model is presented, and use of UPPAAL as a model checking tool is introduced.

## 2.1 Informal description

This section introduces the system description language of UPPAAL. The presentation is based mainly on [DMY03] and the documentation accompanying the UPPAAL application. The static and the dynamic elements of a UPPAAL model are described. The static elements are the language constructs, and the dynamic elements are the behaviours of the constructs, i.e., what a configuration is and how a model can progress from one configuration to another.

#### 2.1.1 Model constructs

A UPPAAL model is a network of timed automata. The automata have constructs for holding data, and the automata can synchronise over globally declared channels, either through *binary synchronisation* in the form of a hand-shake or through *broadcast synchronisation*.

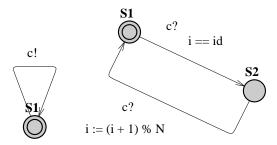

Each automaton is represented by a finite, directed graph, where edges are labelled with guards, synchronisation labels, and updates in the form of variable assignments. The nodes in the graph are referred to as *locations*, and the edges as *transitions*. The *initial location* is marked with a double circle. Figure 2.1 shows an example UPPAAL model.

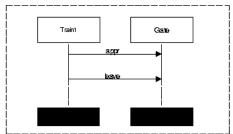

The model shows an example of a UPPAAL network with broadcast. The left is a sender and the right is a receiver model template.

Figure 2.1: The sender and receiver templates of a Broadcast example.

#### **Data constructs**

Data in the model are stored in clocks and variables. Clocks contain non-negative real values, i.e., values in the set  $\mathbb{R}_{\geq 0}$ . Variables can be of type boolean or finite subrange of integer, and be ordered in multi dimensional arrays. Constant values can also be declared.

Integers must be declared with a finite bound, e.g., [-5,5] in order to restrict the number of configurations, the maximum bound is [-32768, 32767], which is used if no bound is explicitly defined. Boolean variables take the values *true* or *false*, and they are type consistent with integers as in C++, i.e., 0 evaluate to *false* and all other integer values evaluates to *true*. Likewise, *false* evaluates to 0 and *true* evaluates to 1.

Both clocks and variables can be declared locally or globally. Normal scope rules apply, meaning that locally declared names override globally declared names.

#### Channels

As already mentioned, automata synchronise over channels, but no information is sent over the channels, instead, information may be exchanged through global variables.

A channel can be declared *urgent*, which means that if transitions labelled with this channel are enabled, then no time delay must occur before the enabled transitions are carried out. The type of the channel used for synchronisation decides whether the synchronisation is binary, or if marked with *broadcast*, one-to-many. A channel can be marked as both urgent and broadcast. A binary synchronisation channel is a blocking synchronisation, whereas a broadcast synchronisation is non-blocking, a sending transition does not wait for a recipient, but can always be enabled.

#### Locations

Locations are the nodes of the directed graph defining an automaton. There are two special types of locations: urgent locations and committed locations. An urgent location is a location in which time may not progress, until the location is left again. A committed location is an urgent location with an additional constraint; transitions from committed locations have precedence over all other enabled transitions, thus committed locations can be used to model atomicity. The special location types are marked with a U and C for urgent and committed locations, respectively.

It is possible to attach a boolean expression over clocks and variables to a location, an *invariant* that needs to be fulfilled while the location is active. It is not permitted to set lower bounds on clock values in invariants and the *or* and *not* operators are restricted to expressions over integers. Expressions in invariants must be side effect free. Appendix A contains a syntax for invariant expressions.

#### **Transitions**

Transitions, being the edges of the directed graph, describe the possible steps from a given location. The steps may be restricted by *guards*, which are expressions that must evaluate to *true* before a transition is enabled, and *synchronisation labels*,

which are labels indicating synchronisation between automata. A transition may furthermore contain *updates*, which are variable and clock assignments.

A guard is a set of side effect free boolean expressions over variables, clocks, and integers, but unlike location invariants they are not restricted from setting lower bounds on clocks. A guard on an urgent channel or on a broadcast receiving channel may not contain any clocks. Appendix A contains a syntax for guards.

Synchronisation labels are channels marked with a direction. The synchronisation scheme in UPPAAL is similar to the synchronisation scheme used in the CCS calculus [LPY97]. Outgoing transitions with e! labels are enabled when there is another outgoing transition with the corresponding label e? at another active location, and neither guards nor location invariants restrict the progress. Because broadcast is non-blocking, a receiver is not necessary in order to enable a transition. The transition marked with e! is evaluated first and the set of receivers last. The evaluation order is the order in which the automata instances are declared in the model. e is a side effect free expression evaluating to a channel, see a BNF with the syntax in Appendix A.

#### 2.1.2 Model behaviour

The behaviour of a model can be seen as a sequence of computation steps from an initial configuration. For an automaton a configuration is a location and a value of clocks and variables. The *initial configuration* of the automaton is the configuration with the active location being the start location and all variables and clocks having the initial values. The combined configurations of all the automata and the values of variables and clocks constitute the configuration of a network of automata.

Transitions may change the active location and the variable values as well as reset clocks. If there is no synchronisation label, a transition is referred to as an *internal* transition step, and when there is a synchronisation label it is either a binary synchronisation step or a broadcast synchronisation step. When the automaton is in a location time can progress, but some constructs restrict time from progressing:

- Urgent locations,

- Committed locations,

- Urgent channels, and

- Location invariants on clocks.

Thus, a computation step on a model is either an internal transition step or a synchronisation step. The behaviour of a model can now be more precisely defined. It is a set of sequences of configurations, where each sequence starts from the initial configuration, and for every two consecutive configurations,  $\sigma[k]$  and  $\sigma[k+1]$ , there must exist a computation step that converts  $\sigma[k]$  to  $\sigma[k+1]$ . A sequence of configurations is referred to as a *trace*.

For a more in-depth description of all language constructs, the syntax, etc. please consult the help file from the, as of this writing, latest UPPAAL version 3.4.5.

### 2.2 Formal description

Now that the informal description of the constructs of an UPPAAL model has been given, the formal description is presented. This section is based on the semantical descriptions presented in the documentation accompanying the UPPAAL application, [BLL<sup>+</sup>95], and [DMY03].

A UPPAAL model is a network of timed automata. A timed automaton is defined as a tuple:

$$\Phi = \langle \mathcal{V}, \mathcal{L}, \mathcal{A}, \Theta, \mathcal{T}, \Pi \rangle$$

consisting of:

- $\mathcal{V} = \mathcal{D} \cup \mathcal{C}$  is the finite set of variables.  $\mathcal{V}$  is partitioned into  $\mathcal{D} = \{d_1, ..., d_n\}$  the set of data variables, and  $\mathcal{C} = \{c_1, ..., c_n\}$  the set of clocks. Data variables are integers or booleans, and they may be defined to be constants, and the clocks are always of type non-negative real,  $\mathbb{R}_{\geq 0}$ . Variables may be ordered in arrays.

- $\mathcal{L} = \{l_0, ..., l_n\}$  is the finite set of locations. Locations can carry the attribute *urgent* or *committed*. Urgent and committed locations are subsets of  $\mathcal{L}$ , thus the two sets are denoted by  $\mathcal{L}_u$  and  $\mathcal{L}_c$ , respectively.

A configuration is  $\sigma = (l, v) \in \Sigma$ , where  $\Sigma$  is a set of configurations, location  $l \in \mathcal{L}$ , and a type consistent valuation v of the variables in V.

A variable assignment is a mapping from clock variables C to the non-negative reals and data variables D to integers or booleans. For a variable assignment v and a delay d,  $v \oplus d$  denotes the variable assignment such that  $(v \oplus d)(x) = v(x) + d$  for any clock variable x and  $(v \oplus d)(i) = v(i)$  for

any integer or boolean variable i. In other words,  $\oplus$  changes only the value of clock variables, i.e., time progression only effects clock variables.

•  $\mathcal{A} = \{\alpha_1, ..., \alpha_n\}$  is the finite set of synchronisation channels on which a network of automata can synchronise. From the set  $\mathcal{A}$  the set  $\mathcal{S}$  of synchronisation labels is formed. Synchronisation is either binary or one-to-many, i.e., one automaton sending and one or more receiving. Sending on channel  $\alpha$  is denoted by  $\alpha$ ! and receiving by  $\alpha$ ?. Also, as not all transition steps are synchronising steps,  $\epsilon$  denotes an internal transition step without any synchronisation. The set of synchronisation labels possible is thus defined as:  $\mathcal{S} = \{\alpha?, \alpha!, \epsilon\}$  for  $\alpha \in \mathcal{A}$ .

An urgent channel is a special instance of a synchronisation channel on which automata must synchronise as soon as possible, thus the set of urgent channels is  $\mathcal{A}_u \subseteq \mathcal{A}$ . A channel can also be marked as a broadcast channel, which means that the synchronisation is one-to-many and non-blocking, thus  $\mathcal{A}_b \subseteq \mathcal{A}$  where  $\mathcal{A}_b$  is the set of broadcast channels. A channel c can be marked as both urgent and broadcast, thus  $c \in \mathcal{A}_u \cap \mathcal{A}_b$

- The initial condition  $\Theta$  specifies a start location  $l_0 \in \mathcal{L}$  and an initial value of all variables,  $\mathcal{V}_0$ .

- $\mathcal{T}$  is the finite set of transitions. Each transition  $\tau \in \mathcal{T}$  is a single relation:

$$\mathcal{T} \subseteq \Sigma \times \mathcal{S} \times \Sigma$$

that relates one configuration and a synchronisation label to another configuration.

Π is the finite set of location invariants, i.e., invariant conditions that must evaluate to *true* on a location, for that location to be active. The invariants are used to specify local restrictions on the progress of an automaton. An invariant is a boolean expression over variables, V, but it is not permitted to set lower bounds on clock values in invariants.

The location invariants are described by a total function *inv* that based on a configuration evaluates whether the conditional expression is true or not:

$$inv : \mathcal{L} \times \mathcal{V} \rightarrow \{true, false\}$$

Two additional total functions are introduced, g and u. The function g evaluates the guard condition for a transition based on the values of the variables:

$$g: \mathcal{V} \to \{true, false\}$$

and the function u evaluates the set of updates carried on a transition:

$$u: \mathcal{V} \to \mathcal{V}'$$

Three different computation steps are possible: internal transition steps, binary synchronisation steps, and broadcast synchronisation steps. The internal transition step is possible in both a single automaton and a network of automata, whereas the binary and broadcast synchronisation steps are only possible in a network of automata.

An internal transition step from l to l' can be taken, just when it is enabled, i.e., g(v) evaluates to true on v and inv(l',v') on v', where the resulting value assignment v' is the result of the update evaluation u(v) and l' is the resulting active location. The internal transition step is defined as:

$$\begin{array}{ccc} (l,v) \stackrel{\epsilon}{\longrightarrow} (l',v') & \text{iff } g(v) \wedge \mathit{inv}(l',v') \\ & \text{where } v' = u(v) \end{array}$$

#### 2.2.1 Network

Synchronisation steps can only be performed on the network level, thus before proceeding with the specification of synchronisation steps, the network level needs to be specified.

A configuration of a network of automata,  $\overline{\Phi} = \langle \Phi_1, \dots, \Phi_m \rangle$  is:

$$\overline{\sigma} = (\overline{l}, v)$$

where  $\overline{l} = \langle l_1, ..., l_m \rangle$  contains the active locations for all automata and v is a type consistent valuation of the set of variables  $\mathcal{V}_1 \cup ... \cup \mathcal{V}_m$ .

It follows that the initial configuration of  $\overline{\Phi}$  is  $(\overline{l}_0, v_0)$ , where  $\overline{l}_0$  is the initial control vector, i.e., the initial locations of all the automata, and  $v_0$  is the initial valuation of  $\mathcal{V}$ .

The invariant function must also hold when used on a network of automata. The function evaluates to *true* when the invariants hold for all individual automata:

$$inv : \mathcal{L} \times \mathcal{V} \rightarrow \left\{ \begin{array}{ll} true & \text{iff } \forall \ l \in \overline{l} : inv(l, v) \\ false & \text{otherwise} \end{array} \right.$$

A network lifts transitions of the individual automata, thus the possible transitions for the individual automaton is used as the basis for the formal description.

The basic binary synchronisation step performed on a network is defined as:

$$(\overline{l},v) \xrightarrow{\alpha} (\overline{l}',v') \quad \text{iff } g(v) \wedge \mathit{inv}(\overline{l}',v') \\ \quad \text{where } v' = u(v) \wedge \alpha \in \mathcal{A} \setminus \mathcal{A}_b$$

The basic broadcast synchronisation step is defined as:

$$(\overline{l}, v) \stackrel{\beta}{\longrightarrow} (\overline{l}', v')$$

iff  $g(v) \wedge inv(\overline{l}', v')$  where  $v' = u(v) \wedge \beta \in \mathcal{A}_b$

Next follows the specification of the synchronisation steps on the network level, i.e., the changes of all effected automata.

In the internal transition step, i.e., a single automaton takes a transition without any synchronisation, only the automaton in question changes location, and the global set of variable values changes. The internal transition step is defined as:

$$\frac{\langle ..., l_i, ... \rangle \stackrel{\epsilon}{\longrightarrow} \langle ..., l'_i, ... \rangle}{(\langle ..., l_i, ..., l_k, ... \rangle, v) \stackrel{\epsilon}{\longrightarrow} (\langle ..., l'_i, ..., l_k, ... \rangle, v')} \quad \text{iff } g_i(v) \wedge \mathit{inv}(l'_i, v') \wedge \mathit{inv}(l_k, v') \\ \quad \text{where } v' = u_i(v)$$

for an internal step in a automaton  $\Phi_i$ .

When a binary synchronisation step occurs two automata change location and there is an update of the global variables as well. The sender updates the variables first and the receiver updates last:

$$\frac{\langle ..., l_i, ... \rangle \xrightarrow{\alpha!} \langle ..., l'_i, ... \rangle \ \langle ..., l_k, ... \rangle \xrightarrow{\alpha?} \langle ..., l'_k, ... \rangle}{(\langle ..., l_i, ... \rangle, v) \xrightarrow{\alpha} (\langle ..., l'_i, ..., l'_k, ... \rangle, v')} \quad \text{iff } g_i(v) \land g_k(v) \land inv(l'_i, v') \land inv(l'_k, v') \\ \quad \text{where } v' = u_k(u_i(v)) \land \alpha \in \mathcal{A} \setminus \mathcal{A}_b$$

for a sending automaton  $\Phi_i$  and a receiving automaton  $\Phi_k$ .

The broadcast synchronisation step has one sender and possible many receivers that all change locations and the global variable values also change. The sender updates first, and the receivers update in the same order as they have been defined in the model:

$$\begin{array}{c} \underbrace{\langle ..., l_i, ... \rangle \xrightarrow{\beta!} \langle ..., l'_i, ... \rangle}_{(\langle ..., l_i, ..., l_k, ...)} \underbrace{\langle ..., l'_k, ..., l'_k, ..., l'_k, ..., l_n, ... \rangle}_{\beta?} \langle ..., l'_k, ..., l'_n, ... \rangle} \underbrace{\langle ..., l'_i, ..., l'_k, ..., l'_n, ... \rangle}_{(\langle ..., l_i, ..., l_k, ..., l'_n, ..., l'_n, l'_n,$$

for a sending automaton  $\Phi_i$  and receiving automata  $\Phi_k \dots \Phi_n$ .

It is also possible to have an empty set of receivers of a broadcast synchronisation, as the broadcast synchronisation is a non-blocking synchronisation call:

$$\frac{\langle ..., l_i, ... \rangle \xrightarrow{\beta!} \langle ..., l'_i, ... \rangle}{(\langle ..., l_i, ..., l_k, ... \rangle, v)} \quad \text{iff } g(v) \wedge \mathit{inv}(l'_i, v') \wedge \mathit{inv}(l_k, v') \\ \quad \text{where } v' = u(v) \wedge \beta \in \mathcal{A}_b$$

for a sending automaton  $\Phi_i$ . Here, only the sender changes location and the global variable set also change.

#### 2.2.2 Maximal delay

A side condition MD is given on all transitions, which returns the maximal delay allowed. If a process modelled by an automaton  $\Phi$  is in a location l with a number of outgoing transitions with guards, the process may have to wait for these guards to become true in order to leave l. It is not desirable that the process waits in this location forever, thus some discrete transition must be taken within a certain time

bound. This bound should be the maximal time before all the guards are completely closed, i.e., they will never become *true* again. If the active location is an urgent or a committed channel, no time delay is allowed.

The maximal delay for an automaton is formalised as:

$$MD(l,v) = \begin{cases} 0 & \text{iff } \exists \ l \in \mathcal{L}_u \cup \mathcal{L}_c \\ max\{d | (l,v) \xrightarrow{\mathcal{S}} (l',v')\} & \text{otherwise} \\ & \text{iff } g(v \oplus d) \\ & \wedge \ inv(l,v \oplus d) \wedge inv(l',v' \oplus d) \\ & \text{where } v' = u_s(v) \end{cases}$$

Also, MD = 0 when a configuration (l, v) has all outgoing transitions from the active location l completely closed.

#### Network

Next, the notion of maximal delay is extended to networks of automata. This insures that synchronisation on urgent channels happens immediately.

The maximal delay for a network of automata is formalised as:

$$\mathit{MD}(\overline{l},v) = \left\{ \begin{array}{ll} 0 & \text{iff } \exists \ \alpha \in A_u, l_i, l_j \in \overline{l} : \\ (l_i,v) \xrightarrow{\alpha!} (l'_i,v') \ \& \ (l_j,v) \xrightarrow{\alpha?} (l'_j,v') \\ & \text{where } v' = u_j(u_i(v)) \\ \lor \ \exists \ \beta \in A_u \cap A_b, l_i \in \overline{l} : \\ (l_i,v) \xrightarrow{\beta!} (l'_i,v') \\ & \text{where } v' = u_i(v) \\ & \text{min}\{\mathit{MD}(l,v)|l \in \overline{l}\} \end{array} \right.$$

If a synchronisation channel  $\alpha$  or  $\beta$  is an urgent channel, and the locations with the urgent channel is in the currently active set, then the maximal delay is 0, i.e., no delay is permitted. If on the other hand, there is no urgent channels pending on the active locations, then the shortest of all maximal delays of the processes of the network is the maximal delay, because this is the maximal allowed delay before some action must be taken.

### 2.3 Requirements specification language (TCTL)

UPPAAL's model-checker is able to verify certain properties such as reachability, i.e., whether certain configurations of the model are reachable from the initial configuration. This is done by constructing a timed computation tree and applying graph algorithms in order to examine the tree. The formulae that the model-checker is to prove or disprove are defined in a requirement specification language, which is a subset of branching time computational tree logic (TCTL) [DMY03, Dav03], where the time part comes from the possibility of constraints on clocks.

A TCTL formula consists of two parts; a local property and a temporal property. The local property describes a property that is to hold for a single configuration, whereas the temporal property specifies to what extend, in traces and configurations, the local properties are to hold, i.e., for all or a single trace, and for all or a single configuration within the given traces.

#### 2.3.1 Local properties

A local property is specified by boolean expressions over location names, clocks, and data variables of the UPPAAL model in question.

Besides the standard relational operators, <, <=, ==, !=, >=, and > as well as the boolean operators *and*, *or*, *not*, and *imply*, the expressions may contain the special keyword *deadlock*, which evaluates to *true* only in the case of a deadlock, i.e., no transitions from the active location are enabled. Specific locations are referred to as  $\Phi.l$ , where  $\Phi$  is a timed automaton in the UPPAAL model and l is a location in  $\Phi$ . A local property has the form specified in the following BNF:

```

p := deadlock

for \Phi \in \overline{\Phi} \wedge l \in \mathcal{L}_{\Phi}

\Phi . l

c\bowtie x

for c \in C, \bowtie \in \{<,<=,==,!=,>=,>\}, x \in \mathbb{Z}

c_1 - c_2 \bowtie x \quad \text{for } c_1, c_2 \in \mathcal{C}, \bowtie \in \{<, <=, ==, !=, >=, >\}, x \in \mathbb{Z}

d_1 \bowtie d_2 for d_1, d_2 \in \mathcal{D} \cup \mathbb{Z}, \bowtie \in \{<, <=, ==, !=, >=, >\}

(p)

for a local property p

for a local property p

not p

p_1 and p_2

for local properties p_1 and p_2

for local properties p_1 and p_2

p_1 or p_2

for local properties p_1 and p_2

p_1 imply p_2

```

A local property evaluates to either *true* or *false* based on the configurations of the model. As the intuitive idea of the semantics of the above constructs should be clear, the semantical evaluation of the constructs are formally described.

#### **Formal description**

Given a configuration  $\overline{\sigma} = (\overline{l}, v)$ , a local property p holds in  $\overline{\sigma}$  denoted  $\overline{\sigma} \models p$ , based upon the following rules:

```

\overline{\sigma} \models \text{deadlock}

iff no delay or action transitions are enabled in \overline{\sigma}

\overline{\sigma} \models \overline{\Phi}.l

iff l = l_i \in \overline{l} for \overline{\Phi} = \overline{\Phi}_i \in \overline{\Phi}

iff v(c) \bowtie x, \bowtie \in \{<, <=, ==, !=, >=, >\}

\overline{\sigma} \models c \bowtie x

\overline{\sigma} \models c_1 - c_2 \bowtie x iff v(c_1) - v(c_1) \bowtie x, \bowtie \in \{<, <=, ==, !=, >=, >\}

iff v(d_1) \bowtie v(d_2), \bowtie \in \{<, <=, ==, !=, >=, >\}

\overline{\sigma} \models d_1 \bowtie d_2

\overline{\sigma} \models (p)

iff \overline{\sigma} \models p

\overline{\sigma} \models \text{not } p

iff \neg(\sigma \models p)

\overline{\sigma} \models p_1 \text{ or } p_2

iff \overline{\sigma} \models p_1 \vee \overline{\sigma} \models p_2

iff \overline{\sigma} \models p_1 \wedge \overline{\sigma} \models p_2

\overline{\sigma} \models p_1 \text{ and } p_2

iff \neg(\overline{\sigma} \models p_1) \vee \overline{\sigma} \models p_2

\overline{\sigma} \models p_1 \text{ imply } p_2

```

where  $c \in \mathcal{C}$ ,  $x \in \mathbb{Z}$ , and  $d \in \mathcal{D} \cup \mathbb{Z}$ .

#### 2.3.2 Temporal properties

Temporal properties specify when a local property is to hold during a computation, in other words, they specify some or all configurations in the computational tree that is to satisfy some local property p. The two quantifiers  $\forall$  and  $\exists$  refer to both paths and configurations of the computation tree. The path aspect of a requirement formula is specified by A and E, and the configuration aspect is specified by [] and  $\Leftrightarrow$ , for  $\forall$  and  $\exists$ , respectively. By combining the path and configuration aspects it is possible to specify the following four types of formulae, where p is a local property; A[], A $\Leftrightarrow$ , E[], and E $\Leftrightarrow$ . The specification language also provides a fifth type, a *leads to* property. It is written as -->, and it is semantically equal to A[] ( $p_1 imply A \Leftrightarrow p_2$ ).

The five temporal property types evaluate to either *true* or *false* based on the evaluation of the local property for each of the configurations specified by the temporal property. This means that if some TCTL formula is to hold for some UPPAAL model  $\overline{\Phi}$ , the local property p is to hold for the set of configurations specified by the temporal properties. Intuitively, the semantics are:

2.4 Example 21

| A[]p       | for all paths $p$ holds for all configurations, i.e., $p$ invariantly holds. |

|------------|------------------------------------------------------------------------------|

| A <> p     | for all paths $p$ holds for some configuration, i.e., $p$ is inevitable.     |

| E[]p       | for some path $p$ holds for all configurations, i.e., $p$ may always hold.   |

| E <> p     | for some path $p$ holds for some configuration, i.e., $p$ is reachable.      |

| $p_1> p_2$ | $p_1$ eventually leads to $p_2$ .                                            |

#### **Formal description**

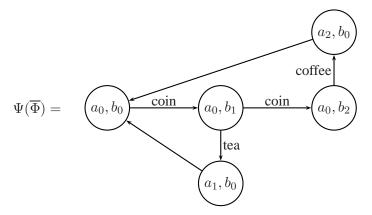

Let  $\Psi(\overline{\Phi})$  be the set of finite timed traces of the model  $\overline{\Phi}$ , a trace in  $\Psi(\overline{\Phi})$  is  $\overline{\sigma}[1,K]$  of length K. Letting the k'th configuration in a trace be denoted by  $\overline{\sigma}[k]$ , the following rules define the semantics of the temporal properties:

### 2.4 Example

This section contains an example of a UPPAAL model and TCTL property formulae. The example is a coffee and tea vending machine, see Figure 2.2.

The coffee\_unit sends coins to the control\_unit and servers a cup of tea or coffee, when informed to. A cup of tea is server within three time units, c <= 3 and a cup of coffee within five time units, c <= 5. The control\_unit dispenses either a cup of tea or coffee, depending on the amount of coins inserted. One coin dispenses a cup of tea if a second coin is not inserted within five time units, see invariant c <= 5. Location b2 is urgent, meaning that when a second coin is received no delay is permitted before the coffee message is sent.

Figure 2.2: UPPAAL model of a coffee vending machine.

#### **Computation graph**

When UPPAAL formally verifies a network of automata, it takes advantage of various internal data representations. The data representation are not described here, see [BBD<sup>+</sup>02] for information about the internal data representations and their usage.

In order to be able to check for the existence of a message trace a computation graph is sufficient. The UPPAAL verification engine, *verifyta*, has support for outputting a UPPAAL model as a finite state machine, FSM - note that this is an internal unpublished version of verifyta. Clocks are not represented in the FSM format but data variables effect the state space. Figure 2.3 shows the FSM output as a computation graph for the coffee vending machine example.

The graph shows the UPPAAL location sets as computation configurations. There are no variables in the UPPAAL model used in this example. If there were variables, the possible variable values would be a part of the configurations, e.g., a variable with a range of three in every UPPAAL model location could triple the number of configurations.

Figure 2.3: FSM computation graph for the vending machine example.

#### **UPPAAL TCTL queries**

Next follows some example TCTL queries that can be checked via UPPAAL for the vending machine example.

• A[] not deadlock: This expression checks the model for deadlocks. If there is a possibility for a deadlock in the model, this query returns *false*.

2.5 Summary 23

• control\_unit.bl --> ( coffee\_unit.al or coffee\_unit.a2 ): The leads to operator tests for the possibility that a local property is eventually followed by some other property. This example tests that if the control\_unit is in location bl, i.e., one coin has been deposited, then the model will eventually be in location all or all which means that either a cup of teal or coffee is dispensed.

The leads to operator must be used with caution, as it is easy to create a *false true* expression, i.e., an expression that is satisfied, but not because a property is eventually followed, but because the first property is never fulfilled. Consider control\_unit.bl and coffee\_unit.a2 --> (coffee\_unit.al or coffee\_unit.a2) is always satisfied, because location bl and a2 do never coincide.

### 2.5 Summary

UPPAAL is a tool for modelling, simulating, and verifying non-deterministic timed finite state automata. The supported data types are integers, booleans, and clocks. Synchronisation between processes are performed through channels, either in the form of a blocking binary one-to-one synchronisation, or a non-blocking broadcast one-to-many synchronisation. Communication, i.e., exchange of information must be performed through shared variables.

The verification of UPPAAL models is performed through the querying of a subset of TCTL expressions. TCTL expressions consist of two properties, a local property and a temporal property. The local property is a boolean expression over automata locations and conditions, whereas the temporal property expresses the range of the local property, i.e., to what extend in traces and configurations the local property must be satisfied.

The modelling language of UPPAAL, and the requirement specification language, TCTL, are specified informally as well as formally in order to be able to compare functionality with LSCs. The comparison is used to identify properties of LSCs that can be used to verify UPPAAL models.

Next chapter gives an introduction to LSCs, a limitation of LSC features, and description of how they are used to specify properties for UPPAAL model verification. The semantics of the selected LSC subset is formally described.

# 3 Live Sequence Charts

#### **Contents**

| 3.1 | LSC constructs          |                             | 20 |

|-----|-------------------------|-----------------------------|----|

|     | 3.1.1 Prechart          | s and activation conditions | 26 |

|     | 3.1.2 Universa          | al and existential charts   | 28 |

|     | 3.1.3 Tempera           | nture                       | 29 |

|     | 3.1.4 Instance          | s                           | 29 |

|     | 3.1.5 Message           | es                          | 3  |

|     | 3.1.6 Condition         | ons                         | 34 |

|     | 3.1.7 Subchar           | ts                          | 3. |

|     | 3.1.8 Coregion          | ns                          | 3  |

| 3.2 | <b>Extensions to th</b> | he basic LSC constructs     | 3  |

|     | 3.2.1 If-then-6         | else                        | 3  |

|     | 3.2.2 LSC act           | ivation mode                | 3  |

|     | 3.2.3 Simultan          | neous regions               | 4  |

|     | 3.2.4 Time .            |                             | 4  |

|     | 3.2.5 Local in          | variants                    | 42 |

| 3.3 | LSC behaviour           |                             | 4  |

| 3.4 | Formal descrip          | tion                        | 4  |

|     | 3.4.1 Semanti           | cs                          | 4  |

| 3.5 | Summary                 |                             | 5. |

As with MSCs, LSCs allow the user to specify scenarios by describing the interobject communication. MSCs are often used in the early development stages for capturing use cases through scenarios, but as development progresses and the designers gain more knowledge about the problem domain as well as confidence in their ideas, scenarios characterising the use cases are discovered and defined. This leads to a desire for more expressive ways of modelling the use cases. LSCs are an extension of MSCs introducing among other things liveness, i.e., specification of mandatory versus possible behaviour. This chapter presents an informal description of LSC features. The first part of the informal description is based on the original LSC description by Werner Damm and David Harel [DH01]. Extensions introduced by Klose in [Klo03] are considered. The graphical LSC notation used is that from the LSCEditor.

The informal description is partitioned into LSC constructs and LSC behaviour, the former being the constructive elements that LSCs are built from, and the latter being how these constructs are used to specify a model behaviour.

A subset of the LSC elements is selected based on what features are relevant for UPPAAL verification, and what elements that can be modelled by other elements. The selected LSC subset is used to reason about the application of LSCs as a requirements specification language for UPPAAL model verification. The limitation and application of LSC features are described when they are introduced.

Finally, this chapter presents a formal semantics of the selected LSC subset.

#### 3.1 LSC constructs

An LSC is a chart with instances, i.e., objects, along the horizontal axis and time down the vertical axis, see Figure 3.1. Interobject behaviour is specified as either messages or method calls between the instances. An LSC consists of several constructs used to define the interobject behaviour of a system.

#### 3.1.1 Precharts and activation conditions

To define when a chart is to become active, i.e., when the system should start behaving according to the chart, each chart is coupled with an initial condition. This condition can be in the form of an *activation condition* (as in MSCs) reflecting some configuration of the system, but it can also be defined as a chart of its own, called a *prechart* as in Figure 3.1. In the case of a prechart it is required that the system exhibits the entire behaviour defined in the prechart before the chart itself becomes active. Both an activation condition and a prechart can be specified for a given chart.

3.1 LSC constructs 27

An LSC with two instances. The top chart is a prechart and the bottom chart is a main chart.

Figure 3.1: LSC with prechart and main chart.

#### Limitation

An activation condition can be modelled by having a prechart with only a condition, see below for description of conditions. Thus, the activation condition construct is disregarded.

# **Application**

Precharts are tested by traversing the UPPAAL computation graph. When a prechart is satisfied, the main chart is tested from the configuration reached by evaluating the prechart. Figure 3.2 displays the connection of the prechart and main chart of Figure 3.1, the condition must hold in the snapshot from the first message until the dashed line, and from the dashed line until the next message it is another snapshot, i.e., snapshots do not overlap from one chart to another.

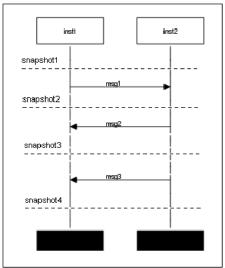

Snapshots are used to divide a chart into segments, see Figure 3.3 on page 31. The temperatures of the segments at a given time are collected in the snapshots, and the temperature of the snapshot is hot if any segment in the snapshot is hot,

otherwise it is cold. Snapshots correspond to a sequence of configurations in the FSM computation graph and they are more precisely defined in Section 3.3.

A prechart supports the same constructs as a main LSC, which means that the following descriptions of LSC constructs must be applied.

The prechart and main chart of Figure 3.1 has been merged to illustrate that any conditions must hold until the dashed line, from where a new snapshot is in effect. This means that there are four snapshots in this LSC.

Figure 3.2: The overlap of prechart and main chart.

#### 3.1.2 Universal and existential charts

An LSC has a chart mode that can be either *universal* or *existential*. An existential chart requires the existence of a trace satisfying the chart, while a universal chart requires that all traces conform to it. Generally, universal charts are more restrictive, and it should be possible to extract more restrictive properties from them. This is also the case, as existential charts yield a temporal property of *a trace exists*, *E*, and universal charts yield a temporal property of *for all traces*, *A*, see Table 3.1 on page 45. When drawing a universal chart, the box around the chart is a solid line, whereas a dashed line is used for existential charts.

#### **Application**

The chart modes, i.e., existential and universal, are handled such that a message trace in an existential chart only needs to exist, whereas a message trace in a universal chart must exist in all traces. This means that if a single trace in a computa-

3.1 LSC constructs 29

tion graph does not conform to the specification in a universal chart, the chart does not hold.

# 3.1.3 Temperature

In the original LSC description in [DH01], a *temperature* is associated with locations, conditions, and messages. The temperature can be either *hot* or *cold*. *Locations* in an LSC are those points on an instance axis where, e.g., messages and conditions are attached. Making a location hot means that it has to be left, thus enforcing progress down the instance axis. Conversely, a cold location never needs to be left, and thus the next location may never be reached.

In the LSC subset adopted in this project, temperatures are not associated to locations, instead coregions and segments have a temperature. The meaning of the temperature notation for the various LSC elements are summarised in Table 3.1 on page 45.

The limitations and applications regarding the temperatures for the LSC construct are given for each construct as they are introduced.

#### 3.1.4 Instances

Instances are the elementary building blocks of LSCs. Their graphical representation has been adopted directly from MSCs, thus instance lines consist of an instance head with the instance name, the instance end as a black box, and an instance axis which is a vertical line connecting the head and the end. As in MSCs the horizontal dimension represents the structural dimension, while the vertical dimension corresponds to the time dimension. Instances are model objects and an instance of a modelled system is a data-space induced by variable declarations and events. Variables used in LSCs may be globally or locally declared in the modelled system. Events may be conditions, sending and reception of messages, or creation and destruction of instances.

Hot instance segments, a segment is a line segment between two events, along an instance line means that progress along the instance line is mandatory. Utilising this feature progress is forced down the instance, but as soon as the instance line reaches a cold segment, progress is no longer enforced. A cold segment means that the next event never needs to be reached.

Messages not originating from one of the objects modelled as an instance line in an LSC are said to come from the *environment*, which can be either non-modelled objects or an external stimuli. An instance line for 'some other stimuli' in the model is thus introduced. It is labelled *environment* and like normal instance lines it may communicate with the instances of the chart.

#### Limitations

The processes in UPPAAL models are created at model construction time and exist throughout a model's life-time, this means that explicit object construction and object destruction is not possible in a UPPAAL model, thus it will not be considered.

To limit the scope of the features to be implemented, the environment instance is disregarded. This means that if there is communication between an instance and an object not represented in the chart, the communication is ignored as only the interobject behaviour of the instances in the chart are of interest.

#### **Application**

When looking at a message trace, the temperatures of the segments do not matter. Even though there are some cold instance line segments the message trace must still exist, albeit it might never be completed in an actual model execution.

If the temperature of any snapshot is hot, progression is enforced for all instance lines in the given snapshot. In a universal chart this property can be tested with the *leads to* operator in TCTL, because if a snapshot is hot, then computation from the first snapshot must eventually progress to the second snapshot, i.e., the second snapshot must eventually be reached from the first.

Figure 3.3 illustrates temperatures of instance lines through a simple universal LSC with communication between two instances, and both hot and cold segments. First, the message sequence is tested, i.e., as described in Section 3.1.5 below. Second, the temperature of the segments can be used to generate properties for the chart.

In snapshot1 both inst1 and inst2 are hot, so msg1 has to be reached, and thereby snapshot2 also has to be reached. In snapshot2 only inst2 is hot, but it forces all other instances, i.e., inst1, to progress. In snapshot3 both instance line segments are cold, meaning that progression is not guaranteed. The possibility of progression must still exist, i.e., the message msg3 must still be possible to be

3.1 LSC constructs

The snapshots collect the temperatures of the segments in the snapshot. If a segment in the snapshot is hot, so is the snapshot, otherwise it is cold.

Figure 3.3: An LSC with hot and cold instance lines.

sent from inst2 to inst1, and this is checked via the message trace check.

#### 3.1.5 Messages

A message in an LSC is basically the same as a message in an MSC. Two kinds of messages are considered:

- Synchronous: The sender blocks until the receiver is ready to receive the

message. Sending and reception of the message happens simultaneously.

A horizontal arrow is used to denote a synchronous message. A delay from

trying to send a message to the acceptance of the request should be expressed

on the vertical axis as progress of time on the sender's side.

- Asynchronous: Time may pass between sending and reception of the message. After the message has been sent, progress may continue along the instance line before the message is received. An asynchronous message is graphically expressed with a slanted arrow.

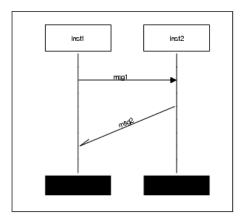

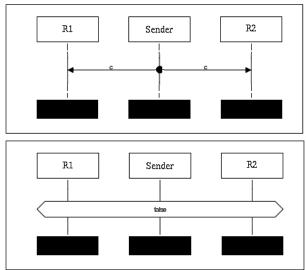

Figure 3.4 shows the graphical notation of messages.

Whether a message is synchronous or not is specified through its angle with the horizon. msg1 is synchronous, as it is parallel with the horizon, and msg2 is asynchronous as the message is slanted.

Figure 3.4: Synchronous and asynchronous messages in an LSC.

Interobject method calls are represented by two synchronous messages; the method call and the return message, and the two messages are paired by widening the instance lines carrying the method body. A hot message is a message that, when sent, must be received, and a cold message means that after the message is sent, it is not required to be received.

#### Limitations

There are two categories of messages in UPPAAL models; binary and broadcast, both categories are synchronous, i.e., sending and reception is instantaneous, thus asynchronous messages in LSCs are discarded.

The binary messages in a UPPAAL model are handshakes, which means that there are always a sender and a receiver. Broadcast messages on the other hand do not need to have a receiver. This means that binary messages in the supported LSC features must be hot, i.e., if a message is sent it must be received. It also means that it is possible to have cold messages, but then the message must be a broadcast and it must be specified in a simultaneous region, whereas a single hot broadcast message needs not be specified in a simultaneous region. See description of simultaneous regions in Section 3.2.3.

Automata in UPPAAL cannot send messages to themselves, thus such messages are not included. If they were, it would be to describe internal action steps, but if

3.1 LSC constructs

these steps were to be included in a specification it would end up being a complete description of an automata trace too detailed for a requirement specification.

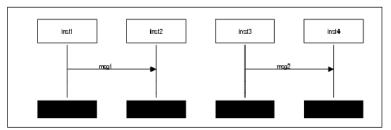

In LSCs it is possible to have two messages at the same level that are not sent from the same simultaneous region. An example of this can be seen in Figure 3.5, where msg1 and msg2 are exchanged simultaneously.

Specifying simultaneity by two messages at the same time like this is disallowed. Any simultaneity must be specified through simultaneous regions.

Figure 3.5: Two messages exchanged at the same time.

UPPAAL supports sending of binary messages simultaneously using urgent locations, but because the computation graph does not contain clocks this cannot be tested. Thus, messages at the same vertical level is not supported, unless they are in a simultaneous region.

#### **Application**

When testing UPPAAL models using TCTL it is not possible to test whether a sequence of messages occurs in a trace, because there are no constructs in TCTL referring to messages. The main focus of TCTL is automata locations and variable values in locations, in other words configurations in UPPAAL models.

To test message sequences the messages are extracted from the LSC and the computation graph is traversed to prove whether the sequence exists.

If a broadcast message only has one receiver in the chart it may be specified by a hot message, but if the message has several receivers each receiver must be specified using a simultaneous region sending the same messages to all receivers, Hot messages are used when the receiver must receive it, and cold messages are interpreted as a broadcast that may be received. A broadcast message is always sent to all objects, but if a message is not specified in the LSC from a simultaneous region to an instance, then the broadcast message may not be received by that instance.

#### 3.1.6 Conditions

Conditions may terminate a chart successfully or unsuccessfully depending of their temperature. A hot condition must be satisfied or the run is terminated unsuccessfully. A cold condition does not have to be satisfied, if it does not hold it simply means that the rest of the chart is disregarded, which is considered a successful termination of the chart.

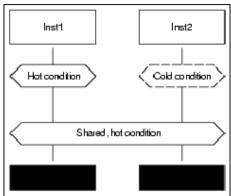

Graphically, a hot condition is depicted as a solid hexagon, and a cold condition is a hexagon with a dashed line, as seen in Figure 3.6. A condition can span more than one instance meaning that the condition is specified to hold for all spanned instances. Such a *shared condition* may be used to synchronise instances because the condition will not be evaluated before all instances have reached the condition, and no instance will progress beyond the condition before it has been evaluated. The rules for hot and cold conditions apply to a shared condition in the same way as they do for normal conditions.

Hot conditions are given as solid hexagons and cold conditions are given as dashed hexagons. Conditions may be shared over several instance lines.

Figure 3.6: The types of conditions in LSCs.

A useful feature of conditions is the ability to construct forbidden scenarios. A prechart with the forbidden scenario may be combined with a universal chart containing just a single hot condition always evaluating to *false* [Bjø04].

#### Limitations

It is possible in LSCs to attach a condition to a simultaneous region and it is possible to have an isolated condition. Klose recommends always attaching a condition

3.1 LSC constructs 35

to a simultaneous region because that gives a definite evaluation point for the condition [Klo03][pp. 118-123]. We choose to not differentiate between a condition attached to a simultaneous region and an isolated condition. A condition is to hold for a snapshot and should be evaluated for all possible UPPAAL configurations in that snapshot. As an isolated condition is intuitively closer to our definition of conditions, only isolated conditions are allowed.

#### **Application**

As with activation conditions, conditions appearing within a chart are boolean expressions over UPPAAL variables and automata locations.

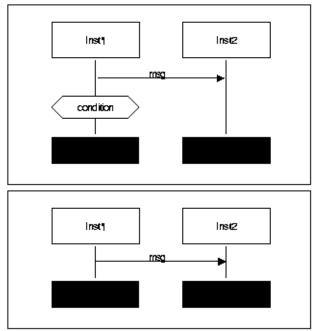

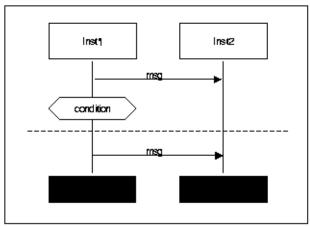

Conditions are expressed as local TCTL properties and the UPPAAL verification engine is used for querying these properties. Each condition on an instance line in a universal chart is checked with a TCTL formula with the following form for each configuration in the snapshot:

A[] configuration imply condition

If the chart is existential, the formula is:

E <> configuration and condition

Shared conditions are conditions that span more than one instance line. A shared condition is a snapshot is the same as a single condition on all instances, thus a shared condition in an LSC is translated into single conditions.

If a hot condition evaluates to *false* the chart is terminated unsuccessfully, i.e., the chart does not hold. If a cold condition evaluates to *false* the LSC verification engine must ignore the rest of the chart, but otherwise report that the chart is satisfied.

#### 3.1.7 Subcharts

A chart may include another chart, which is specified over a set of instances that may or may not be present in the parent chart. Subcharts may include itself, allowing infinite iteration and thus an infinite number of elements to be verified. Subcharts introduce chart scope, which means that cold conditions not satisfied only

exit the subchart and not the parent chart. Combining subcharts and cold conditions yields classical if-then constructs and loop structures such as while-do and repeatuntil. If-then constructs are simply subcharts beginning with cold conditions, and the loop structures are based on subchart iterations.

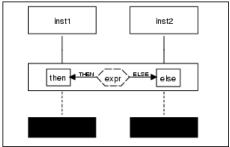

#### Limitation

As the LSC editor used in this project does not support subcharts in this form, they are not used. The LSCEditor supports an if-then-else construct, and as subcharts can be seen as a special instance of the if-then-else, excluding subcharts as a construct poses no problem. The if-then-else construct is described below.

# 3.1.8 Coregions

A coregion is used to indicate that partial ordering is imposed on the events contained in the region as opposed to the total ordering present outside of a coregion. A coregion is graphically represented as a vertical dotted line next to the instance axis as in Figure 3.7.

The coregion, which is given by a dashed vertical line, induces partial order on inst1, but because the messages are synchronous, the order is still preserved.

Figure 3.7: An LSC with a coregion.

Coregions in [DH01] also act as simultaneous regions, but [Kl003] uses an explicit construct for simultaneous regions, and thus limits coregions. Because the LSCEditor uses the representation of an explicit simultaneous region this representation is adopted.

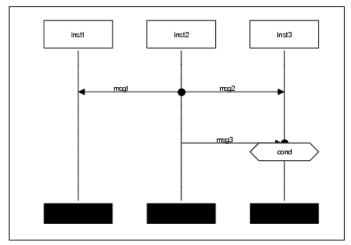

#### Limitations

Coregions introduce partial order on a section of an instance line. As only synchronous messages are supported in the LSC subset, a coregion with partial order would be overridden if the other instance lines involved in the message passing in the coregion are not declared as coregions, like in Scenario1 of Figure 3.8. If a message is sent, it will be received at the same time. Therefore, a coregion declaration on an instance line will count as a global coregion for all instance lines. This means that Scenario1 of Figure 3.8 will be interpreted as Scenario2.

The interpretation of coregions is that coregions induces no order on messages for all instance lines. A specification like the one in Scenariol is thus interpreted as the specification of Scenario2.

Figure 3.8: How coregions are interpreted.