# The Art of General-Purpose Computations on Graphics Processing Units

BrookGPU CUDA OpenCL

10th of January 2011 9th semester of Software Engineering Aalborg University

Søren Alsbjerg Hørup Søren Andreas Juul Henrik Holtegaard Larsen

#### Title:

The Art of GPGPU

#### Project period:

September 2<sup>nd</sup>, 2010 to January 10<sup>th</sup>, 2011

#### Theme:

GPGPU Programming

#### Group:

d509aSoftware Engineering

#### Authors:

Søren Alsbjerg Hørup Søren Andreas Juul Henrik Holtegaard Larsen

#### Supervisor:

Lone Leth Thomsen

Copies: 6

Total pages: 117

Appendices: 1

Project finished: 10th of January 2011

Aalborg University **Department of Computer Science** Selma Lagerlöfs Vej 300 9220 Aalborg Telephone: (45)99409940 http://www.cs.aau.dk

#### Abstract:

In this report we document our analysis of General-Purpose computations on Graphics Processing Units (GPGPU) and the practical experience that we have gained throughout the process.

In the analysis chapter, we analyze the differences between GPUs and CPUs describe the architecture of the G80 chip, which is the chip on the Tesla cards available to us. Also we take an in-depth look at three GPGPU programming languages, CUDA, OpenCL and BrookGPU, where OpenCL and CUDA is supported by the the Tesla card, and we find several tools that can help with OpenCL and CUDA development.

In the development chapter, we implement two GPGPU powered applications, namely a ray tracer using CUDA and the Boids flocking algorithm using OpenCL and Brook+. Benchmarks are carried out, which are analyzed and discussed. We find that the GPU is indeed a powerful co-processor, but one must be able to program it correctly against several factors to obtain high performance.

Lastly, we compare the three GPGPU languages, that we found through the analysis, using a number of comparison criteria. Through the comparison we find that CUDA is the most expressive of the three, and is also the must mature, while OpenCL is quickly gaining popularity in the GPGPU field.

The content of this report is freely available, but publication is only permitted with explicit permission from the authors.

#### Preface

#### Style Guide

The following style is used throughout this report:

Citations are represented as a pair of angle-brackets containing a number. The number refers to a number in our bibliography. Used as this section is based on [1] means that the entire section is based on the mentioned source, unless other sources are explicitly stated.

A citation at the end of a sentence, but right before the full stop, means that the citation is used exactly for that sentence. A citation after a full stop means that the citation is applied to the whole paragraph, i.e. more than one sentence.

Citing a specific page, section and chapter, is done with "p.", "sec." and "chap." respectively, e.g. [1, p. 55], [1, chap. 2], etc.

#### Prerequisites

The intended readers of this report are students who have passed Software Engineering  $8^{\rm th}$  semester or equivalent. A basic understanding of the C/C++ language is recommended, as many of the APIs discussed are written in C/C++ or a subset of it.

#### Terms

The following list introduces the most important terms used throughout this report.

**GPU** refers to Graphics Processing Unit, a specialized microprocessor that accelerates graphics computations.

**Concurrency** refers to computations done simultaneously, but can be interleaved.

Parallel refers to computations that are done simultaneously and in parallel.

**Graphics card** refers to a device which has a Graphics Processing Unit (GPU), memory and a host interface.

**Discrete card** refers to a graphics card which is not integrated into a system, but must be installed into an expansion slot, e.g. PCI, PCI-E, etc.

**GPGPU** refers to General-Purpose Computing on Graphics Processing Units, i.e. utilizing graphics cards for non-graphical computations.

**Device** refers to the graphics card containing the GPU.

**Device code** refers to code which is executed on a device.

**Host** refers to the host system containing the Central Processing Unit (CPU) and main memory.

Host code refers to code which is executed on the host.

Interactive framerates refers to the number of frames per second required by an application, while still being interactive, i.e. handle input from the users. We define this as at least 30 frames per second.

**Rendering** refers to the process of creating a 2D image from a 3D scene that can be displayed.

#### **Enclosed CD**

On the enclosed CD the source code developed during this project is available along with the benchmark results and this report in PDF format.

#### **Thanks**

We want to give thanks to our supervisor Lone Leth Thomsen, for guiding and helping us throughout this project. We would also like to thank Bent Thomsen for setting up the meeting with ConfiCore, Kim Guldstrand Larsen for giving us suggestions to our problem formulation, and Aage Sørensen who helped us acquire the needed hardware.

## Signatures

| SprenHond                | Scren Jul          |

|--------------------------|--------------------|

| Søren Alsbjerg Hørup     | Søren Andreas Juul |

| Herrit V. Loren          |                    |

| Henrik Holtegaard Larsen |                    |

# Contents

| T | ıntr | duction                                                  | L |

|---|------|----------------------------------------------------------|---|

|   | 1.1  | Motivation                                               | 1 |

|   |      | 1.1.1 Other Utilization of GPGPU                         | 2 |

|   | 1.2  | Problem Formulation                                      | 4 |

|   |      | 1.2.1 Practical Experience                               | 5 |

|   |      | 1.2.2 Be Scientific                                      | 5 |

| 2 | Ana  | lysis                                                    | 6 |

|   | 2.1  | What Is a GPU                                            | 6 |

|   | 2.2  | Available Hardware                                       | 8 |

|   |      | 2.2.1 Problems with Tesla C870                           | 8 |

|   | 2.3  | G80 Architecture                                         | 9 |

|   |      | 2.3.1 Overview                                           | 9 |

|   |      | 2.3.2 Memory                                             | 1 |

|   |      | 2.3.3 Summary                                            | 2 |

|   | 2.4  | Algorithms Suited for GPGPU Execution                    | 2 |

|   |      | 2.4.1 Comparison of Performance between GPUs and CPUs 13 | 3 |

|   |      | 2.4.1.1 Discussion                                       | 5 |

|   |      | 2.4.1.2 Our Remarks                                      | 6 |

|   | 2.5  | Programming GPUs for General Purposes                    | 6 |

|   |      | $2.5.1  \text{Stream Processing}  \dots  \dots  1$       | 7 |

|   | 2.6  | GPU Languages                                            | 3 |

|   |      | 2.6.1 BrookGPU                                           | 8 |

|   |      | 2.6.1.1 ATI's Brook+                                     | 9 |

|   |      | 2.6.1.2 Example                                          | O |

|   |      | 2.6.2 CUDA                                               | O |

|   |      | 2.6.2.1 Architecture                                     | 1 |

|   |      | 2.6.2.2 Memory                                           | 1 |

|   |      | 2.6.2.3 Example                                          | 2 |

|   |      | 2.6.2.4 Compute Capability                               | 4 |

|   |      | 2.6.3 OpenCL                                             | õ |

|   |      |                                                          |   |

|   |     |                        | 2.6.3.1 Architecture                                                                                                            |

|---|-----|------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|   |     |                        | 2.6.3.2 Framework                                                                                                               |

|   |     |                        | 2.6.3.3 Example                                                                                                                 |

|   |     | 2.6.4                  | Summary                                                                                                                         |

|   | 2.7 | Tool S                 | upport                                                                                                                          |

|   |     | 2.7.1                  | CUDA-GDB                                                                                                                        |

|   |     | 2.7.2                  | Nvidia Parallel Nsight                                                                                                          |

|   |     | 2.7.3                  | Nvidia Compute Visual Profiler                                                                                                  |

|   |     | 2.7.4                  | gDEBugger CL                                                                                                                    |

|   |     | 2.7.5                  | CUDA Occupancy Calculator                                                                                                       |

|   |     | 2.7.6                  | Conclusion                                                                                                                      |

|   | 2.8 | Summ                   |                                                                                                                                 |

|   |     |                        |                                                                                                                                 |

| 3 | Dev | elopm                  | ent 35                                                                                                                          |

|   | 3.1 | $\operatorname{Boids}$ | $Application \dots \dots$ |

|   |     | 3.1.1                  | The Boids Model                                                                                                                 |

|   |     |                        | 3.1.1.1 Steering                                                                                                                |

|   |     |                        | 3.1.1.2 Heading                                                                                                                 |

|   |     |                        | 3.1.1.3 Position                                                                                                                |

|   |     | 3.1.2                  | Optimizations                                                                                                                   |

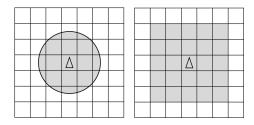

|   |     |                        | 3.1.2.1 Sorting                                                                                                                 |

|   |     |                        | 3.1.2.2 Finding neighbors                                                                                                       |

|   |     |                        | 3.1.2.3 Choice of optimization                                                                                                  |

|   |     | 3.1.3                  | Functional Requirements                                                                                                         |

|   |     | 3.1.4                  | OpenCL Implementation                                                                                                           |

|   |     |                        | 3.1.4.1 Sort                                                                                                                    |

|   |     |                        | 3.1.4.2 BoidsSimple                                                                                                             |

|   |     |                        | 3.1.4.3 Boids                                                                                                                   |

|   |     | 3.1.5                  | Brook+ Implementation                                                                                                           |

|   |     |                        | 3.1.5.1 Sort                                                                                                                    |

|   |     |                        | 3.1.5.2 BoidsSimple                                                                                                             |

|   |     |                        | 3.1.5.3 Boids                                                                                                                   |

|   |     | 3.1.6                  | C++ CPU Implementation                                                                                                          |

|   |     |                        | 3.1.6.1 Sort                                                                                                                    |

|   |     |                        | 3.1.6.2 BoidsSimple                                                                                                             |

|   |     |                        | 3.1.6.3 Boids                                                                                                                   |

|   |     | 3.1.7                  | Summary                                                                                                                         |

|   | 3.2 | Ray T                  | racer Application                                                                                                               |

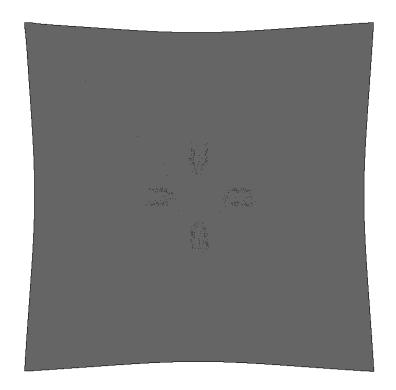

|   |     | 3.2.1                  | Ray Tracing Algorithm                                                                                                           |

|   |     | 3.2.2                  | Functional Requirements                                                                                                         |

|   |     | 3.2.3                  | CUDA Implementation                                                                                                             |

|   |     |                        | 3.2.3.1 Work Partitioning (R+P)                                                                                                 |

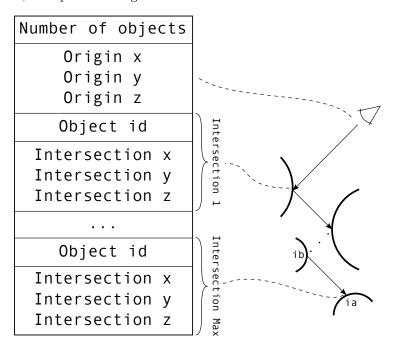

|   |     |                        | 3.2.3.2 Intersection Buffer (R)                                                                                                 |

|   |     |                        | 3.2.3.3 Memory (P)                                                                                                              |

|   |     | 3.2.4                  | C++ Implementation                                                                                                              |

|   |     | 3.2.5                  | Summary                                                                                                                         |

|   | 3.3 |                        | ary                                                                                                                             |

|   | -   |                        |                                                                                                                                 |

| 4 | Ben | chmar                  | ks         |              |    |  |  |  |  |  |  |  | 54   |

|---|-----|------------------------|------------|--------------|----|--|--|--|--|--|--|--|------|

|   | 4.1 | $\operatorname{Boids}$ | Benchmar   | ks           |    |  |  |  |  |  |  |  | . 54 |

|   |     | 4.1.1                  | Benchma    | rk Setup .   |    |  |  |  |  |  |  |  |      |

|   |     | 4.1.2                  |            | periments    |    |  |  |  |  |  |  |  |      |

|   |     |                        |            | Results .    |    |  |  |  |  |  |  |  |      |

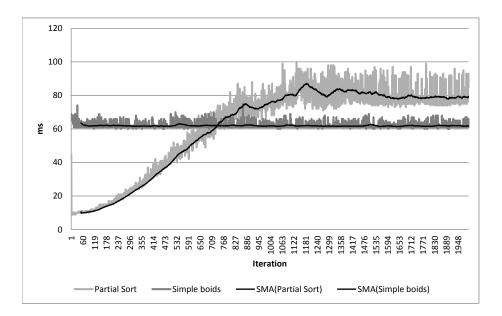

|   |     | 4.1.3                  |            | rk Results   |    |  |  |  |  |  |  |  |      |

|   |     | 4.1.4                  |            | n            |    |  |  |  |  |  |  |  |      |

|   | 4.2 |                        |            | hmarks .     |    |  |  |  |  |  |  |  |      |

|   |     | 4.2.1                  |            | rk Setup .   |    |  |  |  |  |  |  |  |      |

|   |     | 4.2.2                  |            | rk Results   |    |  |  |  |  |  |  |  |      |

|   |     | 4.2.3                  |            | n            |    |  |  |  |  |  |  |  |      |

|   |     |                        |            |              |    |  |  |  |  |  |  |  |      |

| 5 | Cor | npariso                | on         |              |    |  |  |  |  |  |  |  | 66   |

|   | 5.1 | Criteri                | ia for Com | parison .    |    |  |  |  |  |  |  |  | . 66 |

|   |     | 5.1.1                  | Memory     |              |    |  |  |  |  |  |  |  | . 67 |

|   |     | 5.1.2                  | Computa    | $tion \dots$ |    |  |  |  |  |  |  |  | . 67 |

|   |     | 5.1.3                  | Learnabil  | lity         |    |  |  |  |  |  |  |  | . 68 |

|   |     | 5.1.4                  | Concurre   | ncy          |    |  |  |  |  |  |  |  | . 68 |

|   |     | 5.1.5                  |            |              |    |  |  |  |  |  |  |  |      |

|   | 5.2 | Rating                 | gs         |              |    |  |  |  |  |  |  |  | . 70 |

|   |     | 5.2.1                  | Memory     |              |    |  |  |  |  |  |  |  | . 70 |

|   |     |                        | 5.2.1.1    | BrookGPU     | J. |  |  |  |  |  |  |  | . 70 |

|   |     |                        | 5.2.1.2    | CUDA .       |    |  |  |  |  |  |  |  | . 71 |

|   |     |                        | 5.2.1.3    | OpenCL       |    |  |  |  |  |  |  |  | . 71 |

|   |     | 5.2.2                  |            | tions        |    |  |  |  |  |  |  |  |      |

|   |     |                        | 5.2.2.1    | BrookGPU     | J. |  |  |  |  |  |  |  | . 72 |

|   |     |                        |            |              |    |  |  |  |  |  |  |  |      |

|   |     |                        | 5.2.2.3    | OpenCL       |    |  |  |  |  |  |  |  | . 73 |

|   |     | 5.2.3                  | Learnabil  | ity          |    |  |  |  |  |  |  |  | . 73 |

|   |     |                        | 5.2.3.1    | BrookGPU     | J. |  |  |  |  |  |  |  | . 73 |

|   |     |                        | 5.2.3.2    | CUDA .       |    |  |  |  |  |  |  |  | . 74 |

|   |     |                        | 5.2.3.3    | OpenCL       |    |  |  |  |  |  |  |  | . 75 |

|   |     | 5.2.4                  | Concurre   | ncy          |    |  |  |  |  |  |  |  | . 76 |

|   |     |                        | 5.2.4.1    | BrookGPU     | J. |  |  |  |  |  |  |  | . 76 |

|   |     |                        | 5.2.4.2    | CUDA .       |    |  |  |  |  |  |  |  | . 77 |

|   |     |                        | 5.2.4.3    | OpenCL       |    |  |  |  |  |  |  |  | . 78 |

|   |     | 5.2.5                  | Support    |              |    |  |  |  |  |  |  |  | . 78 |

|   |     |                        | 5.2.5.1    | BrookGPU     | J. |  |  |  |  |  |  |  | . 79 |

|   |     |                        | 5.2.5.2    | CUDA .       |    |  |  |  |  |  |  |  | . 79 |

|   |     |                        | 5.2.5.3    | OpenCL       |    |  |  |  |  |  |  |  | . 80 |

|   | 5.3 | Summ                   | ary        |              |    |  |  |  |  |  |  |  | . 81 |

|   |     |                        |            |              |    |  |  |  |  |  |  |  |      |

| 6 | Epi | logue                  |            |              |    |  |  |  |  |  |  |  | 85   |

|   | 6.1 | Conclu                 |            |              |    |  |  |  |  |  |  |  |      |

|   |     | 6.1.1                  |            | Formulation  |    |  |  |  |  |  |  |  |      |

|   |     | 6.1.2                  |            | experience   |    |  |  |  |  |  |  |  |      |

|   | 6.2 |                        |            |              |    |  |  |  |  |  |  |  |      |

|   |     | 6.2.1                  | -          | ntation Ver  |    |  |  |  |  |  |  |  |      |

|   |     | 6.2.2                  |            | rks          |    |  |  |  |  |  |  |  |      |

|   |     | 6.2.3                  | Be Scient  | ific         |    |  |  |  |  |  |  |  | . 90 |

|    |       | 6.2.4                          | Our Thoughts                                                                                                                       |

|----|-------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|    | 6.3   | Future                         | e Trends                                                                                                                           |

|    |       | 6.3.1                          | GPGPU Programming is Becoming More Powerful 91                                                                                     |

|    |       | 6.3.2                          | GPGPU Programming is Becoming Easier 91                                                                                            |

|    |       | 6.3.3                          | GPU and CPUs are merging                                                                                                           |

|    |       | 6.3.4                          | GPGPU is Gaining Momentum                                                                                                          |

|    |       | 6.3.5                          | Summary                                                                                                                            |

|    | 6.4   | $\operatorname{Futur}\epsilon$ | e Development                                                                                                                      |

| Bi | bliog | raphy                          | 101                                                                                                                                |

| A  | Nvi   | dia G8                         | 102                                                                                                                                |

|    | A.1   | Comp                           | onents Details $\dots \dots \dots$ |

|    | A.2   | Memo                           | ry                                                                                                                                 |

#### Introduction

A GPU is a specialized microprocessor that accelerates graphics rendering, thus allowing interactive graphic-intensive applications on consumer-level computers, which would otherwise require a high performance and much more expensive CPU. [79]

Previous generations of GPUs, prior to 2000, used a fixed-function pipeline, meaning that the functionality of a GPU was fixed and one could only effect the behavior of the pipeline trough parameters, e.g. one could affect how vertices are transformed by specifying a transformation matrix. [79, sec. 1.1.3][36, p. 96]

In the start of the 2000s, GPU manufacturers introduced programmable aspects to the GPU pipeline. This allowed more advanced graphical effects, such as bump-mapping, because developers were able to introduce small programs to the graphical pipeline, called "shaders", which could alter the results of the graphical computations. In 2002 the first GPUs that supported features such as, loops, branches, variables and floating point mathematics in pixel shaders were introduced, thus making GPUs more flexible and more like CPUs. [79, sec. 1.1.4][36, p. 98]

GPUs have continued to increase in flexibility and todays GPUs even allow general purpose computations, other than graphical computations, on the GPU. This is commonly referred to as General-purpose computing on graphics processing units (GPGPU) or, and to a lesser degree, GPU Computing. [20]

Examples of GPGPU applications include: neural network that utilizes the GPU to calculate the product of the neurons, computer vision algorithms that utilizes the GPU to sample and analyze each separate pixel in real time, Fast Fourier Transform algorithms which is commonly used in encodings and decodings of audio and video, and many more. [36, p. 99]

#### 1.1 Motivation

Our primary reason for looking at GPGPU programming is that we implemented a ray tracer for smartphones and CPUs as a part of our 8<sup>th</sup> semester project. Ray tracing, however, turned out to be a slow process using only the CPU. We have since seen several publications where different types of computations have

been accelerated using GPUs, we want to investigate whether we can create a faster ray tracer using GPUs. Another advantage of using a GPU over a CPU is that we might be capable of achieving comparable levels of performance using a cheaper systems with GPUs than CPUs.

Performance vs Cost With regards to performance vs cost, we look at the FLoating point Operations Per Second (FLOPS) since the computations made in ray tracing is primary done on floating points. When looking at state of the art consumer level graphics cards and CPUs, we see that a Radeon HD 5970 graphics card with two ATI Cypress GPUs gives a theoretical peak double-precision floating-point performance of 925 gigaFLOPS, while an Intel Core i7 980 XE CPU has a max theoretical performance of 107.55 gigaFLOPS. Thus, the HD 5970 has nearly 10 times the computational power. [76]

According to EDBPriser.dk at the time of writing, the HD 5970 costs 3985kr (about 200 megaFLOPS/kr) compared to the 980 XE's price of 6860 kr (about 15 megaFLOPS/kr), making the CPU roughly 13 times more expensive with regards to double precision cost efficiency. Of course, theoretical performance should be taken with a grain of salt, since the actual performance also depends upon the implemented algorithm, e.g. algorithms requiring heavy synchronization may be bounded by memory access latency and not FLOPS.

8<sup>th</sup> Semester's ray tracer Implementation During the 8<sup>th</sup> semester we implemented a ray tracer [27], running on the CPU, and discovered that the rendering process required a lot of computational resources. We had an hypothesis that the rendering process could be carried out much faster using a GPU, instead of a CPU, because of the theoretical higher processing power of GPUs.

Looking at the literature with regards to GPGPU and ray tracing we see that several publications deal with the problem of creating an efficient GPU based ray tracer [17][63][62]; many of which are successful in achieving high frame rates on consumer level GPUs. Creating an implementation that is accelerated by a GPU requires a lot of work, and the implementation would not be compatible with the smartphone that we had access to at the time, thus requiring us to make two separate code bases which was outside the scope of the 8<sup>th</sup> semester project; we therefore want to investigate the potential of using GPGPU for ray tracing in this project.

#### 1.1.1 Other Utilization of GPGPU

Looking beyond ray tracing on GPU hardware, we see that other algorithms have been implemented with GPU support with considerable increase in execution speed.

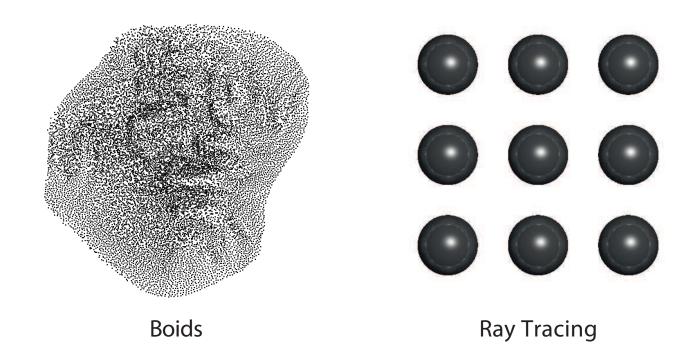

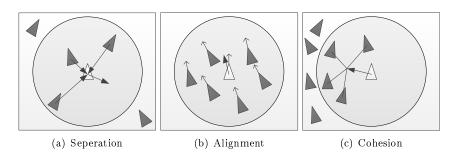

**Crowd Simulation** Crowd simulation is the process of simulating a larger group of actors, such as humans, animals, particles, etc. and their interaction, which leads to a form of collective behavior [75]. *Boids* is an algorithm that allows crowd simulation with regards to how animals exhibit flocking behavior [67], specifically, the Boids algorithm deals with the simulation of a herd of land

animals, a flock of birds or a school of fish; these behaviors are all captured within the Boids algorithm.

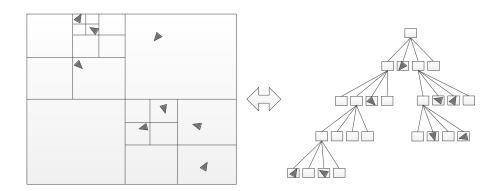

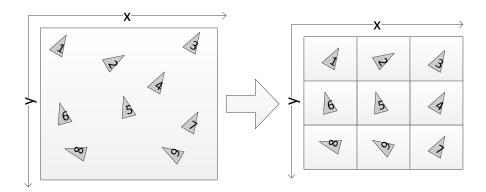

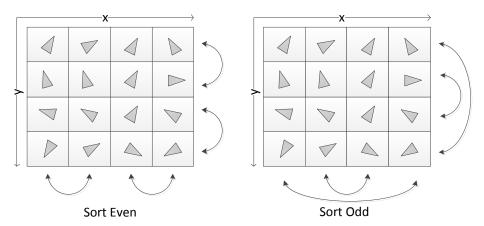

Several parallel CPU implementations of the Boids algorithm exist, such as [11] for multi-core CPUs and [72] for clusters, but some publications have also introduced GPU implementations of the Boids algorithm. [64] is one such publication, where each actor is stored in a two-dimensional data structure, that is partially sorted at each iteration, thereby allowing efficient spatial queries. Two implementations of the algorithm, one targeting the CPU and the other targeting the GPU, is evaluated. The CPU and GPU version is able to simulate one iteration of one million actors in 5394ms and 38ms respectively, on a Core 2 Quad 2.4GHz equipped with a Nvidia 8800 GTS graphics card. Thus, the GPU version is about 140 times faster than the CPU version.

Computer Vision Computer vision in science is the discipline concerned with the theory behind artificial systems that have the ability to extract information from images, such as photographs, video, scanners, etc. thus allowing computers to "see". [6, p xiii]

Several publications deal with computer vision. One such publication [1] from 2008, describes an open-source computer vision and image processing library for GPUs, called GpuCV. GpuCV was designed to be compatible with existing applications that utilizes OpenCV, a CPU based computer vision library, thus allowing transparent utilization of the GPU for existing OpenCV applications.

Benchmarking is done on a Intel Core2 Duo 2.13 Ghz CPU with 2GB of Random Access Memory (RAM) and a 1GB Nvidia GeForce GTX280 graphics card, the images used as input, ranging from 128x128 to 2048x2048 pixels in size. The results show that GPU support is beneficial when high resolution images are used as input, however, at lower resolutions the CPU is in most cases more efficient. At high resolutions however, GpuCV achieves speed ups in the range of 30 to 100 times that of the OpenCV implementation.

**Sorting** The problem of sorting has also been solved using GPUs, though with smaller factor speed ups compared to the applications presented above.

A publication [68] from 2008 suggests a hybrid sorting algorithm based upon quick-sort and merge-sort. Quick-sort is first used to divide the input list, that requires sorting, into L number of sublists, where all elements of sublist i+1 are higher than the elements of i. L is the number of stream processors on the GPU, 128 for a GeForce 8800 GTS. Afterwards, a modified version of merge-sort is used to sort the L sublists.

This approach achieves nearly twice as fast sorting compared to other GPU sorting algorithms and is over 6 times faster than the Standard Template Library (STL) quick sort CPU implementation provided by Microsoft. Also, when utilizing two GPUs, sorting is 11 times faster compared to STL sort. Benchmarking was carried out using an Intel Core 2 Duo 2.66GHz and two GeForce 8800 GTS 512MB graphics cards. [68, sec. 7.1]

#### 1.2 Problem Formulation

The aim of this semesters project is to gain a deeper understanding of GPGPU related theories and practices, which allows us to implement applications which can utilize the GPU for computational intensive operations. We have devised a problem formulation, presented below.

Our main problem is:

Learn the art of performing General-Purpose Computing on Graphics Processing Units, and the theories that relate to this subject

From the main problem we have derived the following questions we want to answer in this project:

• How does the hardware architecture of a GPU look like, compared to a CPU?

In order to efficiently utilize the GPUs, knowledge of the hardware architecture might be required

- We have two Tesla C870 graphics cards available, as is described in Section 2.2. What does the hardware architecture of a Tesla C870 look like?

- What are the characteristics of well suited problems for GPU execution?

Not all problems, or parts thereof, may be suited for GPU execution. We wish to identify which type of problems are suited, and which are not

- What are GPUs currently used for other than graphical applications?

- What are the pros and cons of GPUs compared to CPUs?

# $\bullet$ Which GPGPU APIs/Languages exist, and how does one use them?

To better understand how GPGPU programming is done, it is wise to look at the tools of the trade

- What are the pros and cons of the different APIs/Languages?

- Do any of the languages support high level of abstractions, i.e. are any of the languages high level programming languages?

- How can a valid comparison of the different languages be carried out?

#### Which tools currently exist to help developers with GPGPU programming?

Tools, such as debugging tools, may make the developer more efficient at implementing programs that make use of GPGPU

- Which debugging tools are available?

- Which testing tools are available, e.g. Unit testing?

- What about profiling tools?

- Is it possible to utilizing multiple GPUs in parallel for GPGPU purposes? using technologies such as SLI and CrossFire Using several GPUs in parallel may increase performance, as more work can be done in parallel

- Which problems arise when using multiple GPUs?

#### 1.2.1 Practical Experience

Furthermore we wish to gain practical experiences with GPGPU by implementing a ray tracer and the Boids algorithm on a GPU. The purpose of choosing two algorithms is to cover a broader area of problems. The Boids implementation will focus on how to implement data structures and the problems this may impose.

The ray tracer implementation will use a naive algorithm and instead focus on improving this algorithm by using the theories from the analysis, e.g. which types of memory should be used where.

#### 1.2.2 Be Scientific

We must be scientific in our approach, which means that we must be able to reason about our choices, e.g. of a specific algorithm. Also, the sources we cite must be scientific publications, i.e. peer reviewed published papers, or atleast some form of recognized documentation, such as an official specification or company website for a particular product.

## **Analysis**

In this chapter, we will first cover what a GPU is and how it differs from a CPU, and then look at the GPU hardware we have available and how we got it working. Afterwards, we will analyze the G80 architecture, which is the architecture used by the Tesla C870 GPU, and look at which problems can be solved using GPUs. Lastly, we will look at which programming languages programmers can use to program GPGPUs, and which GPGPU tools are currently available.

#### 2.1 What Is a GPU

GPUs were originally designed for graphics computations and then started changing to allow more and more general types of computations, they have a very different designs than CPUs. In order to develop a program that can run efficiently on a GPU, we have to understand these differences.

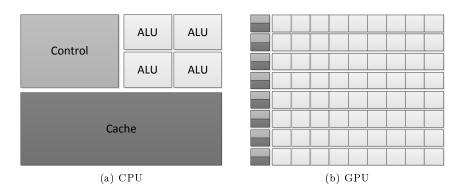

The main difference between a CPU and a GPU is that a CPU has a few faster cores, while the GPU has many slower cores.

"If you were plowing a field, which would you rather use?... Two strong oxen or 1024 chickens?" [13]

The reason for CPUs having few but faster cores and GPUs have many slower cores is that they have different goals. The CPU focuses on low latency, i.e. making a single instruction execute as fast as possible. The GPU on the other hand focuses on delivering as high throughput as possible, i.e. the time it takes to complete a single instruction is less important than the time it takes to complete all the instructions of a given task.

The difference can be illustrated by an example of the addition of two vectors each containing 2000 elements. Assuming that we have a CPU that can execute an add instruction in 1ms completing the task would take  $1\times 2000=2000$  ms. On the other hand we might have a GPU that takes 100ms to execute one add instruction, but can execute 200 add instructions in parallel thereby only taking  $\frac{2000}{200}\times 100=1000$  ms to complete the task.

This has led CPU architects to keep the CPU's Arithmetic Logic Unit (ALU) busy by using large caches, using prefetching to minimize the latency of memory

Figure 2.1: Difference between a CPU and a GPU [31]

access, and use complicated control logic such as branch prediction and out of order execution, thus taking advantage of cycles which would otherwise have been wasted due to memory access latency. All of this cache and control logic takes up a relatively large portion of the chip, compared to the space taken by the ALUs. This is shown on Figure 2.1(a).

On the other hand, GPUs are designed as a very parallel architecture with many simple cores, containing very simple control logic and small caches. GPUs also uses Single Instruction, Multiple Data (SIMD) to share a single control unit between multiple ALU [41] as shown in Figure 2.1(b). The use of SIMD means that more ALUs can be fitted on to a chip, but this also means that branching becomes slow. The reason branching becomes slow is that a single control unit can only follow one branch at a time. All ALUs not taking a given branch must wait for the ALU, which took the branch, to exit the branch before executing their own branch. Thus, if we have 8 ALUs per control unit, we have a worst case performance of  $1/8^{\rm th}$  the performance of a program without any branches.

To keep the ALU busy during memory access without the use of advanced control and large caches, the GPU instead rely on latency hiding, that is, having many lightweight threads ready to execute, such that the GPU can start running one of these when another thread is waiting for memory access.

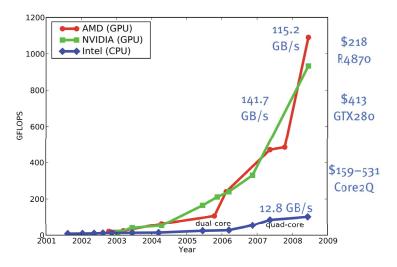

These two design philosophies have led to a big difference in the theoretical peak performance of GPU and CPU. The performance is usually measured in FLOPS, as shown in Figure 2.2. The GPU has about a 10 times more compute power than a CPU and the difference appears to be growing. In recent years, CPU has hit a limit in the increase in sequential execution speed due to power consumption [71]. This has led CPU designers from the uni-processor design to multi-core design, i.e. multiple cores per die, which in turn means that the processing power of CPUs increases every year due to more cores, and not due to increased clock-frequency.

GPUs usually comes on a discrete card with its own RAM. Therefore, it is much easier for hardware manufactures to move to new RAM technologies or make a wider memory busses since it does not have to remain backward compatible with old hardware [31]. This means that GPUs usually have a much higher memory bandwidth than the CPUs. As shown in Figure 2.2, a GPU can have access to RAM that has above 10 times the bandwidth of the RAM that a CPU has access to.

Figure 2.2: Performance comparison of GPU and CPU [31][61]

#### 2.2 Available Hardware

We have a workstation with two Nvidia C870 Tesla cards at our disposal. These cards support Compute Unified Device Architecture (CUDA) of compute capability 1.0, which is the first version of CUDA released, and have a theoretical performance of 518.4 gigaFLOPS with a memory bandwidth of 76.8 GB/sec. Compute capability version defines which CUDA features are supported, e.g. compute capability 1.1 introduces atomic operations on integers in global memory. The compute capability depends on the GPU architecture and can be seen as an abstraction of the features of the architecture. The fact that the Tesla C870 only support 1.0 means that the programs we wish to run on these GPUs, can only use the features available in compute capability 1.0. Also, any optimizations must be based on this compute capability's specific requirements, e.g. memory access requirements. The architecture of the Tesla C870 is analyzed further in Appendix A, but we will give the most important details in Section 2.3.

Beside the Tesla cards, we have two developer computers with Nvidia graphics cards: Quadro FX880M, supporting compute capability 1.2 and a Quadro 140M, supporting compute capability 1.1, and we have a Radeon HD 2900XT from ATI with a theoretical performance of 475 gigaFLOPS with a memory bandwidth of  $106~\mathrm{GB/s}$  [23].

#### 2.2.1 Problems with Tesla C870

The two Tesla C870 cards are installed in a LENOVO ThinkStation D10 6427H6G with a Intel Xeon E5420 Quad core CPU, with a theoretical performance of 40 gigaFLOPS [28], and 4GB PC2-5300 RAM running Windows 7 enterprise 64-bit. Since the Tesla cards do not have any display output, and since they take up both of the Peripheral Component Interconnect Express (PCIe) X16 slots on the motherboard, an old ATI Mach64 VT2 Peripheral Component Interconnect (PCI) graphics card was initially installed in the system.

However, after trying different drivers and searching for similar problems on the Internet, we found the installation guide for the Tesla C1060, which states that the Tesla C1060 only works with other Nvidia graphics cards that are compatible with the same drivers as the Tesla C1060, when running Windows.[49] This was not mentioned in any of the official documentation for the Tesla C870 that we were able to find [47][48][46], but since the C1060 is a newer card compared to the C870, we assumed that a Nvidia graphics card is also required with the C870, and thus the root of our problems. After discovering this, we installed a Quadro FX 1400 card which used the same driver as the Tesla cards. This setup worked as intended, but the Quadro FX 1400 took up one of the two available PCIe 16x slots. The Tesla cards also uses PCIe 16x thus only one Tesla C870 could be used.

We therefore acquired a GeForce 8400GS with 512MB RAM that uses the PCIe X1 interface. The system however was unable to register this card when it was inserted. We assume this is due to the motherboard for some reason not supporting PCIe X1 graphics cards even after updating to the newest Basic Input Output System (BIOS) version. At the time of writing, the BIOS version is 2XKT31A. Also, the graphics card was tested in another system where it worked perfectly, i.e. it was not faulty.

Having concluded that the motherboard did not support PCIe x1 graphics cards, we found a GeForce 8400GS with 256MB RAM that uses the older PCI interface. Using this graphics card, we managed to get both Tesla C870 cards running using Windows.

In total this process took us about a month, with work on and off. A lot of time was spend on other tasks, as we were waiting for new hardware.

#### 2.3 G80 Architecture

Because Tesla C870 graphics cards implements the G80 architecture, this sections covers the most important details of the G80 architecture. The architecture is described in much more detail in Appendix A.

Nvidia is somewhat secretive about the details of their chips, therefore the following is based on information from people working for Nvidia found ind [35] and [54] supplemented with details found in [7] and [69].

#### 2.3.1 Overview

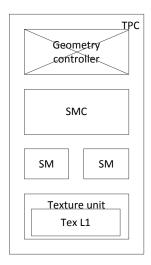

In Figure 2.3 we show the high level components of the G80 and how it interacts with the other components outside the GPU. At the top of the Figure 2.3 is the host system, with the host CPU and system memory that can communicate with each other through a bridge, this is usually the north bridge but might also be integrated in the CPU itself.

As shown on Figure 2.3, all communication such as issuing instructions or copying memory between the host system and the GPU, goes through the host interface, this is usually the systems PCIe bus. When GPGPU work is assigned the GPU the compute work distribution takes care of splitting the work in to smaller groups which are then assigned to one of the 8 Texture Processor Cluster (TPC), that performs the actual computations. The TPC usually requires access to the Dynamic Random Access Memory (DRAM) on the

graphics card, and can access it through the interconnection network on the chip, that connects each of the TPC to each of the 6 DRAM banks on the graphics card. Each of these banks has its own level 2 cache.

Figure 2.3: The architecture of the G80 GPU. The crossed out components are those that are of no interest to GPGPU. [35]

As shown in Figure 2.4, each TPC has a number of subcomponents, it has a single SM Controller (SMC) which controls two Streaming Multiprocessor (SM) and a texture unit. All communication between the SMs and the texture unit goes through the SMC, the SMC also decides which SM can access the texture unit at any given time. The texture unit is in charge of texture memory access and has a small read only L1 cache.

As shown in Figure 2.5 each SM consists of a number of subcomponents. It has an instruction cache and a multithreaded instruction unit that controls the eight Streaming Processor (SP) and two Special Function Unit (SFU). The SP executes simple floating point and integer operations and the SFU performs more advanced functions such as fast approximations of sin and cos. In addition to this, the SM has a read only constant cache and a read/write shared memory.

Figure 2.4: Components of the TPC on the G80 the component that are crossed out is of no interest to GPGPU. [35]

#### 2.3.2 Memory

The Tesla C870 features a number of different memory types, where some or located on-chip and other are located off-chip.

- 8192 32 bit registers per SM

- 16KB shared memory per SM

- 8KB constant cache per SM

- 8KB L1 texture cache per TPC

- 1536MB off chip DRAM

These memory types are described in more detail in Section 2.6.2 and in Section A.2.

Memory access to DRAM is much slower than memory access to registers, typically 400 to 800 clock cycles. To avoid stalls when performing computations that require DRAM access, the program should feature many thousands of threads such that it can switch between threads when one of them stalls. This means that the memory access latency is hidden away by having many threads.

As an example, consider a program which that performs one DRAM access per 10 instructions that are executed. Each performed instruction takes four clock cycles, and assuming that the DRAM latency is 600 clock cycles, we require 480 threads to hide this latency, since  $(480/32) \times 10 \times 4 = 600$ , where 32 is number of threads that goes into a warp. A warp is basically a collection of 32 threads that execute the same program on different data concurrently and is the smallest scheduable unit on the GPU. Warps are explained in more detail in Section A.1.

Figure 2.5: Components of the SM on the G80 [35]

#### 2.3.3 Summary

During this section we have analysed and described the G80 chip, e.g. which components it has, which memory types are available and how they are best accessed. This may useful when optimizing code for this architecture.

# 2.4 Algorithms Suited for GPGPU Execution

As described in Chapter 1, the primary usage of GPUs are the rendering of real time 3D graphics, such as in games, CAD applications, media players, etc. This means that GPGPU tasks have to exhibit many of the same characteristic as real time 3D graphics to obtain high performance. The aim of this section is to gain an overview of what these characteristics are, and how these characteristics influence the solutions used on the GPU compared to the solution used on the CPU.

Some of the things that characterize real time 3D graphics are:

• The computational requirements are very large. Each frame contains millions of pixels and each pixel requires hundreds of operations to calculate

its color. With multiple frames calculated each second real time 3D graphics requires many billions of calculations each second. [60]

- There are large opportunities for parallelism. Execution of programmable vertices and fragment/pixel shaders can easily be parallelized since they have no side effects. Thus, there are often millions of vertices and fragments in each frame, that can be processed in parallel. [60]

- There are opportunities for instruction stream sharing. Shaders are often executed on vertices and fragments that are close to each other. This locality leads to shaders often following the same control flow and thus are well suited for a SIMD style of execution. [16]

- Throughput is more important than latency. There is a large difference between the speed of the human visual system and the speed of modern processors. The human visual system, i.e. the processing of images in humans through eyes and the brain, works on a millisecond scale while processors work on a nanosecond scale, thus the time individual operations take is unimportant. Therefore the graphics pipeline is often quite deep, hundreds or thousands of cycles. [60]

- Well suited for read only caches that capture spatial locality. Graphics rendering involves few write operations, usual the only write operations performed by the graphics pipeline is outputting the final colors of the pixels. Instead, graphics involves a lot of read operations with a high level of spatial locality, e.g. a shader which applies texturing to one of the pixels of an object reads in data from on or more textures stored in memory, and there are a large chance that texturing neighboring pixels will involve accessing texture data close by. [16]

- Memory bandwidth is more important than memory latency. Graphics are well suited for wide memory busses since memory accesses often exhibit a high degree of spatial locality that allow to coalesce to fewer accesses. Data required by each stage in graphics pipeline are well suited for pre-fetching, thereby reducing the cost of high latency memory access. Additionally, the parallel nature of graphics rendering allows for latency hiding as was described in Section 2.1. [16]

#### 2.4.1 Comparison of Performance between GPUs and CPUs

Several types of problems have been solved with a substantial speed up using GPUs instead of CPUs, as we described in Section 1.1. This has lead to claims such as GPUs being superior to CPU in compute intensive applications. Scientific publications that support this claim are however hard to find, since not many publications deal with comparing CPU performance with GPU performance, other than comparing the theoretical performance or use a unoptimized single threaded version of the application on the CPU.

We have however found a publication [34] from 2010 by the Intel's Throughput Computing Lab and Architecture Group that deals with the issue of comparing the performance of several applications executing on a multi-core CPU and on a Nvidia GPU. [34] tries to void studies claiming 10x - 1000x speed up

of using GPUs for data intensive applications, and concludes based upon benchmarks done on a Core i7 960 CPU and a GTX280 GPU, that the GPU achieves a speed up of only 2.5x on average. This might be due to other researchers GPU performance analysis have neglected CPU optimizations and concentrated on the GPU implementation.

The GPU implementations achieve only 2.5x normalized speed up on average, even though the theoretical performance of the CPU is only 102.4 gigaFLOPS compared to the GPU's 933.1 gigaFLOPS. The 622 of the 933.1 gigaFLOPS are available when using a fused multiply-add operation, and by using a multiply operation on the special function unit. Thus, the GPU is theoretically 9 times faster than the CPU but it cannot be expected that all applications can achieve this speedup.

The benchmarks in [34] are carried out using 14 algorithms implemented and optimized for both platforms. Four of the algorithms are described below, with emphasis on how they perform on the GPU compared to the CPU, and why the performance speed ups are as it is. The four algorithms were chosen because they are known to us. The description of the algorithms and the implementation optimizations are based upon [34].

Radix Sort is a multi-pass algorithm that sorts one digit of the input each pass, from least to most significant digit. Due to each pass induces sorting, i.e. data rearrangement, several memory scatter and gather operations are carried out. The best implementation on the CPU is by utilizing the large cache, thus performing the scatter oriented rearrangements within this cache and thereby avoiding the costly memory operations into main memory.

Since the GPU has a much less cache memory, as described in Section 2.3.1, in the form of shared memory, the Radix sort is rewritten using a technique called split, such that it requires less memory for each pass but with the trade-off of using more scalar operations. Also, since GPU are best suited for read only operations that capture spacial-locality, Radix Sort is not well suited for the GPU because of its use of memory scatter operations, i.e. operations that write to seemingly unordered locations in memory.

This is also evident on the performed benchmark, where Radix Sort performs worse on the GPU than on the CPU, only a factor 0.76 of CPU performance is achieved.

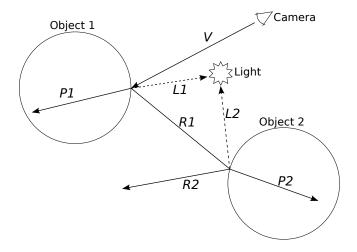

Volumetric Ray Casting is a technique used to visualize 3D datasets such as data gathered from medical CT scanners. In Volumetric Ray Casting, rays are traced through the 3D dataset which in the end generates a pixel based upon the opacity, color, etc. of the dataset.

Tracing several rays in a SIMD like pattern is challenging, since the rays may access incoherent memory, e.g. rays can be scattered in several different directions when tracing through the dataset. This reduces performance, since incoherent memory access on GPUs are generally more expensive compared to CPUs.

Volumetric Ray Casting is however a very compute intensive application, and the GPU implementation achieves a 1.8 speed up compared to the CPU.

**Fast Fourier Transform** is a standard signal processing algorithm used to convert signals from the time domain to the frequency domain, and vice versa. That is, instead of representing the signal as a signal amplitude change over time, it is instead represented as how much much signal lies within each frequency band over a range of frequencies.

Fast Fourier Transform (FFT) improves the Discrete Fourier Transform algorithm from  $O(n^2)$  to  $O(n*\log n)$  operations, which are mainly composed of multiply-adds floating point arithmetic operations. However, the data access patterns of FFT are non-trivial, making FFT hard to parallizable efficiently in a SIMD like pattern.

However, moving FFT from the CPU to the GPU yields a performance speed up of 3.0. This speed up can be explained by the extensive use of multiply-adds, which the GPU does well.

Collision Detection among convex objects, i.e. any two points within the object can be joined by a line segment that lies within the object, is commonly used in physics based simulators and computer games. A large fraction of the execution-time is spent on vertex computations, such as determining the closest vertex of a given position and direction, making collision detection on convex objects compute bound.

Also, data parallelism can be exploited, because the vertices and edges that make up an object are independent from other objects' vertices and edges, and can therefore be processed in parallel. This maps well to the SIMD architecture of the GPU.

In addition, texture memory can be used to speed up memory reads on the GPU. These optimizations make the GPU perform 14.9 times better than the equivalent CPU implementation and is thus a good fit for GPU execution.

#### 2.4.1.1 Discussion

Looking at the benchmark results from [34] we see that speed ups ranging from 0.5 to 14.9 were achieved on the GTX280 GPU compared to the Core i7-960 CPU, resulting in an average performance increase of a factor 2.5. This performance increase is smaller than what has previously been achieved with GPUs, and with similar benchmark specifications, and the following is a discussion on why this might be the case.

According to [34], one reason that some applications run much better on the CPU is due to the CPUs huge cache, compared to that of the GPU. Recall from Section 2.1, that the GPU relies on latency hiding by having hundreds of threads ready to be executed, however, this is not always possible depending on the application, e.g. due to synchronization constraints, or simply because the application requires too much register- or shared memory, thereby rendering it impossible to execute enough threads concurrently to achieve efficient latency hiding. The CPU does not suffer as much from this problem, since the CPU caches can in many instances hold large portions of the working set and the CPU program is normally not bound as much by register or memory constraints.

Looking at the results from this publication compared to other publications that deal with performance increase using GPUs, we only see one application that achieves above the 10x speed up mark, namely the collision detection algorithm with its 14.9 speed up, while other authors claim 100-1000x speed up.

[34] speculate that the reason for the speed up seen in prior papers, is mainly due to the CPU implementations being non-optimized versions, and in many cases single-threaded applications. Five references are made to publications that perform similar optimizations on CPU code, and the results are that the CPU and GPU implementations are much closer with regards to performance, thereby supporting this view. Also, some of the CPU implementations are executed on low-end CPUs, while their GPU counterparts are executed on high-end GPUs, thereby increasing the performance gap significantly.

Nvidia has given a rebuttal, in a blog post [50], to the results presented above claiming that the [34] is an attempt to promote the CPU, that the code that was run on the GPU was in unoptimized form, and that speed ups from 100x-300x have been seen by hundreds of developers. Also according to Nvidia, another contributing factor is that [34] compares the Core i7 960 (released October 09) with the GTX280 (released June 08), and Nvidia believes that using a newer GPU, with a newer and more advanced architecture, would yield much better performance.

The blog post also cites 10 publications which achieve 100x-300x speed up using GPUs. Looking at the publication claiming the highest speed up, 300x, on a Monte Carlo simulation [15] using a Nvidia 8800GT GPU compared to a Xeon Processor running 1.86GHz, we see that the GPU implementation uses single precision fast math, i.e. faster but less accurate single precision floating point operations, while the CPU implementation uses accurate double precision operations [15, p. 10]. Also, the CPU implementation is a C++ implementation called tMCimg, from 2004, which is apparently not being maintained [18]. In addition, the 300x speed up is only achieved when using non-atomic operations, which due to race conditions, can give incorrect results [15, p. 11]. When using atomic operations and normal floating point math, the speed up around 40x, which is significantly lower. Taking into account that double precision arithmetic on the CPU might be slower than single precision, e.g. due to the increased amount of memory usage, the 40x speed up might be reduced further to 20x speed up.

#### 2.4.1.2 Our Remarks

Based upon our analysis of the results presented in this section, we find that the 300x speed up is questionable at best, but we also agree that even a 10-40x speed up is significant. Also, newer GPUs such as the ones using the Fermi architecture are much better at performing GPGPU than their predecessors, e.g. due to cheaper unconcealed memory access, and especially at performing double precision arithmetics.

According to the information and discussion above, we should not expect that the GPU implementations of the ray tracer and Boids application are able to utilize the Tesla card to its maximum.

#### 2.5 Programming GPUs for General Purposes

With the move from the fixed-function pipeline, to a programmable one, programmers are able to write their own programs that are executed on the GPU in the form of shader programs.

When programming GPUs for general purposes using shader languages, such as the High Level Shader Language (HLSL) or the OpenGL Shading Language (GLSL), one has to transform the problem into the graphical domain before solving it, i.e. one has to represent the general problem as a rendering problem. Mapping steps frequently include [24, chap. 1]:

- 1. The copying of input data from the host to a portion of texture memory on the device.

- 2. Writing a pixel shader that computes some function based upon each pixel in the texture.

- 3. Setting up an off-screen buffer in which to store the result.

- 4. Invokes the pixel shader by rendering a 3D primitive to the off-screen buffer.

- 5. Copies the resulting pixels from the off-screen buffer back to the host.

Although these steps allows GPGPU programming, they do so in a graphical context. Instead, one may utilize higher level languages, such as CUDA, Open Computing Language (OpenCL) and BrookGPU, which completely hides the graphical context, and instead provides the programmer with an abstraction.

#### 2.5.1 Stream Processing

The following is based upon [29].

The Stream Processing paradigm advocates that input data is gathered into so called "Streams", in which each element can be operated on by one or more "kernels" in parallel. A kernel is a program that takes as input a stream and produces a stream as output with the computed result. A stream is a set of data.

This style of programming is frequently referred to as "gather, operate, and scatter", since source data is gathered into streams, then operated upon by a kernel containing several operations, and then scattered back into memory.

Stream Processing not only allows a kernel to operate on multiple elements in parallel, due to each element being independent of the other, but also allows efficient utilization of memory because of the producer-consumer nature of Stream Processing. The producers' input and output data can in many cases be coalesced, which in turn will improve performance since only one transaction is required.

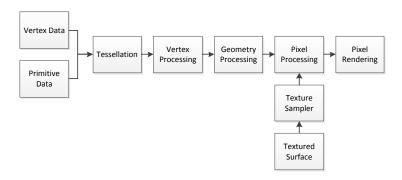

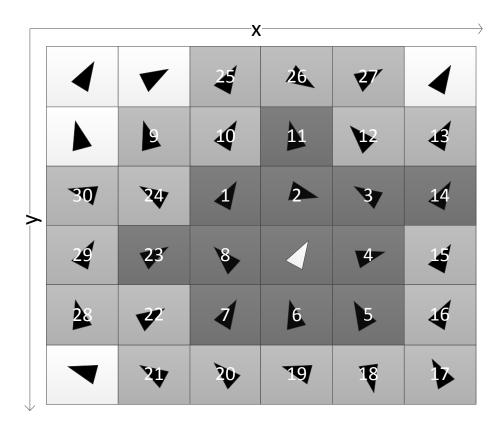

Larger granularity of pipelining can be performed when working on streams, by performing pipelining on the different stages rather than at instruction level. An example of this pipelining could be the Direct3D 9 graphics pipeline as shown in Figure 2.6.

The input to the graphics pipeline is a stream of Vertex Data and Primitive Data, this data is given to the first stage of the pipeline, which is the Tessellation stage where higher-order primitives are converted to vertices, thereby producing a new stream of vertices.

This stream of vertices are are then passed as input to the Vertex Processing stage which transforms the vertices, e.g. using a rotation matrix, thereby crating a new stream of rotated vertexes.

Figure 2.6: The Direct3D 9 Graphics Pipeline [38]

These are passed to the Geometry Processing stage, where they are rasterized thereby producing a stream of fragment; in DirectX terminology fragments are called pixels.

The fragment stream is then passed to the Pixel Processing stage where texturing is performed using the Texture Sampler to read the texture color for a given fragment.

The Pixel Processing stage produces a stream of fragments, which are passed to the Pixel Rendering stage where alpha blending and depth testing is performed, before the final stream of fragments are produced which can be shown on the screen.

# 2.6 GPU Languages

This section will introduce three GPGPU languages: BrookGPU, which is based upon the stream processing paradigm, CUDA, which is a GPGPU language and architecture developed by Nvidia, and OpenCL, which is an open GPGPU specification very similar to CUDA.

#### 2.6.1 BrookGPU

This section is based on [12].

BrookGPU is a programming language and runtime system that allows developers to utilize the GPU as a streaming co-processor, using the stream processing programming paradigm.

The Brook language extends ANSI C with data-parallel constructs such as *streams* and *kernels*, which allows the developer to define streams of data and write compute kernels, which can be transmitted to and carried out on the GPU.

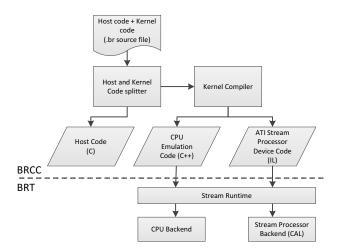

The BrookGPU architecture consist of The Brook Compiler (BRCC) and the Brook RunTime library (BRT). BRCC takes as input .br files that contain a mix of C and Brook code, and translates these with the help of BRT into C++ source files which are later compiled into an executable. The BRT is a class library that provides a generic and device independent interface for the BRCC, but with a device dependent implementation. [9]

Two well know implementations of BRT exists, one utilizes the Open Graphics Library (OpenGL) 1.3 or newer Application Programming Interface (API)

as backend, while the other utilizes the Direct3D 9 or newer API as backend. All GPUs that support at least one of the two APIs should be complaint with Brook and thus allow developers to utilize such GPUs for GPGPU purposes. [8]

#### 2.6.1.1 ATI's Brook+

Even though Brook supports GPGPU programming using Direct3D and OpenGL backends, it do so through a "graphical" context, although abstracted away by the runtime library, it utilize a graphics API that is optimized for drawing graphics and not optimized for GPGPU.

Brook+ is ATI's extension to the Brook language that allows developers to specifically write GPGPU code targeted ATI graphics cards; in Brook+, the BRT implementation targets ATI's Compute Abstraction Layer (CAL). CAL is a device driver for stream processors, specifically ATI GPUs, which allows stream programming closer to the GPU hardware, without using a graphics API. [4, sec. 1.1]

Figure 2.7: The architecture of ATI's Brook+, showing how Brook source code is compiled for use on CAL enabled devices. [4, p. 23]

As depicted on Figure 2.7, BRCC first splits the Brook program into the host code and the kernel code. The kernel code is compiled into either C++ code, which is later compiled to runs on the host, or into ATI's Intermediate Language (IL), which is later compiled to run on the device. Obviously, to harness the power of ATI GPUs, one would target IL code; CPU code is used primarily as a reference implementation to ease kernel debugging, since debugging tools for the GPU exists [4, sec. 2.2.4].

IL code is passed to the BRT, where it is later compiled by the CAL compiler for the specific GPU architecture. This allows IL code to run on many different ATI GPUs, as long as the instruction-set is supported by the CAL compiler. Also, IL code and device-specific code can be optimized by hand, thereby potentially improving kernel performance. [4, sec. 3.1.2.2]

#### 2.6.1.2 Example

Codeexample 2.1 shows a simple Brook program which sums two newly initialized matrices together.

```

1

#include < stdio.h>

3

//kernel definition, runs on the GPU

kernel void sum (float a<>, float b<>, out float c<>)

5

c \ = \ a{+}b \; ;

7

//host code, runs on the CPU

9

int main(int argc, char** argv)

11

\quad \textbf{int} \quad i \ , j \ ;

//2D stream declarations of 10x10:

float a < 10, 10 >;

13

float b<10,10>;

15

float c < 10, 10 >;

//2D arrays decelerations of 10x10

float input_a[10][10];

17

float input b [10][10];

float output_c[10][10];

//initialize the 2D arrays

19

21

for (i=0; i < 10; i++)

for (j=0; j < 10; j++)

23

\begin{array}{lll} input\_a \, [\, i\, ] \, [\, j\, ] &=& (\, \textbf{float} \,) \, i \, ; \\ input\_b \, [\, i\, ] \, [\, j\, ] &=& (\, \textbf{float} \,) \, j \, ; \end{array}

25

27

29

//copy the 2D arrays to the GPU

streamRead(a,input_a);

31

streamRead(b,input b);

//call the kernel

33

sum(a,b,c);

//get the result from the GPU

35

streamWrite(c,output c);

```

Codeexample 2.1: Sum.br: Sums together two matrices, a and b, and stores the result in c. [4]

The sum kernel takes as input, two 2D streams and returns, as output, a 2D stream containing the matrix summation. The operations are done in parallel on the GPU.

The main function allocates three 2D streams and three 2D arrays that make up the matrices. It then initializes the matrices, copies them to the GPU using the streams as references and schedules the sum kernel to the GPU.

Lastly, the result of the computation is copied from the GPU to the host program, by copying the content of the output stream to the output\_c array on the host.

#### 2.6.2 CUDA

This section is based on [54].

CUDA is general purpose parallel computing architecture developed by Nvidia to provides a unified way of performing GPGPU on Nvidia GPUs. As such CUDA supports a number of different languages and APIs those officially supported by Nvidia are: CUDA C, OpenCL, DirectCompute and CUDA Fortran. [55, sec. 1.2]. CUDA C and CUDA Fortran are Nvidia's own languages that provides a small number of extensions to the C and Fortran languages, respectively, that enables programmers to use the GPU.

In this section we will focus on CUDA C since C appears to be a much more popular language than Fortran [32]. CUDA comes in a number of different compute capabilities that describes the different features supported in CUDA. In the following, we will assume a compute capability of 1.0, as this is supported by the Tesla cards at our disposal as described in Section 2.2. A further description of the different compute capabilities is given in Section 2.6.2.4.

#### 2.6.2.1 Architecture

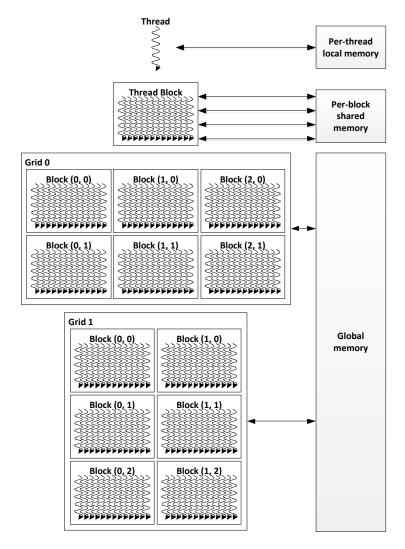

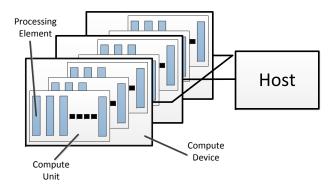

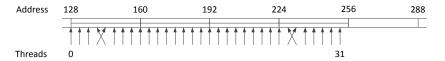

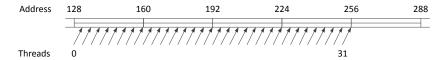

CUDA C enables developers to write kernels that run on the GPU. In CUDA C, a kernel is executed by a number of concurrent threads. These threads are organized into a one-dimensional, two-dimensional, or three-dimensional thread blocks. As stated in Section A.1, a thread block is equivalent to Cooperative Thread Array (CAT)s in the G80 architecture. Thread blocks are further organized in a grid of thread blocks, which can be one-dimensional or two-dimensional [55, sec. 2.2].

As a consequence of this, the programmer first need to define the size of the thread blocks and the size of the grid when lunching a kernel on the GPU. Each thread executes the same kernel, which defines the work to be done. From the kernel, each thread can be identified by its thread- and block id, allowing it to work on different pieces of data based upon its id. Kernels can only access data stored in memory on the graphics card, which means that the programmer needs to manage all memory on the host and device, and data needs to be copied between the two using host functions provided by CUDA.

If multiple CUDA capable GPUs are present in the system, these can all be utilized. This however requires that the programmer writes an explicit multi GPU capable application, i.e. an application that distributes work between more devices and not only one. CUDA also imposes that each device gets its own CPU thread; this must also be handled by the programmer. [55, sec. 3.2.3]

#### 2.6.2.2 Memory

As shown in Figure 2.8, there are a number of different read and write memories in CUDA C that are shared on the thread, thread block and grid level. These memories have different performance characteristics and must in most cases be managed by the programmer.

**Local** Each thread can use up to 16KB of memory, called local memory, that is only accessible within the given thread. This memory is relatively slow as it is stored in DRAM on the graphics card and performs as described in Section A.2, i.e. global memory access have latency of 400-600 cycles. Use of local memory is manage by the CUDA C compiler and is primary used for large structures

that would use to much register space, e.g. arrays containing many elements, or if kernel consumes more registers than available on the GPU.

**Shared** Threads in a thread block have access to 16KB of memory, called shared memory, which is shared between the threads in the block. Shared memory is fast on chip memory as described in Section A.2. Since shared memory is fast, it is often used by programmers as a cache to increase performance when working with data stored in slower memory.

Global All threads both in the same grid and between grids have access to a large shared memory space, called global memory, that resides in DRAM on the graphics card. The size of the global memory is limited by the amount of DRAM on the graphics card. Performance of global memory is affected by the access pattern of programs, e.g. un-coalesced memory access results in much worse performance. This is described in much more detail Section A.2.

**Read only** In addition to these types of memories, there are also two types of read only memory areas that are shared between all threads.

The first of these is constant memory, which is limited to a size of 64K. Constant memory is optimized for broadcasting a memory read to multiple threads and is cached on chip. The performance is described further in Section A.2.

The second type of read only memory is called texture memory and is cached on chip and optimized for 2D spatial locality [54, sec. 5.3.2.5]. A kernel can at most use 128 texture memories, in addition to this limitation, texture memory is also limited in the maximum number of elements depending on whether it is a 1D, 2D or 3D texture.

A 1D texture can be at most 8192 or  $2^{27}$  elements wide, depending on how it is allocated. A 2D texture can contain  $65536 \times 32768$  elements and 3D texture can contain  $2048 \times 2048 \times 2048$  elements. The performance of texture memory is described in greater detail in Section A.2.

#### 2.6.2.3 Example

Codeexample 2.2 shows an example of CUDA code, which adds two vectors of 1000000 elements. Line 1 to 6 is the kernel that is to run on the GPU. All kernels in CUDA C must be denoted by the <code>\_\_global\_\_</code> key word, but otherwise look like a normal C function.

Line 3, the element of the vectors a given thread is to work on is calculated based on the thread id, block ids and block size.

Line 4 and 5, it is checked if the element to work on is within the size of the vectors, if it is, the two elements are added together.

Line 7 to 38 denotes the code which is executed on the host. Line 9 indicates the number of elements in the vectors. Line 10 to 13 allocates host memory for the vectors. Line 14 to 18 fills the vectors with values. Line 19 to 24 allocates device memory for the two input vectors and the output vector on the graphics card. Line 25 and 26 copies the input vectors from the host to the device. Line 27 and 28 calculates the number of thread blocks required in a grid with a given number of threads in a thread block, in this case 256, to process all elements in the vectors. Line 29 launches the kernel with the previously calculated number

Figure 2.8: Shows the memory access model on CUDA. [54]

of blocks per grid and 256 threads per block. Line 30 copy the result of running the kernel from device memory back to host memory. Line 31 to 36 frees all the allocated memory both on device and host.

```

float* host_C = (float*) malloc(size);

14

for(int i = 0; i < elements; i++)

host A[i] = i;

16

host B[i] = i * 2;

18

float * device A;

\verb|cudaMalloc(&device_A|, size)|;

20

float * device B;

22

cudaMalloc(&device B, size);

float * device C;

24

cudaMalloc(&device_C , size);

26

int threadsPerBlock = 256;

int blocksPerGrid = (size + threadsPerBlock - 1) threadsPerBlock;

\verb|addVector| << \verb|blocksPerGrid||, threadsPerBlock|| >> (\texttt|device\_A|, \texttt|device\_B|)|,

device C, elements);

30

cudaFree(device B);

32

cudaFree(device_C);

34

free (host_A);

free (host B);

36

free (host_C);

return 0;

38

```

Codeexample 2.2: Example code, which sums two vectors together. This is a modified version of the example found on page 22 in [54]

#### 2.6.2.4 Compute Capability

The compute capability of Nvidia GPUs consists of a major and a minor revision number. The major revision number denotes the overall core architecture, while the minor revision number denotes an incremental improvement on the overall core architecture, e.g. such as the addition of a new feature. Compatibility of GPGPU programs written targeting different compute capabilities are guaranteed on the binary level, but only from minor revision number to the next. Compatibility is not guaranteed between major revisions, i.e. compatibility between 1.0 and 1.3 is guaranteed, but 1.3 to 2.0 is not.

Parallel Thread Execution (PTX) code is an intermediate assembly language used by CUDA. At compile time, the CUDA application is compiled to PTX code, which is later compiled at runtime to native code on the device. PTX allows CUDA programs to use higher compute compatibility, than was available when the CUDA program was written, and can therefore insure forward compatibility of CUDA programs. Thus, PTX circumvents the restriction of binary compatibility between major revisions thus allowing better cross-platform support. [55, sec. 3.1.4]

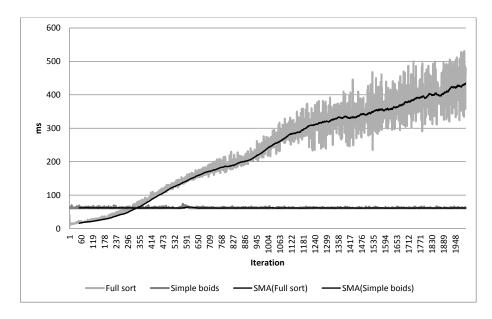

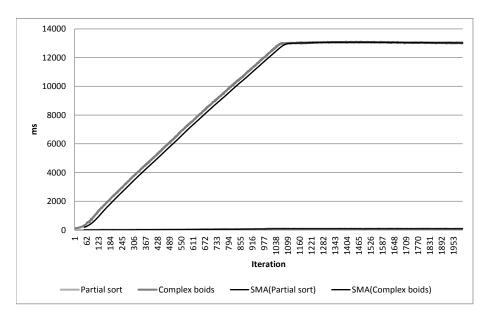

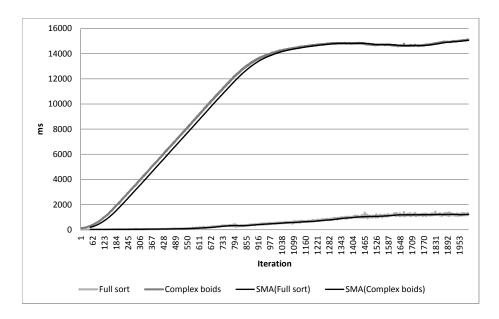

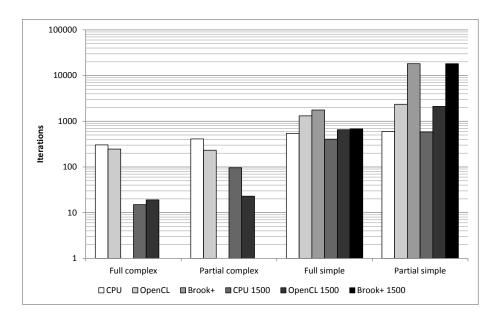

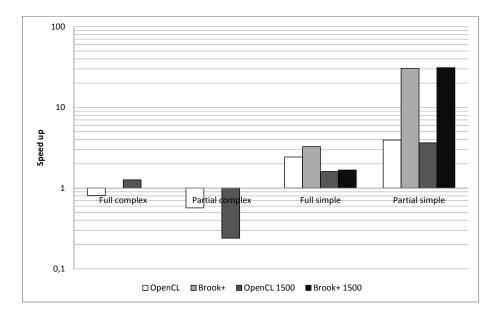

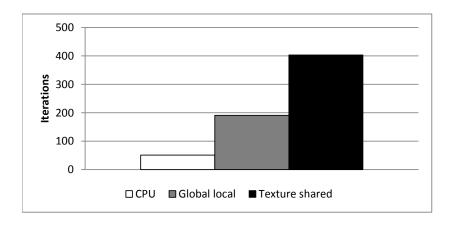

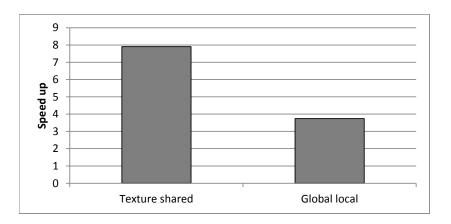

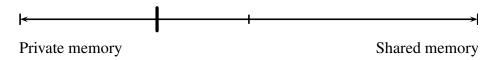

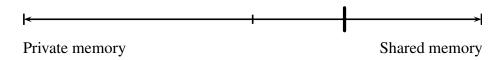

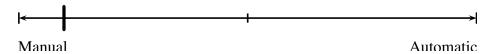

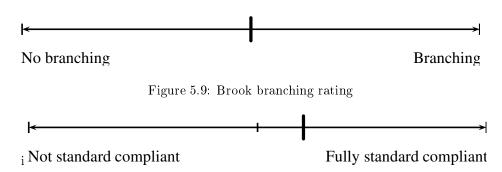

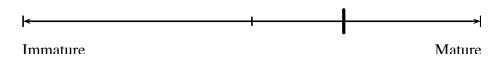

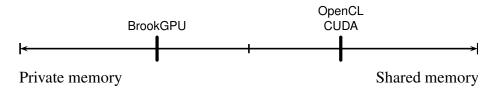

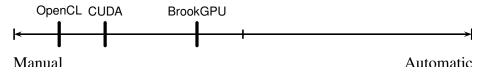

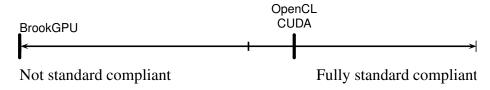

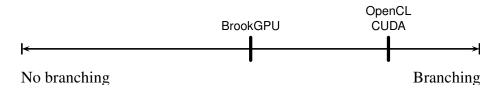

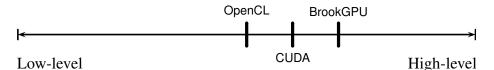

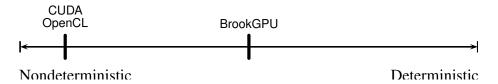

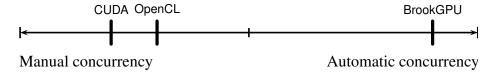

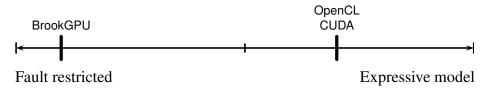

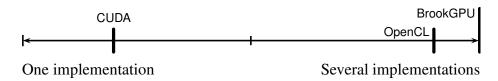

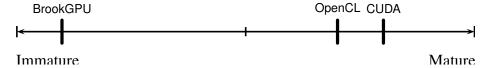

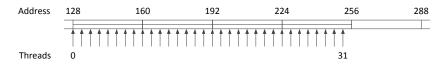

The following a short list of features introduced after compute capability 1.0, which is the compute capability that the Tesla cards support. For a more in depth look, see [55].